(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для контроля кодовых жгутов ПЗУ | 1985 |

|

SU1336120A1 |

| Устройство для сопряжения процессора с памятью | 1990 |

|

SU1798788A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано для контроля блоков постоянной памяти (ПЗУ) и кодовых жгутов. Целью изобретения является повышение достоверности контроля. Устройство

тг

00

СО 00

14)

Ьодержит блок 1 элементов коммутации, |блок 2 управления, состоящий из муль- |гивибратора 3, делителя 4 частоты, формирователя 5 тактовых импульсов распределителя 6 тактовых импуль- ЬОБ, Устройство содержит также блок |7 ввода контрольных сигналов, напри- с перфокарт, регистр 8 адреса, :зторой 9 и первый 17 блоки сравнения, ()0рмирова тель 10 адресных сигналов, (юрмирователь 11 управляющих сигналов, блок 12 элементов И-ИЛИ, счетчик 13, дешифратор 14, коммутатор 15, ()лок 16 контроля контактирования ко- довых жгутовр формирователь 18 информационных сигналов, элемент задержки

9, блок 20 индуктивных датчиков, на- фимер катушки индуктивности на штыре иых сердечниках, первичной обмоткой каждой из которых является провод 1|:одового жгута, генератор 21 тока.

Изобретение относится к вычисли- т|ельной технике и может быть исполь- з|овано для контроля блоков постоянной п|амяти (ПЗУ) и кодовых жгутов и является гсовершенствованием изобретения по IIBT.CB, IS 1191944.

i Цель изобрете.ния - повышение досто : ерности контроля .На фиг, 1 представлена функциональ ifiaK схема предложенного устройства Йа .фиг. 2 - функциональная схема бло- )jca анализа полноты контроля; на фиг. 3 - функциональная схема наибо- .jiee предпочтительного варианта вьшол- :|1ения распределителя тактовых импуль- ||;ов блока управления.

Устройство содержит (фиг.1) блок It элементов коммутации, блок 2 управ- ;|1ения, состоящий из мультивибратора :, делителя 4 частоты, формирователя 5 тактовых импульсов и распределите- ;|1Я 6 тактовых импульсов.

Устройство содержит также блок 7 контрольных сигналов, регистр $ адреса, второй 9 блок сравнения, формирователь 10 адресных сигналов, формирователь 11 управляющих сигна- ;liOB, блок 12 элементов И-ИЛИ, счетчик

блок 22 -регистрации ошибок, блок 23 памяти адресов, блок 24 анализа полноты контроля, счетчик 25 числа неопрошенных ячеек памяти и блок 26 элементов И, Повьшгегше достоверности контроля достигается за счет того, что в блок 23 записьшается единица при обращении к контролируемому блоку памяти по адресу, установленному на выходе счетчика 13, и нуль - в случае, если по этому адресу объект контроля не контролируется, К концу контроля выполняется опрос блока 23 Адреса, по которым в блоке 23 записаны нули, регистрируются блоком 22, а число их фиксируется счетчи1сом 25, Сигнал конца контроля выдается блоком 24 анализа полноты контроля только в случае записи единичной информации во всех ячейках блока 23 памяти, 1 з.п,ф-лы, 3 ило

0 5

0

5

13, дешифратор 14, коммутатор 15, блок 16 контроля контактирования кодовых жгутов, первый 17 блок сравнения, формирователь 18 информационных сигналов, элемент 19 задержки, блок

20индуктивных датчиков, генератор

21тока, блок 22 регистрации ошибок, блок 23 памяти адресов, блок 24 анализа полноты контроля,.счетчик 25 числа неопрошенных ячеек памяти и блок 26 элементов И,

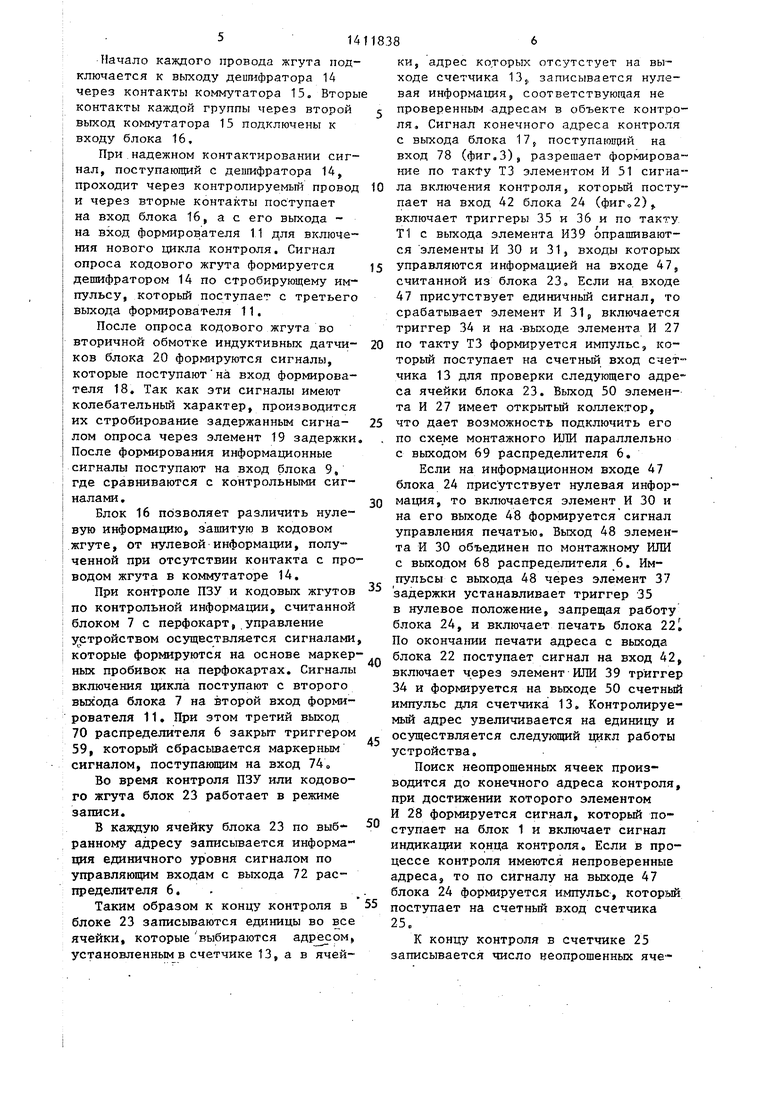

Блок 24 анализа полноты контроля содержит (фиг.2) с первого по пятый элементы И 27 - 31, первый 32 и второй 33 элементы НЕ, с первого по третий триггеры 34-36, первый 37 и второй 38 элементы задержки, первый 39 и второй 40 элементы ИЛИ, Первый 41 и второй 42 входы пуска, первый 43 и второй 44 входы разблокировки, вход 45 синхронизации, информационный вход 46 и с первого по четвертый 47-50 выходы блока 24 анализа полноты контроля.

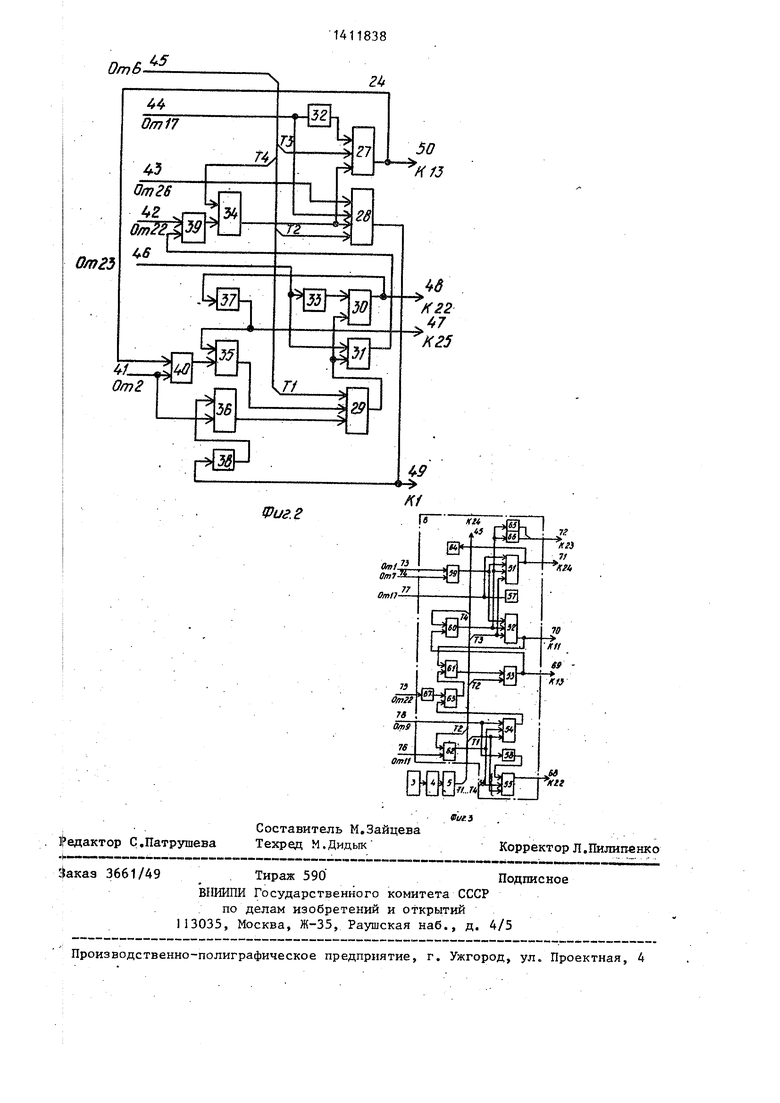

Распределитель 6 тактовых импульсов содержит (фиг.З) элементы И 51- 55, входы 56 элемента И 55, элементы и 58. триггеры 59 - 62, эле- мент ИЛИ 63, элемент 64 задержки, эле1« енты 65-67 согласования, выходы 68-72 к входы 73-78 распределителя 6 тактовых импульсов. На фиг.1 обозна- чены также информационные входы 79 и выходы 80 устройства.

Блок 7 ввода контрольных сигналов может быть вьтолнен, например из УПК-М1, позволяющего считывать контрольную информадаю с перфокарты. В качестве блока 22 регистрации ошибок может быть применено, например, М11У16-3 (малогабаритное печатающее устройство).

Блок 20 индуктивных датчиков может быть выполнен, например, в виде катушек индуктивности, представляющих собой вторичную обмотку на, штыревых сердечниках, первичную обмотку кото- рых представляет провод проверяемого кодового жгута.

Формирователь 18 информационных сигналов выполнен из усилителей, число которых равно разрядности контро- лируемого кодового жгута, подключенных входами к вторичным обмоткам индук-Гйвных датчиков, которые формируют импульсные сигналы на основе протекания импульсного тока в проводе проверяе-30 По такту ТЗ на выходе элемента И .52

мого кодового жгута.

Устройство работает следующим образом.

Устройство обеспечивает проверку функционально законченных блоков постоянной памяти и пассивных узлов памяти - кодовых жгутов,

В первом случае контролируемые блоки подключаются к входам 79 и выходам 80 устройства, а при проверке кодовых жгутов последний укладьшает- ся на сердечншси блока 20 (фиг,1).

Проверка осуществляется сравнением в блоке 9 чисел в двоичном коде которые считаны с объекта контроля, с контрольными кодами, носителями которых может быть перфокарта или эталонный блок памяти.

При проверке объекта контроля по эталонному блоку последний подключается к входам 79 и выходам 80 аналогично контролируемому б локу.

Временная диаграмма работы эталонного и контролируемого блоков строится формирователем 11 на основе тактовых импульсов Т1 - Т4, смещенных один относительно другого на длительность одного тактового импульса, формируемых формирователем 5

Прн контроле ПЗУ по эталонному блоку устройство работает следующим образом. Пусковой импульс с пятого выхода блока 1 по входу 73 в распределителе 6 (фиг.З) включает триггер 59. По пятому входу формирователя 11 включается временная диаграмма контроля.

В конце цикла формируется сигнал, который с-выхода блока 11 поступает на вход 76, включает триггер 62, в результате импульсом Т1 опрашиваются элементы И 54 и 55. При равенстве кодов в блоке 9 формируется единичный сигнал, при неравенстве - нулевой, который через элемент НЕ 33 поступает на вход элемента И55. Единичный сигнал по такту Т1 формирует импульс на выходе элемента И 54, а нулевой - на выходе элемента И 55,

Импульс с выхода элемента И 54 через элемент ИЛИ 63 включает триггер 61 для разрешения формирования счетного импульса для счетчика 13 по такту Т2 элементом И 53, При этом код. адреса в счетчике 13 увеличивается.на единицу и выбирает следующую контролируемую ячейку ПЗУ (не показан),

5

формируется импульс, къторый поступает на .третий вход формирователя 11, формирует сигналы временной диаграммы и начинает следующий, цикл контроля.

Количество циклов контроля задается с блока 1 посылкой в регистр 8 кода, который соответствует адресу последней контролируемой ячейки ПЗУ, 0 При достижении конечного адреса блок 17 вырабатьгеает сигнал, который с- его выхода поступает на .вход 77 рас-; : пределителя 6 и запрещает формирова- . кие сигнала на выходе элемента И.52 для пуска следующего цикла,- При не совпадении кодов в блоке 9 сигнал неравенства фop lиpyeт по такту Т1 элементом И 55 импульс обращения к печати, который с выхода 68 поступает на вход блока 22, При этом фиксируется адрес неисправности и по окончании операции печати формируется импульс, которьй поступает на вход 75 распределителя 6, включается триггер 61, формируется на выходе 70 импульс пуска временной диаграммы следующего цикла и импульс счета на выходе 69.

Проверка кодового жгута осуществляется аналогично проверке ПЗУ,

5

0

5

51411838

Начало каждого провода жгута под20 п

ключается к выходу деимфратора 14 через контакты коммутатора 15. Вторы контакты каждой группы через второй выход коммутатора 15 подключены к входу блока 16,

При надежном контактировании си1- нал, поступающий с дешифратора 14, проходит через контролируемый провод и через вторые контакты поступает на вход блока 16, а с его выхода на вход формиров,ателя 11 для включения нового цикла контроля. Сигнал опроса кодового жгута формируется дешифратором 14 по стробирующему им пульсу, который поступает с третьего выхода формирователя 11.

После опроса кодового жгута во вторичной обмотке индуктивных датчиков блока 20 формируются сигналы, которые поступают на вход формирователя 18. Так как эти сигналы имеют колебательный характер, производится их стробирование задержанным сигналом опроса через элемент 19 задержки После формирования информационные сигналы поступают на вход блока 9, где сравниваются с контрольными сигналами ,

Блок 16 пбзволяет различить нулевую информацию, зашитую в кодовом жгуте, от нулевой информации, полученной при отсутствии контакта с проводом жгута в коммутаторе 14.

При контроле ПЗУ и кодовых жгутов по контрольной информации, считанной блоком 7 с перфокарт, управление устройством осуществляется сигналами которые формируются на основе маркерных пробивок на перфокартах. Сигналы включения цикла поступают с второго выхода блока 7 на второй вход формирователя 11. При этом третий выход 70 распределителя 6 закрыт триггером 59, который сбрасьшается маркерным сигналом, поступающим на вход 74.

Во время контроля ПЗУ или кодового жгута блок 23 работает в режиме записи.

В каждую ячейку блока 23 по выбранному адресу записывается информация единичного уровня сигналом по управляющим входам с выхода 72 распределителя 6. .

Таким образом к концу контроля в блоке 23 записываются единицы во все ячейки, которые выбираются , установленным в счетчике 13, а в ячей0

5

5

0

ки, адрес которых отсутстует на выходе счетчика 13j, записывается нулевая информация, соответствующая не проверенным адресам в объекте контроля. Сигнал конечного адреса контроля с выхода блока 17, поступающий на вход 78 (фиг.З), разрешает формирование по такту ТЗ элементом И 51 сигнала включения контроля, которьш поступает на вход 42 блока 24 (фиГо2) включает триггеры 35 и 36 и по такгу Т1 с выхода элемента ИЗ9 опрашиваются элементы И 30 и 31, входы которых управляются информацией на входе 47, считанной из блока 23, Если на входе 47 присутствует единичный сигнал, то срабатывает элемент И 31j включается триггер 34 и на -выходе элемента И 27 0 по такту ТЗ формируется импульс, который поступает на счетный вход счетчика 13 для проверки следующего адреса ячейки блока 23. Выход 50 элемента И 27 имеет открытый коллектор, что дает возможность подключить его по монтажного ШШ параллельно с выходом 69 распределителя 6.

Если на информационном входе 47 блока 24 присутствует нулевая информация, то включается элемент И 30 и на его выходе 48 формируется сигнал управления печатью. Выход 48 элемента И 30 объединен по монтажному ИЛИ с выходом 68 распределителя 6. Импульсы с выхода 48 через элемент 37 задержки устанавливает триггер 35 в нулевое положение, запрещая работу блока 24, и включает печать блока 22L По окончагши печати адреса с выхода блока 22 поступает сигнал на вход 42, включает через элемент ИЛИ 39 триггер 34 и формируется на выходе 50 счетный импульс для счетчика 13. Контролируе- мьй адрес увеличивается на единицу и осуществляется следующий цикл работы устройства.

Поиск неопрошенных ячеек производится до конечного адреса контроля, при достижении которого элементом И 28 формируется сигнал, который поступает на блок 1 и включает сигнал индикации конца контроля. Если в процессе контроля имеются непроверенные адреса, то по сигналу на выходе 47 блока 24 формируется импульс, который поступает на счетный вход счетчика 25.

К концу контроля в счетчике 25 записывается число неопрошенных яче5

0

5

0

5

ек контролируемой памяти. Блок элементов И 26 осуществляет контроль,состояний выходов счетчика 25 по единичным уровням. При наличии в счетчике 25 информации, отличной от нулевой, блок элементов И 26 по выходу закрыт и сигнал индикации конца контроля не сформирован, а адреса непроверенных ячеек объекта контроля зарегистрируются блоком 22, J

8

10

Формула изобретения

ты задержки, первый и второй- элеме(г- ты или, причем выход первого элемента ИЛИ подключен к входу установки в 1 первого триггера, выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом установки в 1 вто рого тригг ера, выход которого подключен к первому входу третьего элемента И, выход которого соединен с первыми входами четвертого и пятого 1. Устройство для контроля ПОСТОЯНЧ5 элементов И, выход второго элемента

И подключен к входу первого элемента задержки, выход которого соединен с входом сброса третьего триггера, вы- ход которого подключен к втором вхо20 ДУ третьего элемента И, второй вход первого элемента И соединен с выходом первого элемента НЕ, выход второго элемента НЕ подключен к второму входу четвертого элемента И, выход

25 которого подключен к входу второго элемента задержки, выход которого подключен к входу установки в О второго триггера, первый вход .перво-. го элемента ИЛИ соединен с выходом

ной памяти по авт.ев, № 1191944, о т- ли 1ающееся тем, что, с целью повьшения достоверности контроля, в устройство введены блок памяти адресов, блок элементов И, счетчик числа неопрошенньпс ячеек памяти и блок анализа полноты контроля, информационный вход и первый выход которого подключены соответственно к выходу блока памяти адресов и к счетному входу счетчика числа неопрошенных ячеек памяти, выходы которого соединены с входами блока элементов И, выход которого,подключен к первому входу разблокировки блока анализа полно- 30 пятого элемента И, второй вход которого и вход второго элемента НЕ -объединены и являются информационным входом блока, второй вход второго элемента И является первымвходом разблокировки блока, третьи входы с первого по третий элементов И и вход установки в О первого триггера объе динены и являются входом синхронизации блока, вход первого элемента НЕ и четвертый вход второго элемента И объединены и являются вторым входом разблокировки блока, вход установки в 1 и второй вход второго элемента ИЛИ объединены и являются первым входом пуска блока, вторым входом пуска которого является второй вход первого элемента ИЛИ, выход второго элемента задержки и выход четвертого ,элемента И являются соответственно

ты контроля, вход синхронизации и первый вход пуска которого соединены соответственно с четвертым и шестым выходами блока управления, второй вход и выход блока регистрации ошибок подключены соответственно к второму выходу и к второму входу пуска блока анализа полноты контроля, третий и четвертый выходы которого соединены соответственно с входом блока элементов коммутации и со счетным входом счетчика, выходы которого подключены к адресным входам блока памяти адресов, вход записи которого соединен с пятым выходом блока управления, второй вход разблокировки блока анализа полноты контроля подключен к выходу первого блока сравнения, 2, Устройство по По 1, о т л и 35

40

45

чающееся тем, что блок анали- первым и вторым выходами блока, выход

50

за полноты контроля содерясит с первого по третий триггеры, с первого по пятый элементы И, первый и второй элементы НЕ, первый и второй элемен8

10

Ч5

30

35

30

40

30

45

первым и вторым выходами блока, выход

50

второго элемента И является третьим выходом блока, четвертым выходом рого является выход первого элемента И.i

ОтВ

Фиг. 2

Oail OmrS.

ОтП

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-05—Подача