(5) ИНТЕГРАЛЬНАЯ ЛОГИЧЕСКАЯ СХЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема | 1979 |

|

SU860314A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ—НЕ» и «И-ИЛИ» | 1970 |

|

SU260680A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Устройство преобразования однофазового логического сигнала в парафазный ток | 1976 |

|

SU570201A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Эмиттерно-связанный элемент | 1988 |

|

SU1629985A1 |

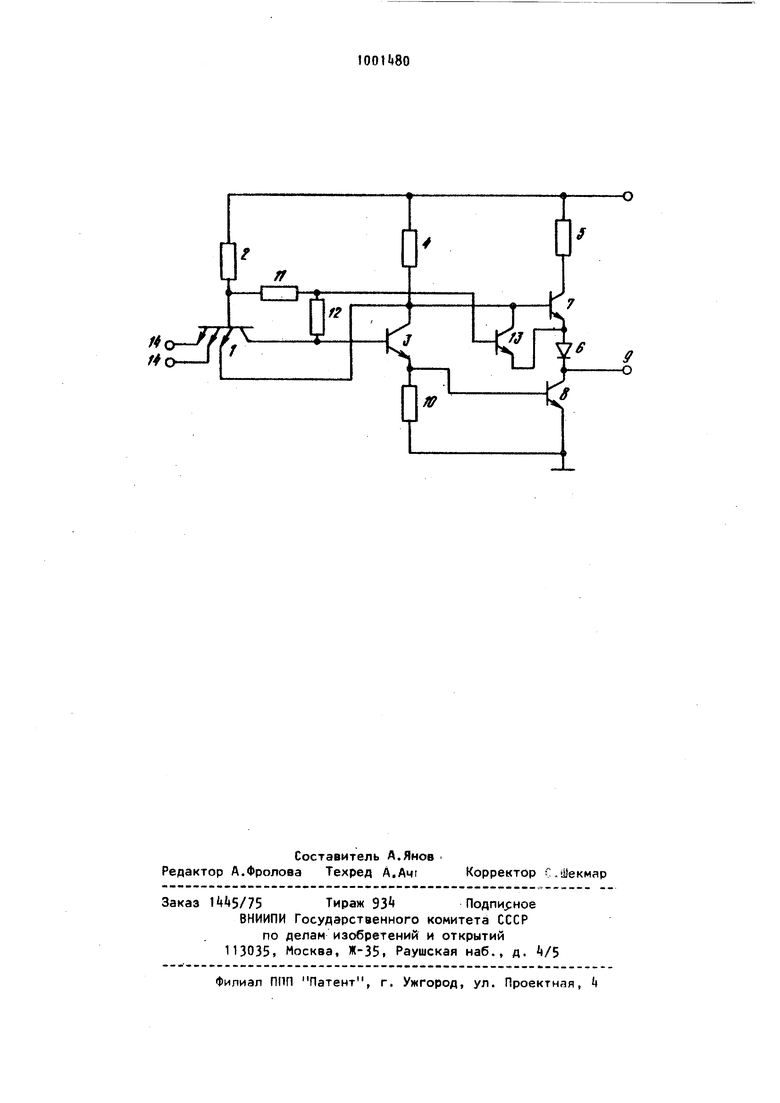

Изобретение относится к микроэлек ронике и может быть использовано в в числительной технике, в системах дис ретной автоматики. Известен ТТЛ элемент, содержащий входной многоэмиттерный транзистор, подсоединенный коллектором к базе транзистора парафазного каскада, кол лектор которого, в .свою очередь, соединен с базой первого транзистора выходного каскада, выполненного на двух последовательно включенных чере диод транзисторах, а эмиттер подключен к базе второго транзистора выходного каскада 1 Недостатком известного элемента является необходимость выполнения технологической операции легирования золотом для обеспечения достаточного быстродействия схемы. Известно также устройство, содержащее входной многоэмиттерный траняистор, подсоединенный коллектором к базе первого транзистора парафазного каскада, коллектор которого соединен с базой первого транзистора выходного каскада, выполненного на двух последовательно включенных через диод транзисторах. Эмиттер первого транзистора парафазного каскада подключен к базе второго транзистора выходного каскада через резистор и непосредственно - к базе второго транзистора парафазного каскада, коллектор и эмиттер которого соединены соответственно с коллектором первого транзистора парафазного каскада и коллектором второго транзистора выходного каскада, эмиттером соединенного с общей шиной . Известное устройство предполагает повышение быстродействия за счет ограничения насыщения выходного транзистора, однако не исключает потери в быстродействии и относительный рост потребляемой мощности в связи с инверсным включением входного многоэмиттерного транзистора при логической 1 на входеи наличием двух насыщенных транзисторов в парафазном каскаде. Указанные недостатки схемы делают целесообразным ее применение лишь в условиях узких температурных диапазонов. Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности. Поставленная цель достигается тем, что в устройство, содержащее входной многоэмиттерный транзистор, база которого через резистор соединена с шиной питания коллектор - с базой первого транзистора парафазного каскада, коллектор которого соединен с коллектором второго транзистора парафазного каскада и базой первого транзистора выходного каскада, коллектор которого 20 через резистор соединен с шиной питания , эмиттер через диод - с коллектором второго транзистора выходного кас када, эмиттер которюго соединен с об|щей шиной, база - с эмиттером первого транзистора парафазного каскада и через резистор с общей шиной, коллектор первого транзистора парафазного каскада через резистор соединен с шиной питания, введен резистивный делитель, включенный между базой и коллектором входного многоэмиттерного транзистора, средняя точка которого подключена к базе второго транзистора парафазного каскада, эмиттер которого подключен к эмиттеру первого транзистора выходного каскада, база которого соединена с одним из эмиттеров входного многоэмиттерного транзистора. На чертеже изображена схема предлагаемого устройства. Устройство содержит входной многоэмиттерный транзистор 1, подключенный базой через резистор 2 к шине питания а коллекторам - к базе первого транзистора 3 парафазного каскада, коллектор которого через резистор 4 подключен также к шине питания. Выходной каскад схемы содержит резистор 5 и два последовательно вклю ченных через диод 6 транзистора 7 и 8 При этом коллектор транзистора 7 подключен к шине питания через резистор 5, база транзистора 7 подключена к коллектору транзистора 3, эмиттер транзистора 7 подключен к аноду диода 6. Коллектор транзистора 8 подклю Чен к катоду диода 6 и выходу 9, база транзистора 8 подключена к резистору 10, второй вывод которого подключен к общей шине. Между базой и коллектором входного многоэмиттерного транзистора 1 включен резистивный делитель, состоящий из последовательно включенных резисторов 11.и 12, к общей точке которых подключена база транзистора 13 парафазного каскада, коллектор и эмиттер которого соответственно подключены к коллектору транзистора 3 и аноду диода 6. Все эмиттеры входного многоэмиттерного транзистора 1, кроме одногодополнительного, подключены к входам 14 схемы, дополнительный эмиттер транзистора 1 связан с коллекторами транзисторов 3 и 13 парафазного каскада. Предлагаемое устройство работает следующим образом. При подаче на входы 14 низкого уровня напряжения логического О транзистор 3 парафазного каскада будет закрыт. При этом будет также закрыт транзистор 8, в базу которого не втекает ток. На выходе 9 микросхемы создается высокий уровень напряжения, а входной транзистор благодаря действию обратной связи с базы на коллектор через резисторы 11 и 12 ограниченно насьпдается. . о При подаче на входы 14 высокого уровня логической 1 транзистор 3 открывается и через него течет ток в базу транзистора 8 и в резистор 10. При этом в начальный момент, когда транзистор 8 еще не включился и на его коллекторе имеется высокий уро,вень напряжения, в базу транзистора 8 задается избыточный ток, обеспечивающий быстрое его включение, тогда как через транзистор 13 ток протекать не может, поскольку напряжение на его базе равно . 1%эв эг прямое напряжение на переходах база - эмиттер соответственно транзисторов 8 и 3; Up -падение напряжения на резисторе 12. Как только включится транзистор 8 напряжение на его коллекторе становится равным падению напряжения на резисторе 12 (/vO,25 В), открывается транзистор 13, и часть тока, протекавшая ранее через транзистор 3, потечет через транзистор 13 и ДИод 6 в коллектор транзистора 8. Базовый

ток транзистора 8 уменьшится (его I величина будет определяться коэффициентом усиления транзистора 8), а весь избыточный ток будет протекать через транзистор 13 в коллектор выходного транзистора 8.

При этом напряжение между коллектором и эмиттером транзистора 3 достигает значения, равного падению напряжения на резисторах 11 и 12, и фик сируется на этом уровне 0,5 В) благодаря действию отрицате;1ьной обратной связи с базы на кoллekтop транзистора 3 через дополнительный эмиттер входного транзистора 1.

Падение напряжения на резисторах 11 и 12, включенных параллельно переходу коллектор - база транзистора 1 ниже уровня, при котором коллектор- ный переход начинает инжектировать,,. Поэтому при уровне напряжения логической 1 на входах 1 исключена возможность потребления как импульсного, так и статического тока.

Таким образом обеспечивается ограничение степени насыщения транзисторов 3 и 13 парафазного каскада и транзистора 8 выходного каскада.

Если теперь на входах 1А вновь создавать низкий уровень напряжения, транзисторы 3 и 13 быстро выключаются при этом прекращается ток в базы выходного транзистора 8, который также в силу отсутствия избыточного базового заряда быстро выключается. При этом существенно уменьшается бросок тока при выключении схемы.

Таким образом в предлагаемом устройстве обеспечивается ограничение насыщения всех активных элементов схемы, что способствует увеличению ее быстродействия без применения диффузии золота и повышению экономичности;

Формула изобретения

Интегральная логическая схема, содержащая входной многоэмиттерный транзистор, база которого через резистор соединена с шиной питания, коллектор - с базой первого транзистора парафазного каскада, коллектор которого соединен с коллектором второго транзистора парафазного каскада и базой первого транзистора выходного каскада, коллектор которого через резистор соединен с шиной питания, эмиттер через диод - с коллектором второго транзистора выходного каскада, эмиттер которого соединен с общей шиной, база - с эмиттером первого транзистора парафазного каскада и через резистор с общей шиной, коллектор первого транзистора парафазного каскада через резистор соединен с шиной питания, отличаю.щаяс у; тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, введен резистивный делитель включенный между базой и коллектором входного многоэмиттерного транзистора средняя точка которого подключена к базе второго транзистора парафазного каскада, эмиттер которого подключен к эмиттеру первого транзистора выходного каскада, база которого соединена с одним из эмиттеров входного многоэмиттерного транзистора.

Источники информации, принятые во внимание при экспертизе

кл. Н 03 К 19/08, 1976.

Авторы

Даты

1983-02-28—Публикация

1979-10-12—Подача