(54) ИНТЕГРАЛЬНАЯ ЛОГИЧЕСКАЯ СХЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ—НЕ» и «И-ИЛИ» | 1970 |

|

SU260680A1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ВОЗБУЖДЕНИЯ ДЛИННЫХ ЛИНИЙ | 1973 |

|

SU364106A1 |

t

Изобретение относится к микроэлектронике и может быть использовано при построении интегральных схем . памяти.

Известна логическая схема, выполненная на основе инвертора, в которой предусмотрено шунтирование перехода база-эмиттер выходного транзистора диодами ШОттки, чем обеспечивается достаточно высокое быстродействие Cil.

Однако известная схема характеризуется значительным потреблением мощности,

Наиболее близким техническим решением к предлагаемой логической схеме является ТТЛ-схема, содержащая входной многоэмиттерный ранзистор, подсоединённый коллектором к базе транзистора парафазного каскада, коллектор которого соединен с базой первого транзистора выходного каскада, выполненного на двух последовательно включенных через диод транзисторах, а эмиттер - к базе второго транзистора выходного каскада 22.

Недостаток известной низкое быстродействие, рост потребляемой мощности с ростом частоты переключений., выходного тока нагрузки.

Цель изобретения - стабилизация выходного тока при высоком быстродействии и экономичности схемы.

Поставленная цель достигается тем, что в интегральной логической схеме, содержащей входной многоэмиттерный транзистор, эмиттеры которого подключены к входным шинам, база через резистор к положительной шине, а

10 коллектор к базе первого транзистора парафазного каскада, эмиттер которого через резистор соединен с земляной шиной и с базой второго транзистора выходного каскада, эмиттер ко15торого соединен с земляной шиной, а коллектор подключен к эмиттеру первого транзистора выходного каскада и к выходной шине, коллектор первого транзистора парафазного кас20ксща подключен к положительной шине, а змиттер - к базе второго транзистора, эмиттер которого, соединен с земляной шиной, а коллектор - с нагрузочным источником тока, с базой

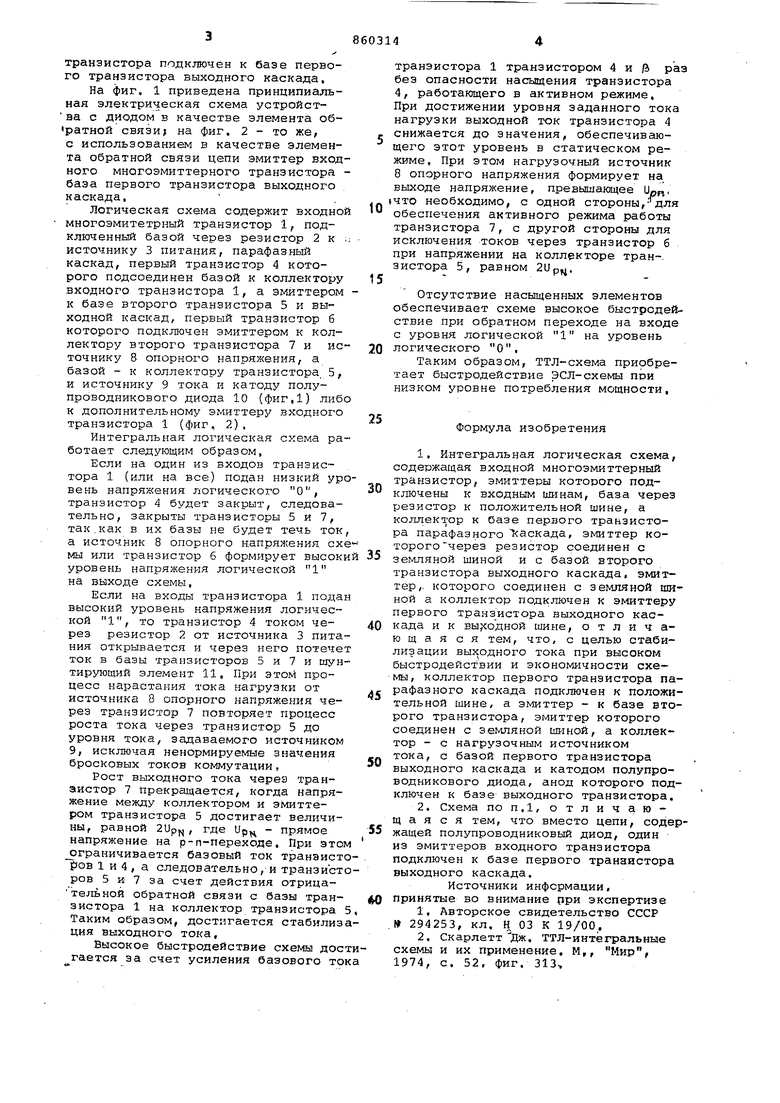

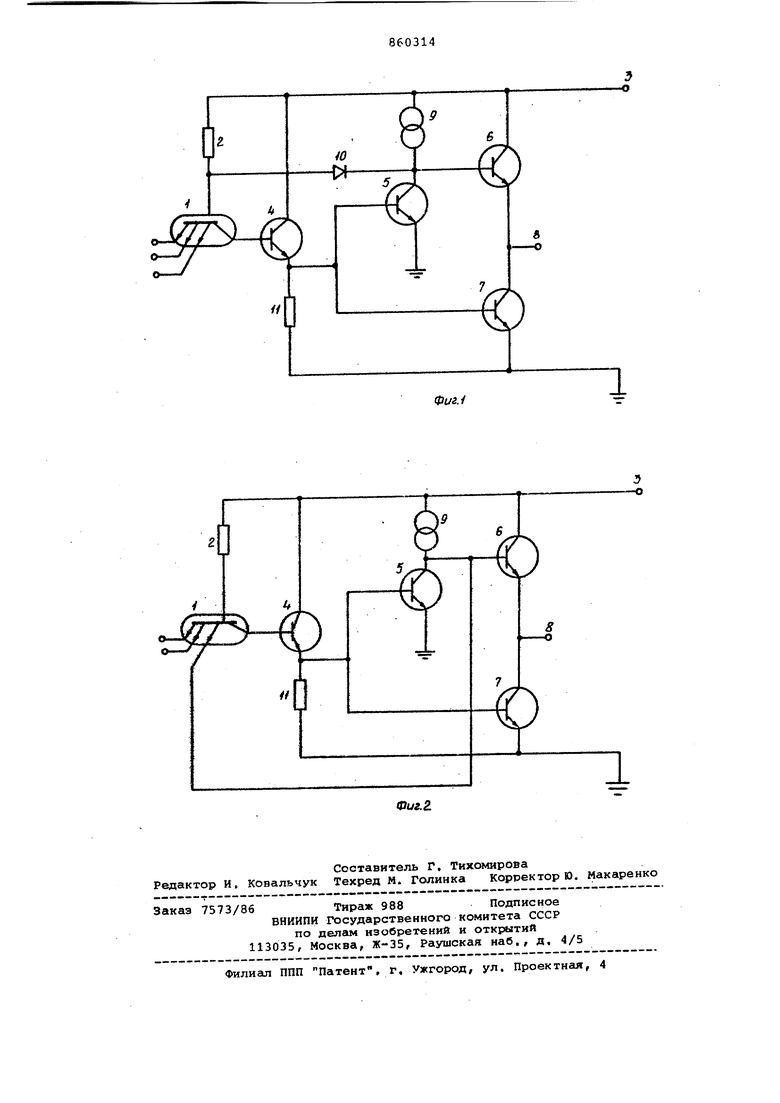

25 первого транизстора выходного каскада и катодом полупроводникового дно. да, анод которого подключен к базе входного транзистора, либо вместо цепи, содержащей полупроводниковый, 30 диод, один из змиттеров входного транзистора подключен к базе первого транзистора выходного каскада. На фиг, 1 приведена принципиальная электрическая схема устройства с лиодом в качестве элемента об«ратной связи; на фиг, 2 - то же, с использованием в качестве элемента обратной связи цепи эмиттер вход ного многоэмиттерного транзистора база первого транзистора выходного каскада. Логическая схема содержит входно многоэмитетрный транзистор 1, подключенный базой через резистор 2 к источнику 3 питания, парафазный каскад, первый транзистор 4 которого подсоединен базой к коллектору входного транзистора 1, а эмиттером к базе второго транзистора 5 и выходной каскад, первый транзистор 6 которого подключен эмиттером к коллектору второго транзистора 7 и ис точнику 8 опорного напряжения, а базой - к коллектору транзистора 5, и источнику 9 тока и катоду полупроводникового диода 10 (фиг,) либ к дополнительному эмиттеру входного транзистора 1 (фиг, 2), Интегральная логическая схема ра ботает следующим образом. Если на один из входов транзистора 1 (или на все) подан низкий ур вень напряжения логического О, транзистор 4 будет закрыт, следовательно, закрыты транзисторы 5 и 7, так.как в их базы не будет течь ток а источник 8 опорного напряжения сх мы или транзистор б формирует высок уровень напряжения логической 1 на выходе схемы, Если на входы транзистора 1 пода высокий уровень напряжения логической 1, то транзистор 4 током через резистор 2 от источника 3 пита ния открывается и через него потече ток в базы транзисторов 5 и 7 и шун тирующий элемент 11, При этом процесс нарастания тока нагрузки от источника 8 опорного напряжения через транзистор 7 повторяет процесс роста тока через транзистор 5 до уровня тока, задаваемого источником 9, исключая ненормируемые значения бросковых токов коммутации. Рост выходного тока через транзистор 7 прекращается, когда напряжение между коллектором и эмиттером транзистора 5 достигает величины, равной 2Upf , где Up - прямое напряжение на р-п-переходе. При это рграничивается базовый ток транзист ров 1 и 4 , а следовательно,-и транзист ров 5 и 7 за счет действия отрицательной обратной связи с базы транзистора 1 на коллектор транзистора Таким образом, достигается стабилиз ция выходного тока, Высокое быстродействие схемы дос гается за счет усиления базового то транзистора 1 транзистором 4 и /i раз без опасности насыщения транзистора 4, работающего в активном режиме. При достижении уровня заданного тока нагрузки выходной ток транзистора 4 снижается до значения, обеспечиваюего этот уровень в статическом режиме. При этом нагрузочный источник 8 опорного напряжения формирует на выходе напряжение, превышающее dpn ЧТО необходимо, с одной стороны, для обеспечения активного режима работы транзистора 7, с другой стороны для исключения токов через транзистор 6 при напряжении на коллекторе тран-. зистора 5, равном 20рп. Отсутствие насыщенных элементов обеспечивает схеме высокое быстродействие при обратном переходе на входе с уровня логической 1 на уровень логического О, Таким образом, ТТЛ-схема приобретает быстродействие ЭСЛ-схемы ПРИ низком уровне потребления мощности. Формула изобретения 1,Интегральная логическая схема, содержащая входной многоэмиттерный транзистор, эмиттеры которого подключены к входным шинам, база через резистор к положительной шине, а коллектор к базе первого транзистора парафазного Тсаскада, эмиттер которогочерез резистор соединен с земляной шиной и с базой второго транзистора выходного каскада, эмиттер,, которого соединен с земляной шиной а коллектор подключен к эмиттеру первого транзистора выходного кас када и к вы одной шине, отличающая с я тем, что, с целью стабилизации выходного тока при высоком быстродействии и экономичности схемы, коллектор первого транзистора парафазного каскада подключен к положительной шине, а эмиттер - к базе второго транзистора, эмиттер которого соединен с земляной шиной, а коллектор - с нагрузочным источником тока, с базой первого транзистора выходного каскада и катодом полупроводникового диода, анод которого подключен к базе выходного транзистора. 2.Схема поп,1, отличающаяся тем, что вместо цепи, содержащей полупроводниковый диод, один из эмиттеров входного транзистора подключен к базе первого транзистора выходного каскада. Источники информации, принятые во внимание рри экспертизе 1,Авторское свидетельство СССР . 294253, кл, Н 03 К 19/00. 2,Скарлетт Дж, ТТЛ-интегральные схемы и их применение, М,, Мир, 1974, с, 52, фиг, 313,

Авторы

Даты

1981-08-30—Публикация

1979-08-03—Подача