1

Изобретение относится к области автоматики и вычислительной техники.

Известны коммутирующие устройства с 1 f -разрядными входами и NA f -разрядными выходами, содержащие полный коммутатор l.

Известно также коммутирующее устройство с К f -разрядными входами и М г разрядными выходами, содержащее полный коммутатор с К Г -разрядными входами И К Г -разрядными выходами, К ассоциативных запоминающих устройств и К линейных коммутаторов 2 .

К недостаткам известнь х устройств относится большой объем используемого оборудования и высокая сложность управления.

Целью изобретения является уменьшение объема используемого оборудования и упрощение управления коммутирующего устройства.

Это достигается тем, что в коммутирующем устройстве с К f -разрядными входами и М Р -разрядными выходами, где К М , содержащем полный .коммутатор с К -разрядными входами и К г -разрядными выходами, К ассоциативных запоминающих устройств и К линейных коммутаторов, h -разрядные входы коммутирующего устройства подключены ко входам соответствующих ассоциативных запоьтенающих устройств, выходы которых подключены к одноименным -разрядным входам полного коммутатора, Г -разрядные выходы которого подключены ко входам соответствующих линейных коммутаторов, а -разрядные выходы линейного коммута,тора подключены к Y 1 .-разрядным выходам коммутирующего устройства.

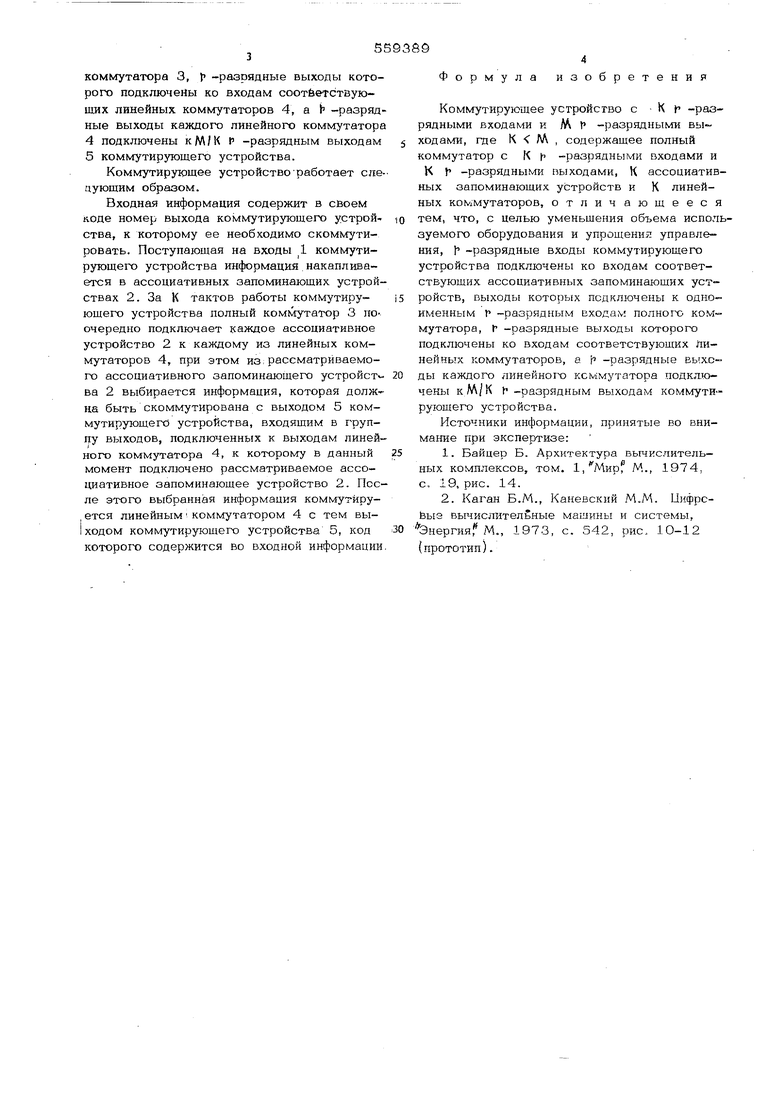

Функциональная схема комкгутируюшего устройства представлена на чертеже и содержит следующие элементы: входы 1. коммутирующего устройства; ассоциативные запоминающие устройства 2; полный коммутатор 3; линейные коммутаторы 4; выходы 5 коммутирующего устройства.

If -разрядные входы 1 коммутирующего устройства подключены ко входам соответствующ11х ассоциативных оапомннаюших уст9

выходы которых подключены к

ропств

одноименным 1 -разсядным входам полного коммутатора 3, -разрядные выходы которого подключены ко входам соотбетствующих линейных коммутаторов 4, а h -разрядные выходы каждого линейного коммутатора 4подключены кМ/К Р -разрядным выходам 5коммутирующего устройства. Коммутирующее устройство-работает елецуюшим образом. Входная информация содержит в своем коде номер выхода коммутирующего устройства, к которому ее необходимо скоммутировать. Поступающая на входы 1 коммутирующего устройства информация накапливается в ассоциативных запоминающих устройствах 2. За К тактов работы коммутирующего устройства полный коммутатор 3 поочередно подключает каждое ассоциативное устройство 2 к каждому из линейных коммутаторов 4, при этом ИЗ; рассматриваемого ассоциативного запоминающего устройст ва 2 выбирается информация, которая долж-ка быть скоммутирована с выходом 5 коммутирующего устройства, входящим в группу выходов, подключенных к выходам линейного коммутатора 4, к которому в данный момент подключено рассматриваемое ассоциативное запоминающее устройство 2. После этого выбранная информация коммутИру, ется линейным коммутатором 4 с тем выI ходом коммутирующего устройства 5, код которого содержится во входной информации. Формула изобретения Коммутирующее усгройсгво с К h -разрядными входами и /А Р -разрядными вы ходами, где К ЛЛ , содержащее полный коммутатор с К h -разрядными входами и К -разрядными выходами, К ассоциативных запоминающих устройств и К линейных коммутаторов, отличающееся тем, что, с целью уменьшения объема используемого оборудования и упрощения управле- ния, -разрядные входы коммутирующего устройства подключены ко входам соответствующих ассоциативных запоминающих устройств, выходы KOTOpbix подключены к одноименным Р -разрядным входам полного коммутатора, f -разрядные выходы которого подключены ко входам соответствующих Линейных коммутаторов, а f -разрядньЕе вь ходы каждого линейного коммутатора подключены кМ/К t -разрядным выходам коммутирующего устройства. Источники информации, принятые во внимание при экспертизе: 1.Байцер Б. Архитектура вычислительных комплексов, том, l,MHpf М., 1974, с, 19, рис. 14. 2.Каган Б.М., Каневский М.М. ЦифрсЬыэ вычислительные машины и системы, Энергия М., 1973, с. 542, рис, 10-12 (прототип).

5

1

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутирующее устройство с приоритетной коммутацией | 1985 |

|

SU1316079A1 |

| Коммутирующее устройство | 1980 |

|

SU875628A2 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310307A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1247948A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Конвейерный умножитель | 1988 |

|

SU1575175A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Ассоциативное запоминающее устройство и ассоциативный накопитель информации для него | 1981 |

|

SU976477A1 |

5

: 5

Авторы

Даты

1977-05-25—Публикация

1975-02-28—Подача