Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем, таких как векторные процессоры, процессоры цифровой обработки сигналов и другие.

Цель изобретения - повышение быстродействия умножителя,

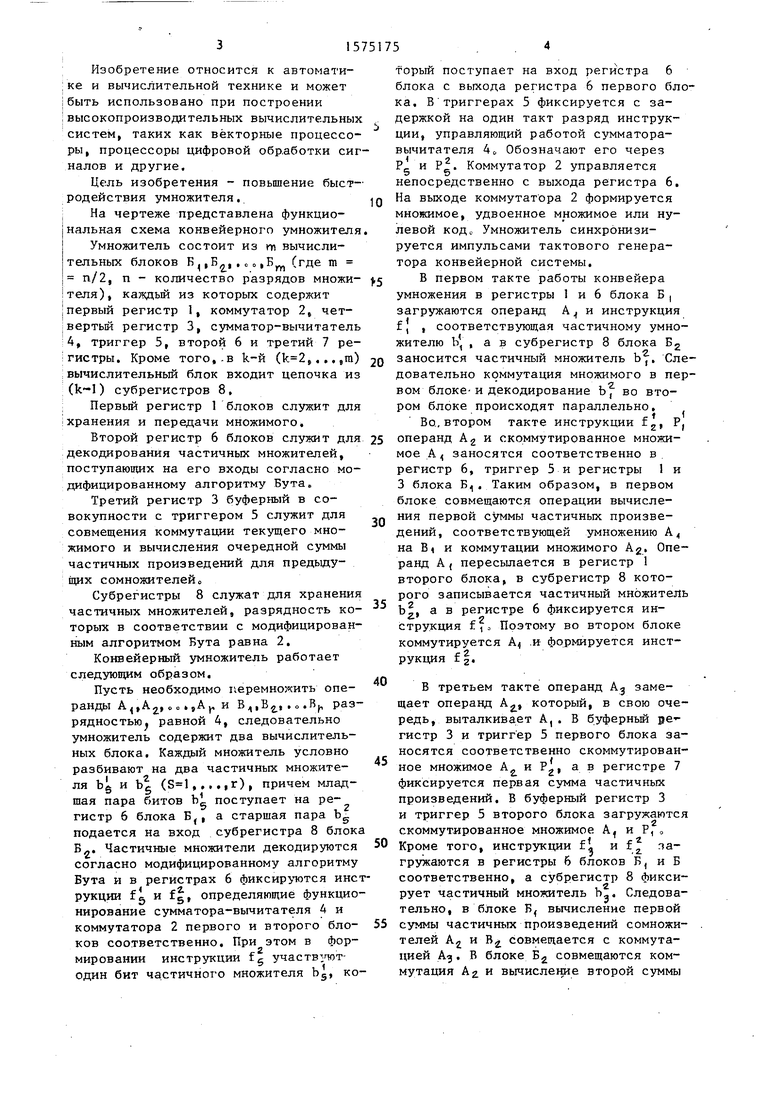

На чертеже представлена функцио- |Нальная схема конвейерного умножителя 1 Умножитель состоит из m вычислительных блоков Б, .Б, . „ о ,5 (где m n/2, n - количество разрядов множителя), каждый из которых содержит первый регистр 1, коммутатор 2, четвертый регистр 3, сумматор-вычитатель 4, триггер 5, второй 6 и третий 7 регистры. Кроме того,.в k-й (,...,m) вычислительный блок входит цепочка из (k-1) субрегистров 8.

Первый регистр 1 блоков служит для хранения и передачи множимого.

Второй регистр 6 блоков служит для декодирования частичных множителей, поступающих на его входы согласно модифицированному алгоритму Бута„

Третий регистр 3 буферный в совокупности с триггером 5 служит для совмещения коммутации текущего множимого и вычисления очередной суммы частичных произведений для предыдущих сомножителейо

Субрегистры 8 служат для хранения частичных множителей, разрядность которых в соответствии с модифицированным алгоритмом Бута равна 2.

Конвейерный умножитель работает следующим образом.

Пусть необходимо перемножить операнды , „ „ ,,Ар и В,Ве, . о .Bj, разрядностью, равной 4, следовательно умножитель содержит два вычислительных блока. Каждый множитель условно разбивают на два частичных множителя bg и b| (,...,г), причем младшая пара битов Ь поступает на регистр 6 блока Б(, а старшая пара bg подается на вход субрегистра 8 блока Б2. Частичные множители декодируются согласно модифицированному алгоритму Бута и в регистрах 6 фиксируются инструкции fg и f|, определяющие функционирование сумматора-вычитателя 4 и коммутатора 2 первого и второго блоков соответственно. При этом в формировании инструкции f5 участвуют один бит частичного множителя bs, ко

0

5

0

5

торый поступает на вход регистра 6 блока с выхода регистра 6 первого блока, В триггерах 5 фиксируется с задержкой на один такт разряд инструкции, управляющий работой сумматора- вычитателя 4й Обозначают его через 5 и р|. Коммутатор 2 управляется непосредственно с выхода регистра 6. На выходе коммутатора 2 формируется множимое, удвоенное множимое или нулевой код. Умножитель синхронизируется импульсами тактового генератора конвейерной системы.

В первом такте работы конвейера умножения в регистры 1 и 6 блока Б , загружаются операнд А . и инструкция

ti

f, , соответствующая частичному умножителю b , а в субрегистр 8 блока Б2 заносится частичный множитель Ь. Следовательно коммутация множимого в первом блоке- и декодирование Ь во втором блоке происходят параллельно.

Во,втором такте инструкции fz, P, операнд А2 и скоммутированное множимое А заносятся соответственно в регистр 6, триггер 5 и регистры 1 и 3 блока Б,. Таким образом, в первом блоке совмещаются операции вычисления первой суммы частичных произведений, соответствующей умножению А,, на В и коммутации множимого А2. Операнд А ( пересылается в регистр 1 второго блока, в субрегистр 8 которого записывается частичный множитель

z

а в регистре 6 фиксируется инструкция f,, Поэтому во втором блоке коммутируется А4 и формируется инст 2«

рукция f

В третьем такте операнд А3 замещает операнд А, который, в свою очередь, выталкивает А,. В буферный в гистр 3 и триггер 5 первого блока заносятся соответственно скоммутированное множимое А и Р , а в регистре 7 фиксируется первая сумма частичных произведений. В буферный регистр 3 и триггер 5 второго блока загружаются скоммутированное множимое Af и Р, „ Кроме того, инструкции ft и f загружаются в регистры 6 блоков Б, и Б соответственно, а субрегистр 8 фиксирует частичный множитель Ь3. Следовательно, в блоке Б{ вычисление первой суммы частичных произведений сомножителей А и В совмещается с коммутацией Ад, В блоке Б2 совмещаются коммутация Аг и вычисление второй суммы

515

частичных произведений для операндов А ц и В v ,

В четвертом такте множимое А. скоммутированное множимое А, инструкция f4 и Р заносятся в соответ- ствующие узлы первого блока. Множимое

fj

частичный множитель Ь. , скоммутированное множимое А,, , инструкция

2 у

г. и Р запоминаются в соответст- овующих узлах блока Б2. В регистрах 7 обоих блоков фиксируются суммы частичных произведений, полученные в третьем такте. При этом на выходе умножителя будет произведение операндов А4 и В ,.

В пятом такте множимое Ау, скоммутированное множимое Ах . инструкция f,|/Т

и Ру заносится в соответствующие узлы первого блока, Множимое А,., час- тичный множитель Ъ $ , скоммутирован- ное множимое А3, инструкция f| и Р| запоминаются в соответствующих узлах второго блока. Очередные суммы частичных произведений, полученные в четвер том такте, фиксируются в регистрах 7 блоков Б,, и Б. При этом на выходе конвейерного умножителя будет произведение операндов В2 ,

И так далее,

Таким образом, умножитель выдает произведение двух операндов, в каждом такте, начиная со второго

Формула изобретения

Конвейерный умножитель, содержащий m вычислительных блоков (, где п - разрядность множителя), каждый из которых содержит первый, второй и третий регистры, сумматор-вычи- татель, коммутатор и i-1 субрегист- ров (,,,,,m), причем вход множимого умножителя соединен с информационным входом первого регистра первого вычислительного блока, входы синхронизации первого второго и третьего регистров, каждого субрегистра всех вычислительных блоков соединены с

75

входом синхронизации умножителя, вход множителя которого соединен с первым информационным входом второго регистра первого вычислительного бло ка и информационным входом первого субрегистра каждого k-ro вычислительного блока (,,.,,m), а в каждом 1-м вычислительном блоке выход первого регистра соединен с информационным входом коммутатора, управляющий вход которого соединен с первым выходом второго регистра, выход сумма тора-вычитателя соединен с информационным входом третьего регистра, выход 1-го субрегистра (,.,.,т-2) соединен с информационным входом (1+1)-го субрегистра, выход (i-l)-ro субрегистра соединен с первым информационным входом второго регистра, выходы первого и третьего регистров и второй выход второго регистра j-ro вычислительного блока (,,.., m-1) соединены соответственно с информационным входом первого, первым информационным входом сумматора-вы - читателя и вторым информационным входом второго регистра (j-H)-ro вычислительного блока, выход третьего регистра m-го вычислительного блока соединен с выходом результата умножителя, о тличающийся тем, что, с целью повышения быстродействия, в каждый вычислительный блок введены четвертый регистр и триггер, причем входы синхронизации четвертого регистра и триггера каждого вычислительного блока соединены с входом синхронизации умножителя, а в каждом вычислительном блоке третий выход второго регистра соединен с информационным входом триггера, выход которого соединен с управляющим входом сумма- тора-вычитателя, второй информационный вход которого соединен с выходом четвертого регистра, информационный вход которого соединен с выходом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерный цифровой умножитель | 1987 |

|

SU1464170A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для умножения | 1985 |

|

SU1252774A1 |

| Устройство для вычисления сумм произведений | 1987 |

|

SU1636842A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении векторных процессоров, процессоров цифровой обработки сигналов. Цель изобретения - повышение быстродействия умножителя. Новым в умножителе, содержащем M вычислительных блоков, каждый из которых содержит регистры 1, 6 и 7, коммутатор 2, сумматор-вычитатель 4, и I-1 субрегистров 8, является введение в каждый вычислительный блок регистра 3 и триггера 5, благодаря которым обеспечивается совмещение операций коммутации множимого и суммирования/вычитания частичных произведений для предыдущих сомножителей, что приводит к ускорению процесса вычисления сумм частичных произведений. 1 ил.

| Авторское свидетельство СССР , 1206800, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерный цифровой умножитель | 1987 |

|

SU1464170A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-06-17—Подача