(54) КОММУТИРУЮШЕ Е УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Программируемое запоминающее устройство | 1977 |

|

SU736170A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Процессор | 1977 |

|

SU691858A1 |

| Коммутирующее устройство для проверки параметров электрических цепей | 1980 |

|

SU966627A1 |

1

Изобретение относится к автоматике и вычислительной технике.

По основному авт. св. № 559389 известно коммутирующее устройство, содержащее К запоминающих устройств, выходы которых соединены с полным коммутатором, разрядные выходы полного коммутатора подключены ко входам соответствующих линейных KOMMyTaTOpoBLlJ

Недостаток указанного устройства . состоит в низком быстродействии его работы вследствие последовательной организации обмена..

Цель изобретения - повышение бь1стродействия.

С этой целью в коммутирующее устройство с К-Г - разрядными входами и разрядными выходами, содержащее К запоминающих устройств, - разрядные входы которых являются входами устройства, полный коммутатор, информационные 1 - разрядные входы которого соединены с одноименными выходами соответствующих запоминающих устройств, информационные Т- разрядные выходы полного коммутатора соединены с одноименными входами соответствующих линейных коммутаторов, а 1 - разрядные выходы каждого линейного коммутатора соединены с М/К - разрядными выходами устройства, введены де- ши|1ратор, регистр и блок управления, причем адресные выходы запоминающих, устройств соединены с адресными вхо10дами дешифратора, выход которого подключен к регистру, при этом первый выход блока управления соединен с управляющим входом дешифратора, а второй выход - с управляющим входом регис- 15ра, вькоды которого подключены к управляющим входам линейных и полного коммутаторов.

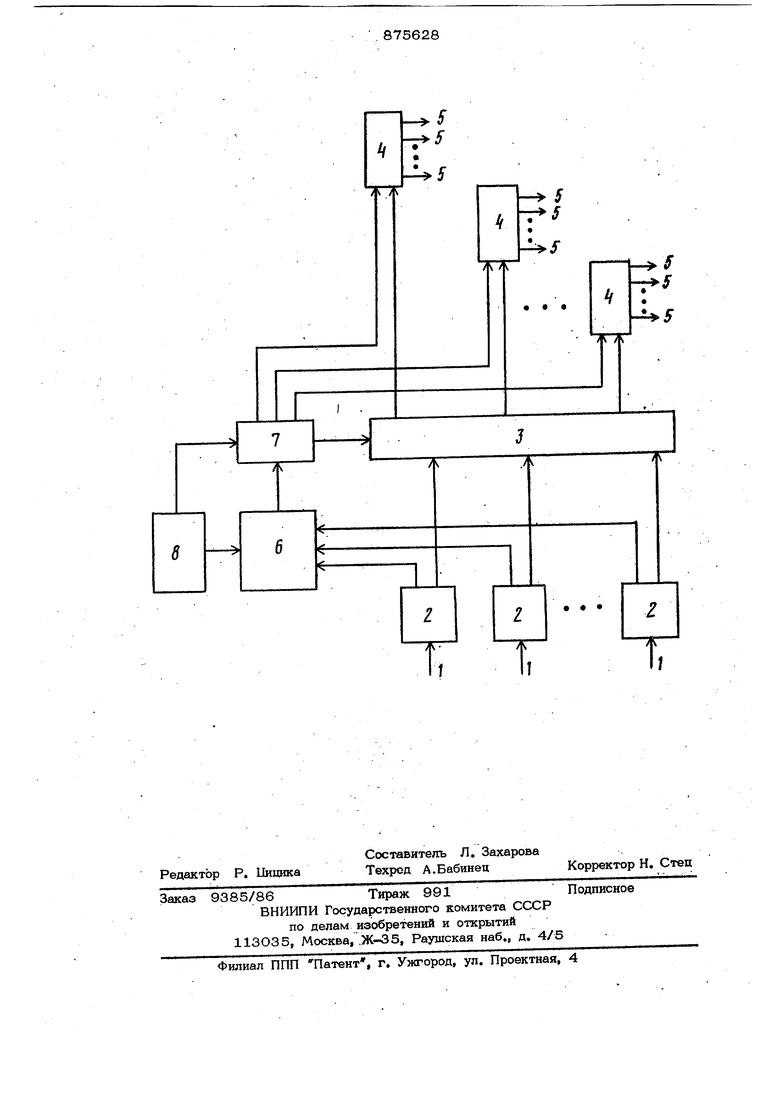

На чертеже представлена функциональ-, ная схема коммутирующего устройства.

20

Схема содержит входы 1, запоминак щие устройства 2, коммутатор 3, линейные коммутаторы 4, выходы 5 коммутирующего устройства, многосекционный. дешифратор 6, регистр 7, блок управления 8« Устройство работает спедукяцим образом. Входная информашга содержит код номера выхода коммутирующего устройства k которому ее необходимо скоммутировать. Поступающая на входы 1 коммутщ)укяцего устройства информашш накапливается в запоминакяцих устройствах 2 Коды номеров вы: содов с каждого запоминающего устройства 2 поступают на . многосекционный дешифратор 6, причем код на свою секцию Продезиифрир(жанные сигналы адресов коммутации зап минаются на регистре 7, с которого поступают, далее на управляющие цепи линейных Коммутаторов 4 и комму та тора 3. Блок 8 управления вырабатьшает две команды По первой команде, поступающей на многосекционный дешифратор 6, происходит дешифрация кодов номеров выводов коммутирующего устройства и их запись на регистр 7, По второй команде блока 8 управления управляющие сигналы коммутации с регистра 7 поступают на управляющие цепи коммутаторов 3 и 4, которые осуществляют коммутацию цепей и параллельную передачу информации со входов 1 устройства на соответствующие выходы 5 устройства. Таким образом, полная передача информации коммутирующим устройством осуществляется за один такт работы, вкл 284 чаклцим в себе две команды. Необходимость двух команд обуславливается разделением работы устройства на подготовительные операции и собственно передачу информации. Введение многосекционного дешифратора 6, регистра 7 и блока 8 управления позволяет увеличить быстродействие работы устройства в К раз. Фор м у ла изобретения Коммутирующее устройство по авт. св. № 559389, отличаюшеес я тем, что, с целью повышения быстродействия, в него введены дешифратор, регистр и блок управления, причем адресные выходы запоминающих устройств соединены с адресными входами дешифратора, выход которогю подключен к регистру, при этом первый выход блока управления соединен с управляющим входом де.шифратора, а второй выход с управпяк щим входом регистра, выходы которого подключены к управляющим входам линейных и полного коммутаторов. Источники информации, принятые во внимание при экспертизе , 1. Авторское свидетельство СССР № 559389, кл.Н 03 К 17/00, 1975 (прототип).

Авторы

Даты

1981-10-23—Публикация

1980-02-22—Подача