Изобретение относите; к области вычислительной техники, в частности к устройствам управления систем контроля, и может быть использовано при производстве илитехническом обслуживании средств вычислительной техники для осущесгвлепия их контроля.

1-1звестно устройство 1 для управления системой контроля, содержандее блок местного управления устройствами звода программ с перфоленты и с исрфокарт, выходы которого соединены с входным буферным регистром, регистр команды, выход которого через дешифратор связан с генератором управляюнд1х сигналов, счетчик длины команды, первый блок сравнения, входы которого иодключены к буферному регистру и регистру номера теста, первый и второй ииформационные регистры, выходы которых соединены с вторым блоком сравнения, а входы второго из них - с выходами контролируемого объекта, счетчик циклов повторения, связанный с регистром номера теста, и регистр кода операции. Входы регистра команды, счетчика циклов повторения, регистра кода операции, счетчика длины команды и первого ннформацио ного регистра связаны с выходами буферного регистра. Выходы буферного регистра, регистра кода операции и генератора управляющих сигналов иодключены к исполнительным блокам системы контроля, обеспечиваюни1м приложение

2

тестовых сигналов к входам контролируемого объекта.

Недостатками данного устройства ямг.лются весьма ограниченный набор onepani.n обработки (только сравнение), низкое быстродействие, онрсдел.чемое скоростью устройства ввода программы, отс тствие униф:1цпро анного соиряжеиия с внешними устросйтвами, что делает иевоз:,южньп1 использование з системе контроля разлнчных ycrpoiicTB вывода И1 формации, устройств параметрического контроля объектов и т. д.

Известно также устройство 2 .тля управления системой контроля, содержащее регистр кода и регистр адреса, выходы которых связаны соответственно с кодовыми и адресными шинами сопряжения с виешними устройствами, регистр данных, соединенный с ннформационнымн шинами сопряжения, дешифратор, выходы которого подключены к входам указанных регистров, а входы - к блоку уиравления распределением ипформашш. б. ;eстного уиравлеиия устройством i oграмм с иерфолеиты, связаи ы; ; )cpный регистр н сумматор с входами де:Ги(р к- тора, коммутатор, входы которого соединены с выходами указанных регистров и бло-.а управления распре.телением информации, а выход - с входами буферного регистра, генератор уиравляющих сигналов, входы н-выходы

которого соединены с шинами синхронизации внешних устройств.

Это устройство обесиечивает унифицироваиное сопряжение с внешними устройствами системы (с устройствами вывода данных, задания воздействий на объект контроля и анализа его реакций), что существенно расширяет функциональные возможности системы и нозволяет изменить ее состав в зависимости от требований конкретного нрименения.

Указанное устройство имеет такие недостатки, как низкое быстродействие, ненрисиособленность для работы одновременно с несколькими устройствами задания программ, а также с такими устройствами, как оперативные ЗУ, накопители на магнитной лейте и т. и. Это исключает возможность изменения состава устройств задания нрограмм в системе контроля в зависимости от требуемого бытродействия и объема программ, хранения в системе библиотеки контрольных программ, рассчитанной на широкую номенклатуру контролируемых объектов, и автоматического доступа к этой библиотеке, а также возможность эффективного сжатия объема нрограмм за счет использования обш;их подпрограмм, хранимых в оперативном ЗУ, т. д.

Известно также наиболее близкое к изобретению но технической сущности и достигаемому результату устройство 3 для унравлення системой контроля цифровых схем, содержащее регистр кода операции, выход которого соединен с кодовой шиной устройства, регистр адреса, выходом связанный с адресной шиной устройства, первый регистр данных, иервый выход которого соединен с первой информационной шиной устройства, второй регистр данных, арифметико-логический блок, информационные входы которого подключены к второму выходу нервого и выходу второго регистров даиных, счетчик длииы команды, первый коммутатор, выход которого соединен с информационными входами счетчика длины команды, нервого и второго регистров данных, регистров кода онерацин и адреса.

Кроме того, устройство включает в себя блок буферных регистров, вход и выход которого соединены соответственно с выходом второго коммутатора и первым информационным входом третьего коммутатора, блок индикации, вторую ииформационную шину, генератор унравляющих сигналов, первый и второй входы и выхо;;ы которого с первого но пятый соединены соответственно с снгнальной шииой устройства, с выходом счетчика длины команды, с управляющими входами регистра кода операции, арифметико-логического блока, счетчика длины команды, первого коммутатора и управляющей шиной устройства, блоки соиряжения с устройствами задания программ, входы - выходы, первые, вторые, третьи входы которых связаны соответственно с входами - выходами устройства, с кодовой, адресной и управляющей шинами устройства. Устройство 3 обладает наибольшими

функциональными возможностями среди известиых устройств. Оно обеспечивает широкий набор операций обработки информации и программного управления внешними устройствами системы, предусматривает возможность задания программ как непосредственно (без оперативного ЗУ) от устройств ввода, так и от оперативного ЗУ, позволяет использовать в системе одиовременно несколько устройств задания программ и изменять их состав в зависимости от коикретных требований, обеспечивает унифицироваииое сопряжение для всех внешних устройств и устройств задания программ за исключением оперативного ЗУ.

Недостатком данного устройства является большие затраты аииаратуры в его базовой (минимальной) модификации, не содержащей блока местиого управления оперативным ЗУ и рассчитанной на задания нроргамм от устройства ввода с перфоленты. Это увеличивает стоимость создаваемых на основе данной модификации устройства наиболее простых систем контроля цифровых объектов.

Цель изобретения - сокращение оборудования устройства.

Это достигается тем, что устройство содержит четвертый коммутатор и наборный регистр, причем первый - четвертый информационные входы и выход четвертого ком утатора соединены соответственно с выходом наборного регистра, с второй информационной шиной устройства, с выходом третьего коммутатора, с выходом арифметико-логического блока и входом первого коммутатора, информационный вход блока индикации - с выходом третьего коммутатора, выход - с вторым ииформационным входом третьего коммутатора, выход арифметико-логического блока - с информационным входом второго коммутатора. Унравляющие входы блока индикации, второго, третьего и четвертого коммутаторов связаиы соответственно с шестым - девятым выходами генератора управляющих сигналов, четвертый вход, первые и вторые выходы блоков сопряжения с устройствами задания ирограмм - соответственно с первой, второй информационными и сигнальной шинами устройства. Цель достигается тем, что каждый блок сопряжения с устройством задания нрограмм содержит дещцфраторы адреса и кода операции, формирователь управляющих сигналов, узел индикации состояния, входной и выходной коммутаторы, операционный узел. Цервый - четвертый входы формирователя уиравляющих сигиалов соединены соответственно с иервым выходом операционного узла, с выходом дешифратора адреса, с первым выходом дешифратора кода операции, с третьим

входом блока, первый выход формирователя управляющих сигналов - с вторым входом онерационного узла, с первыми входами выходиого и входиого коммутаторов, вторые входы которых связаны соответственно с третьим

выходом операционного узла и четвертым входом блока. Первый и третий входы и второй выход операционного узла соединены соответственно с выходами дешифратора кода операции, входного коммутатора и с первым входом узла индикации состояния, второй вход которого подключен к второму выходу формирователя управляющих сигналов, входы дешифраторов адреса и кода операции, выходы узла индикации состояния и выходного коммутатора соединены соответственно с вторым и первым входами н с вторым и первым выходами блока.

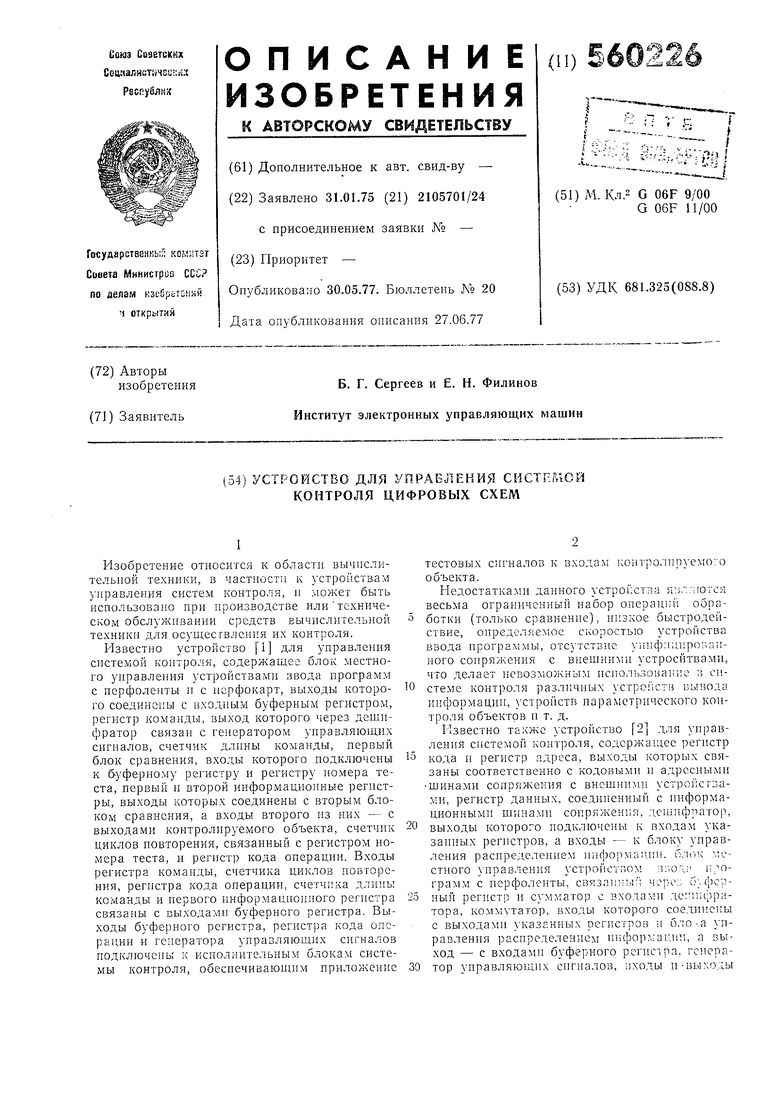

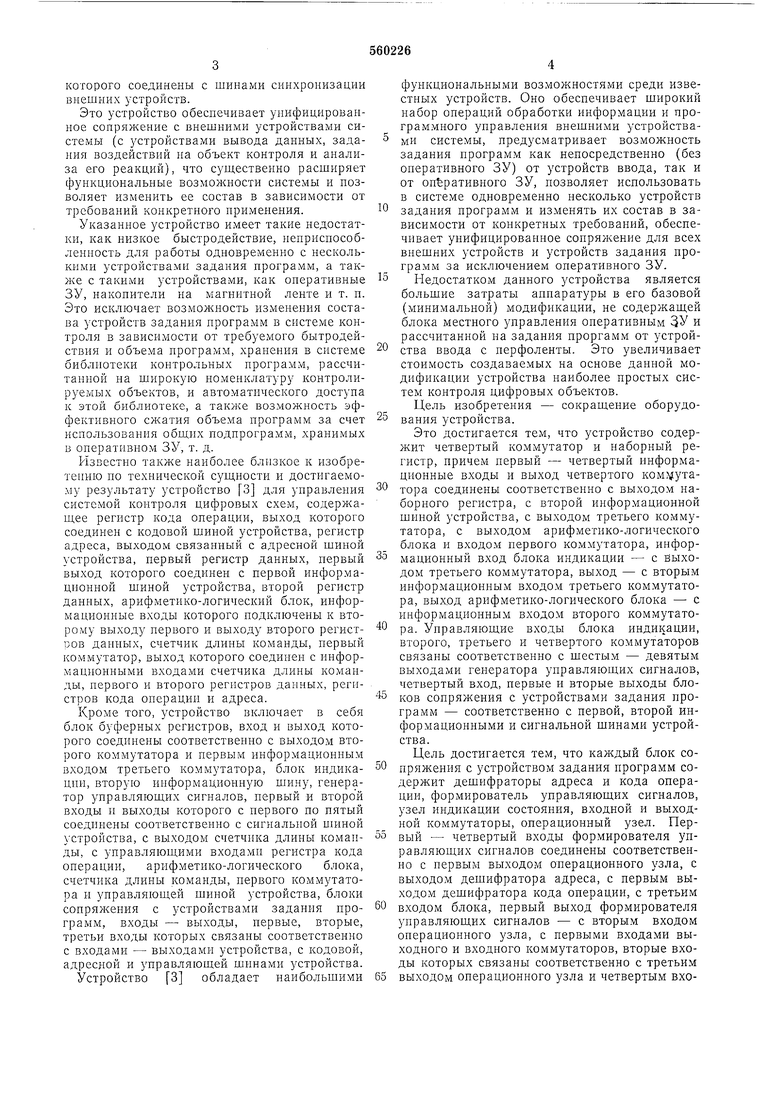

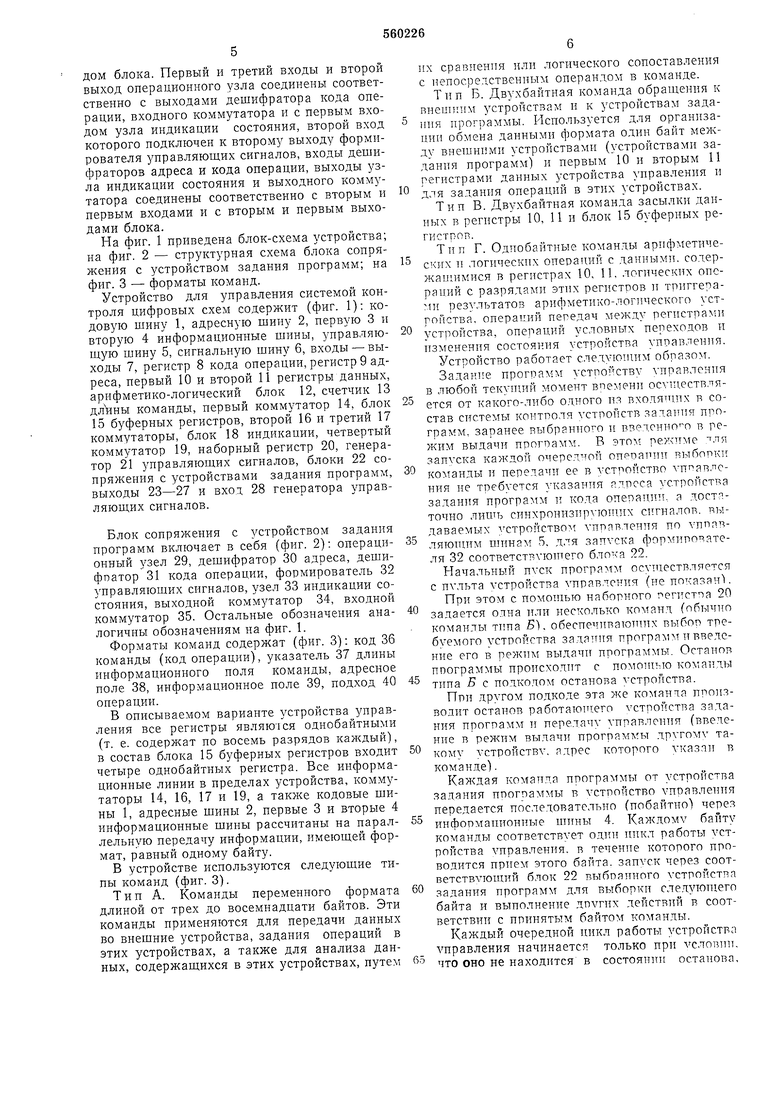

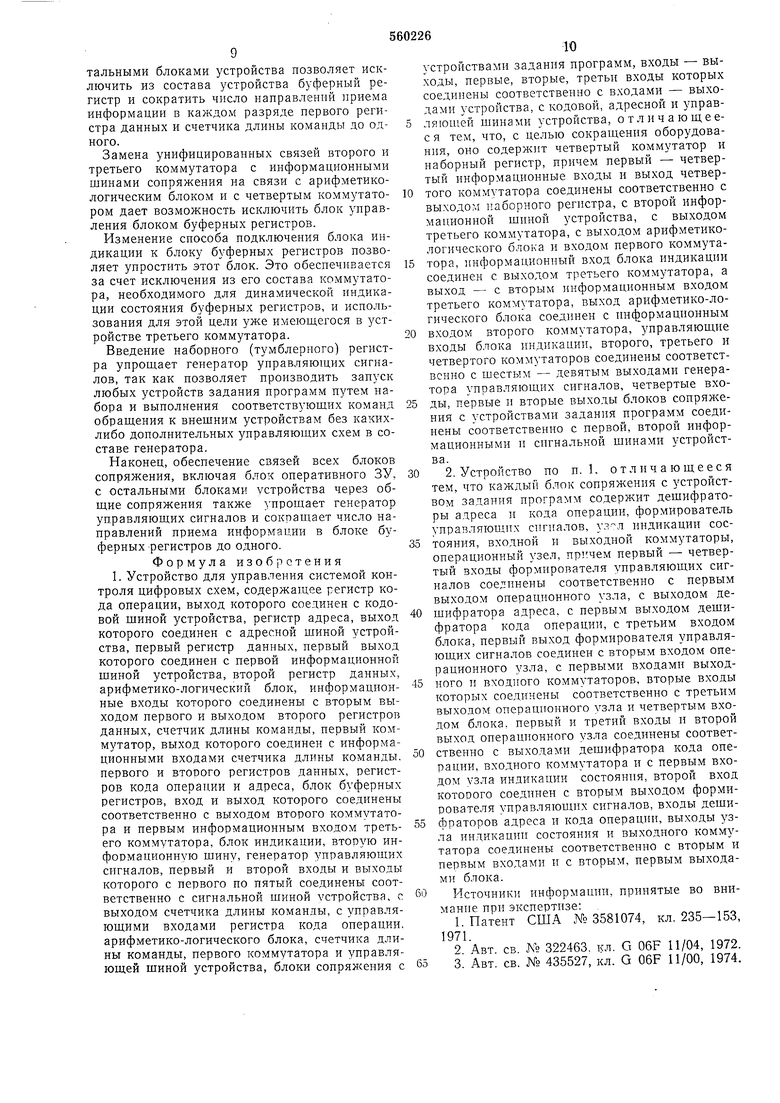

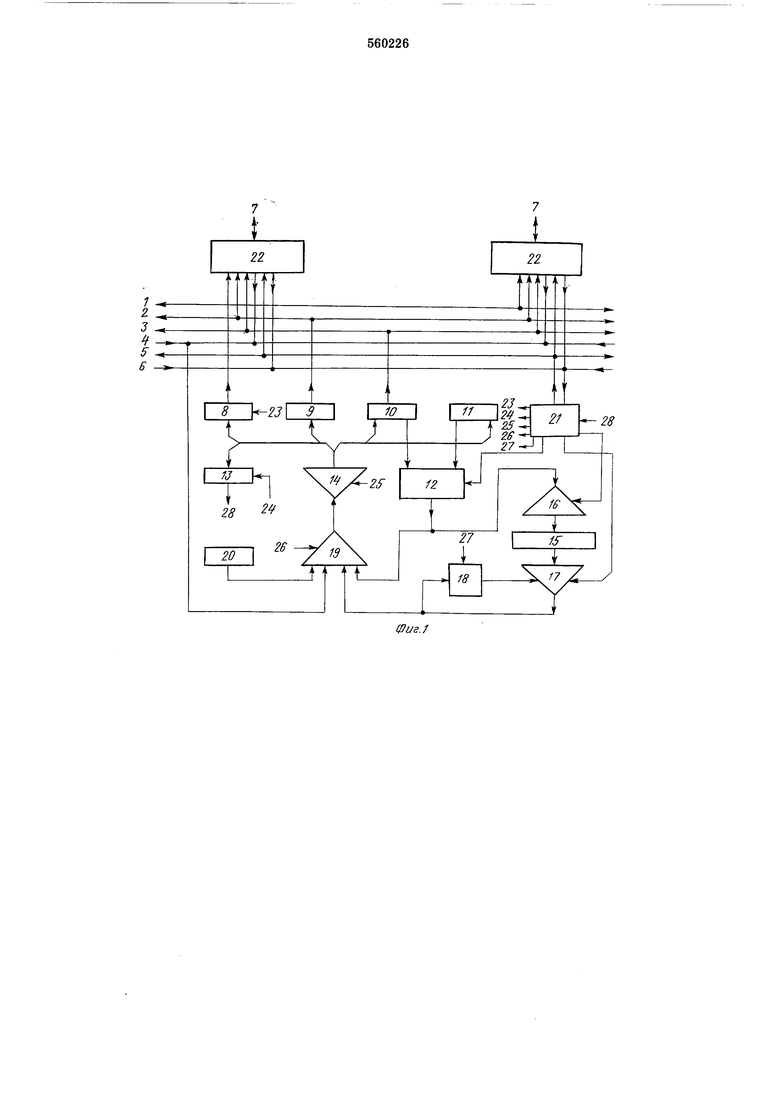

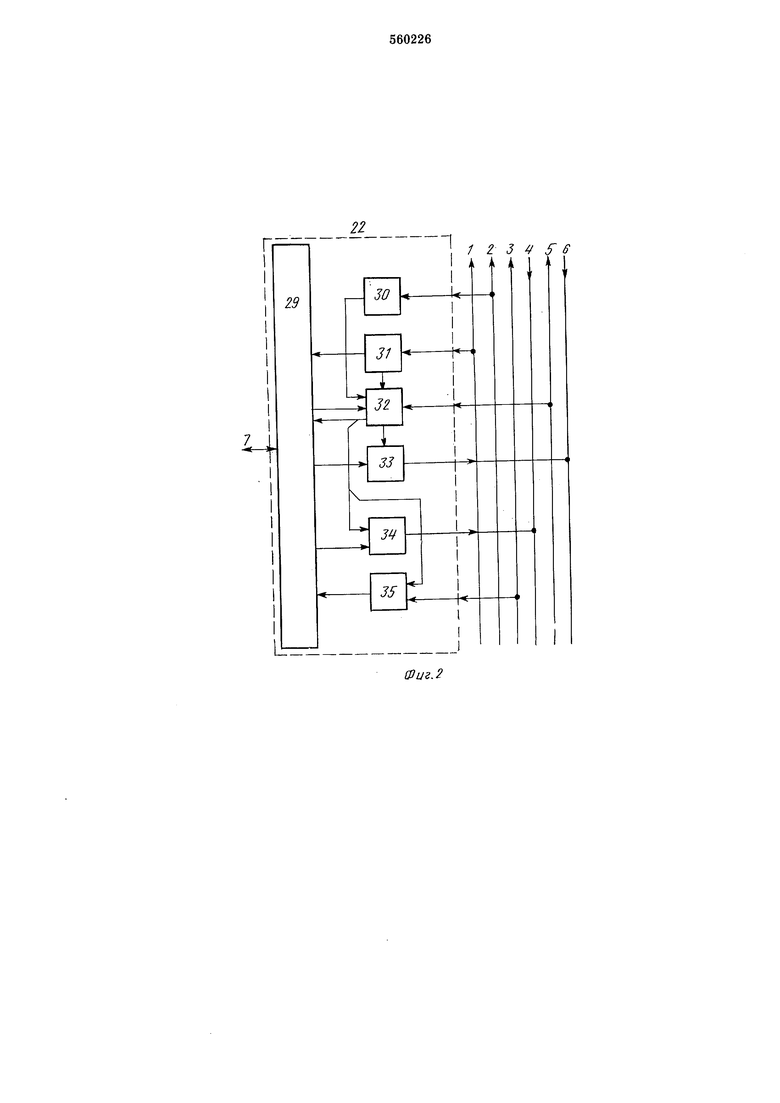

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - структурная схема блока сопряжения с устройством задания программ; иа фиг. 3 - форматы команд.

Устройство для управления системой контроля цифровых схем содержит (фиг. 1): кодовую шину 1, адресную шину 2, первую 3 н вторую 4 информационные шины, управляющую шину 5, сигнальную шину 6, входы - выходы 7, регистр 8 кода операции, регистр 9 адреса, первый 10 и второй 11 регистры данных, арифметико-логический блок 12, счетчик 13 длины команды, первый коммутатор 14, блок 15 буферных регистров, второй 16 и третий 17 коммутаторы, блок 18 индикации, четвертый коммутатор 19, наборный регистр 20, генератор 21 управляющих сигналов, блоки 22 сопряжения с устройствами задания програмл, выходы 23-27 и вход 28 генератора управляющих сигналов.

Блок сопряжения с устройством задания программ включает в себя (фиг. 2): операционный узел 29, дешифратор 30 адреса, дещифпатор 31 кода операции, формирователь 32 управляющих сигналов, узел 33 индикации состояния, выходной коммутатор 34, входной коммутатор 35. Остальные обозначения аналогичны обозначениям на фиг. 1.

Форматы команд содержат (фиг. 3): код 36 команды (код операции), указатель 37 длины информационного поля команды, адресное поле 38, информационное поле 39, подход 40 операции.

В описываемом варианте устройства управления все регистры являются о.днобайтными (т. е. содержат по восемь разрядов ), в состав блока 15 буферных регистров входит четыре однобайтных регистра. Все информационные линии в пределах устройства, коммутаторы 14, 16, 17 и 19, а также кодовые шины 1, адресные шины 2, первые 3 и вторые 4 информационные шины рассчитаны на параллельную передачу информации, имеющей формат, равный одному байту.

В устройстве используются следующие типы команд (фиг. 3).

Тип А. Команды переменного формата длиной от трех до восемнадцати байтов. Эти команды применяются для передачи данных во внешние устройства, задания операций в этих устройствах, а также для анализа данных, содержащихся в этих устройствах, путем

ИХ сравнения или логического сопоставления с непосредственным операндом в команде.

Тип Б. Двухбайтная команда обращения к внешним устройствам и к устройствам задания программы. Иснользуется для организации обмена данными формата один байт между внешними устройствами (устройствами задания программ) и первым 10 н вторым 11 регистрами данных устройства управления н

0 для задания операций в этих устройствах.

Тип В. Двухбайтная команда засылки данных в регистры 10, 11 и блок 15 буфериых регистров.

Тип Г. Однобайтные команды арифметиче5ских и логических операций с данными, содержащимися в регистрах 10, 11. .тогических операций с разрядами этих регистров и триггерами результатов арифметико-логического устройства, операций передач между регистрами

0 устройства, операций условных переходов и изменения состояния устройства управления.

Устройство работает следую.щим образом.

Задание программ устройству управления в любой текущий момент впеменн осуществля5ется от какого-либо одного из входятццх в состав системы КОНТРОЛЯ устройств задаптш проrpaMAt, заранее выбранного н введенного в режим выдачи программ. В этол; режттме т.пя запуска каждой очередной опеоатши выборки

0 комтанды н передачи ее в устройство л-ппавлсния не требуется указания адреса устройства задания программ и кода опепацнп., а достаточно лишь сипхрониз1 рующих сигналов, выдаваемых стройством лправлення по лпппв5ляюшим тинам 5. для запуска формнрочателя 32 соответствующего блока 22.

Начальный ПУСК программ осуществляется с пУльта устройства управления (не показан.

При этом с помошью наборного г егистпа 20

0 задается одна пли несколько команд (обычно команды типа Б, обеспечивающих выбоп требуемого устройства задания программ и введение его в режим выдачи программы. Останов программы происходит с помопп-ю команды

5 типа Б с подколом останова устройства.

При другом подкоде эта же комата производит останов работающего устройства задания программ и передачу управления (введение в режим вылачи программы другому та0кому УСТРОЙСТВУ, адрес которого указан в команде).

Каждая команда программы от устройства задания прогпаммы в УСТРОЙСТВО управленпя передается последовательно (побайтно) через

5 информационные шины 4. Каждому байту команды соответствует один цикл работы устройства управления, в течение которого проводится прием этого байта, запуск через соответствлчощий блок 22 выбпанпого устройства

0 задания программ для выборки следующего байта и выполнение дпугих действий в соответствии с ПРИНЯТЫМ байтом команды.

Каждый очередной цикл работы устройства управления начинается только при УСЛОПЦЦ.

5 что оно не находится в состоянии останова.

предыдущий цикл его работы закончен, закончена операция в выбранном устройстве задания программ по подготовке очередного байта команды, закончены операции во всех внешних устройствах, нет требования на останов по особому результату предыдущих оцераций.

После приема каждого байта комаиды в устройство управления изменяется соответствующим- образом состоящие счетчика 13 длины команды. Поэтому перед началом каждого очередного цикла устройства зарацее известно назначение байта команды, принимаемого в этом цикле.

В начале цикла генератор 21 устройства управления с помощью сигналов по ущравляюИ1ИМ щинам 5 обеспечивает запуск формирователя 32 соответствующего блока 22 для выдачи через выходной коммутатор 34 байта команды от заранее выбранного устройства задания программ на информационные шины 4. Далее этот байт передается через коммутатор 19 и коммутатор 14 либо в регистр 8 кода опеоацци, либо в регистр 9 адреса, либо в г егистр 10 данных, в зависимости от текущего состояния сечтчика 13. Байт команды типа Г и первые байты команд типов А, Б, В принимаются в регистр 8, вторые байты команд типов А, Б - в регистр 9 адреса, второй байт команды типа В и все байты информационного поля команд типа А - в регистр 10 данных.

После приема байта команды генератор 21 упоавляющих сигналов изменяет состояние счетчика 13 длины команды и через соответствующую шину 5 запускает операцию выборки следующего байта в выбранном устройстве задания программ. Если в рассматриваемом цикле в устройство управления был принят байт команды типа Г, либо второй байт команды типа Б или В, либо байт информационного поля команды типа А, то генератор 21 обеспечивает проведение операций, предписанных командой.

Основные операции устройства управления выполняются следующим образом.

В операциях, осуществляемых с помощью арифметико-логического блока 12, генератор 21 задает тил операции блоку 12, который производит эту операцию над данными в регистрах 10, 11.

Результат операции с выхода блока 12 передается через коммутаторы 19 и 14 в регистр 10. В операциях обмена данными между регистрами выполняется одна из следующих передач: из первого 10 или второго II регистров данных через арифметико-логический блок 12 и коммутатор 16 в заданный регистр блока 15, из заданного регистра блока 15 через коммутаторы 17, 19 и далее через коммутатор 14 в один из регистров данных (10, II); из наборного регистра 20 через коммутаторы 19 и 14 в один из регистров данных.

В операциях условных переходов генератор 21 опрашивает один из триггеров результатов арифметико-логического блока 12 (тот, котэрый указан в команде) и, если его состояние совпадает с заданным в команде, устанавливает соответствующий признак, три котором запрещается выполнение одной следующей команды программы или групп -: команд.

Операции, в которых участвуют находящиеся в режиме ожидания устройства задания программ, выполняются следующим образом. После приема команды типа Б в устройство управления кодовое и адресное ноля команды, содержащиеся в регистре 8 и в регистре 9 адреса, через кодовые (и адресные 2 шины оказываются доступны всем блокам 22. Блок 22, относящийся к адресуемому в команде устройству, с помощью дешифратора 30 адреса распознает свой адрес на щииах 2 и приводит в состояние готовности формирователь 32 управляющих сигналов, а дещифратор 31 определяет тип операции, которую должно выполнить устройство задания программ.

Далее по сигналам па управляющих щинах 5, выдаваемых генератором 21, приводится в действие формирователь 32 выбранного блока 22, который вырабатывает все необходимые управляющие сигналы для выполнения операции в устройстве или для приема данных из регистра 10 через первые информационные тины 3 и входной коммутатор 35. На время операции в устройстве задания программ узел 33 блока 22 этого устройства устанавливает сигнал занятости на сигнальной шине 6.

Если выполняемая команда предусматривает прием байта состояния или данных от выбранного устг1ойства задания программ, то по сигналу на заправляющей щине 5 формирователь 32 обеспечивает выдачу данных через выходной коммутатор 34 на вторую информационную ЩИНУ 4. Генератор 21 производит передачу этих данных через коммутаторы 19 и 14 в один из регистров данных (10, 11).

Атгалогичным образом исполняется команда типа 5 и в том случае, если она адресуется какому-либо исполнительному внещнему устройству.

При выполнении команд типа А прием байтов данных от указанного в команде BHeojHeго устройства осуществляется в регистр 11. После приема каждого очередного байта генепатор 21 с помощью заправляющей щины 5 запускает операцию во внещнем устройстве и параллельно, используя арифметико-логический блок 12, выполняет операцию сравнения или логического сопоставления данных регистра 11 и принятого в регистр 10 соответствующего байта информационного поля команды. Результат операции фиксируется триггерами результата блока 12 и затем может анализироваться с помощью команд условных переходов.

Отличительные признаки устройства обеспечивают лостижеггто поставленной цели изобретения - сокпащение оборудования - следующим образом.

Введение четвертого коммутатора и соответс- зуютцих спязей этого коммутатора с остальными блоками устройства позволяет исключить из состава устройства буферный регистр и сократить число направлений приема информации в каждом разряде первого регистра данных и счетчика длины команды до одного.

Замена унифицированных связей второго и третьего коммутатора с информационными шинами сопряжения на связи с арифметикологическим блоком и с четвертым коммутатором дает возможность исключить блок управления блоком буферных регистров.

Изменение способа подключения блока индикации к блоку буферных регистров позволяет упростить этот блок. Это обеспечивается за счет исключения из его состава коммутатора, необходимого для динамической индикации состояния буферных регистров, и использования для этой цели уже имеющегося в устройстве третьего коммутатора.

Введение наборного (тумблерного) регистра упрощает генератор управляющих сигналов, так как позволяет производить запуск любых устройств задания программ путем набора и выполнения соответствующих команд обращения к внешним устройствам без какихлибо дополнительных управляющих схем в составе генератора.

Наконец, обеспечение связей всех блоков сопряжения, включая блох оперативного ЗУ, с остальными блоками устройства через общие сопряжения также упрощает генератор управляющих сигналов и сокращает число направлений приема информации в блоке буферных регистров до одного.

Формула изобретения

1. Устройство для управления системой контроля цифровых схем, содержащее регистр кода операции, выход которого соединен с кодовой шиной устройства, регистр адреса, выход которого соединен с адресной щиной устройства, первый регистр данных, первый выход которого соединен с первой информационной щиной устройства, второй регистр данных, арифметико-логический блок, информационные входы которого соединены с вторым выходом первого и выходом второго регистров данных, счетчик длины команды, первый коммутатор, выход которого соединен с информационными входами счетчика длины команды, первого и второго регистров данных, регистров кода операции и адреса, блок буферных регистров, вход и выход которого соединены соответственно с выходом второго коммутатора и первым информационным входом третьего коммутатора, блок индикации, вторую информационную , генератор управляющих сигналов, первый и второй входы и выходы которого с первого по пятый соединены соответственно с сигнальной щиной устройства, v выходом счетчика длины команды, с управляющими входами регистра кода операции, арифметико-логического блока, счетчика длины команды, первого коммутатора и управляющей щиной устройства, блоки сопряжения с

устройствами задания программ, входы - выходы, первые, вторые, третьи входы которых соединены соответственно с входами - выходами устройства, с кодовой, адресной и управляющей щинами устройства, отличающеес я тем, что, с целью сокращения оборудования, оно содержит четвертый коммутатор и наборный регистр, причем первый - четвертый информационные входы и выход четвертого коммутатора соединены соответственно с выходом наборного регистра, с второй информационной щиной устройства, с выходом третьего коммутатора, с выходом арифметикологического блока и входом первого коммутатора, информационный вход блока индикации соединен с выходом третьего коммутатора, а выход - с вторым информационным входом третьего коммутатора, выход арифметико-логического блока соединен с инф ормащюнным

входом второго коммутатора, управляющие входы блока индикации, второго, третьего и четвертого коммутаторов соединены соответственно с шестым - девятым выходами генератора управляющих сигналов, четвертые входы, первые и вторые выходы блоков сопрял ения с устройствами задания программ соединены соответственно с первой, второй информационными ц сигнальной щинами устройства.

2. Устройство по п. 1, отличающееся тем, что каждый блок сопряжения с устройством задания программ содержит дещифраторы адреса н кода операции, формирователь управляющих сигналов, индикации состояния, входной и выходной коммутаторы, операционный узел, причем первый - четвертый входы формирователя управляющих сигналов соединены соответственно с первым выходом операционного узла, с выходом дещифратора адреса, с первым выходом дешифратора кода операции, с третьим входом блока, первый выход формирователя управляющих сигналов соединен с вторым входом операционного узла, с первыми входами выходного и входного коммутаторов, вторые входы которых соединены соответственно с третьим выходом операционного узла и четвертым входом блока, первый и третий входы и второй выход операционного уз.гта соединены соответственно с выходами дещифратора кода операции, входного коммутатора и с первым входом узла индикации состояния, второй вход которого соединен с вторым выходом формирователя управляющих сигналов, входы дещифраторов адреса и кода операции, выходы узла индикации состояния и выходного коммутатора соединены соответственно с вторым и первым входами и с вторым, первым выходами блока.

Источники информации, принятые во внимание при экспертизе:

1.Иатент США №3581074, кл. 235-153, 1971. 2. Авт. св. К° 322463. кл. G 06F 11/04, 1972.

3. Авт. св. № 435527, кл. G 06F 11/00, 1974.

Jff I J7 j JS

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для контроля программ | 1987 |

|

SU1418720A1 |

| Имитатор канала | 1985 |

|

SU1377857A2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Имитатор канала | 1987 |

|

SU1467555A1 |

Jff

o

J8

Авторы

Даты

1977-05-30—Публикация

1975-01-31—Подача