гистров, узел 9 указателя стека, счетчик 10 команд, управляющий регистр 11, узел 12 выбора регистра, .регистр 13 врем.енного хранения, буферную nanntb 14, регистр 15 буферной памяти, буферный регистр 16, буферный регистр 17 адреса, блок 18 дешифрации, тактовый генератор 19,

оперативную память 20, постоянную память 21, блок 22 индикации, блок 23 ввода информации, триггер 24, счетчик 25, элемент И-НЕ 26, триггер 27, элемент ИЛИ 28, кнопку 29 сброса данных, переключатели 30-32, шину 33 адреса, шину 34 обмена, гаину 35 данных, 1 шт.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

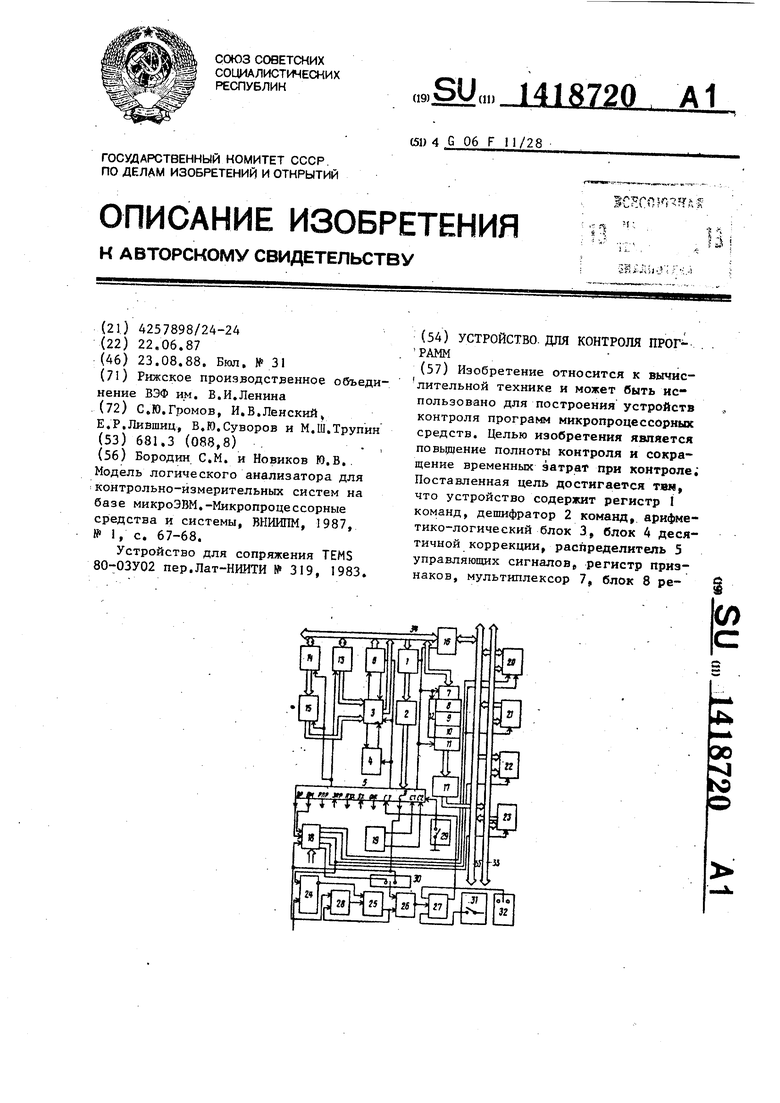

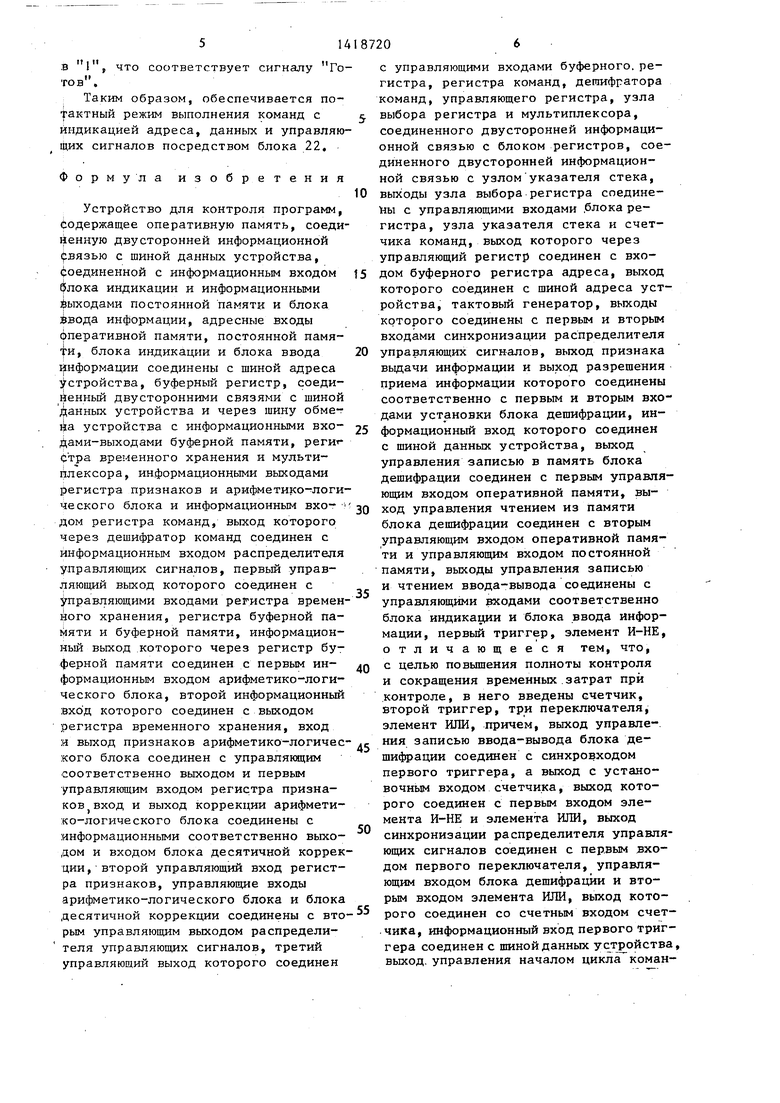

Изобретение относится к вычис лительной технике и может быть использовано для построения устройств контроля программ микропроцессорных средств. Целью изобретения является повьадение полноты контроля и сокращение временных затрат при контроле. Поставленная цель достигается твн, что устройство содержит регистр I команд, дешифратор 2 команд,, арифметико-логический блок 3, блок 4 десятичной коррекции, распределитель 5 управляющих сигналов, регистр признаков, мультиплексор 7, блок 8 ре

1

Изобретение относится к вычислительной технике, и может быть использовано для построения устройств контроля программ и может найти применение в качестве учебного микрокомпьютера.

Целью изобретения является повышение полноты контроля и сокращение временных затрат при контроле.

На чертеже представлена схема предлагаемого устройства.

Устройство содержит регистр 1 команд, дешифратор 2 команд, арифметико-логический блок 3, блок 4 десятичной коррекции, распределитель 5 управляющих сигналов, регистр 6 признаков, мультиплексор 7, блок 8 регистров, узел 9 указателя стека, счетчик 10 команд, управляющий регистр 11, узел 12 выбора регистра, регистр 13 временного хранения, буферную память 14, регистр 15 буферной памяти, буферный регистр 16, буферный регистр 17 адреса, блок 18 дешифрации, тактовый генератор 19, оперативную память 20, постоянную память 21, блок 22 индикации, блок 23 ввода информации, триггер 24, счетчик 25, элемент И-НЕ 26, триггер 27, элемент ИЛИ 28, кнопку 29 сброса данных, переключатели 30-32, шину 33 адресу, шину 34 обмена, шину 35 данных.

Устройство работает следующим образом.

При включении питания содержимое регистров блок 8 и счет-чика. 10 устанавливается произвольным образом, подачи на вход сброса СВР формирователя 5 сигнала высокого уровня посредством кнопки 29 в счетчик

10 записывается ноль. Работа синхронизируется генератором 19, Команды выполняются за несколько машинных

циклов в зависимости от длины команды и реализуемых операций, В первом цикле выполнения команды содержимое счетчика 10 записывается в регистр 11 и затем через регистр 17 выдается на

шину 33, Одновременно на шину 35 выдается управляющее слово и формируются сигналы: синхронизация С, ПМ - разрешение приема информации с шины данных, В Р - признак выдачи информации на шину данных. Под действием синхросигнала управляющее слово записывается в блок 18, В управляющем слове отражается текущее состояние устройства, происходит запись или

чтение, ввод или вывод, идет опера ция со стеком или обрабатывается ;i .прерывание, В соответствии с этим блок 18 состояний может вырабатывать на соответствующих выходах сигналы:

ПЧТ - чтение памяти, ПЗП - запись в.память, ВВЧТ - чтение ввода-вывода, ВВЗП - запись ввода-г-вывода. Ml - начало первого цикла команды. В данном случае отражено состояние Чтенив из памяти, в соответствии с

этим управляющим словом вырабатывается сигнал ПЧТ,

Под воздействием зтого слова первый байт команды, являющийся кодом операции, считывается из нулевой ячейки 21 памяти, поступает на шину 35 и через регистр 16 записывается в регистр 1, Далее код операции поступает на дешифратор 2, где происходит его декодирование, и декодированный сигнал воздействует на формирователь 5, Последний вырабатывает ;

314

либо внешние сигналы для чтения второго и третьего байтов команды и инициализации операций ввода-вывода, ли- бо вырабатывает управляющие сигналы, распространяющиеся по внутренней шине управления. Управляющие сигналы вырабатываются загцитньии в формирователе 5 микрокомандами. Каждой команде соответствует определенный набор микрокоманд. Арифметические и логические команды выполняются в блоке 3, Данные при этом размещаются в регистре 13 и регистре 15. Результат операции записывается в память 14 или поступает на шину 34. Блок 4 позволяет при необходимости осуществлять перевод содержимого памяти 1 4 из двоиуной в двоично-десятичную форму. Информация о результате выполнения команды заносится в регистр 6. Разряд Нуль регистра 6 устанавливается в 1 при нулевом результате, разряд Перенос при переполнении старшего разряда, разряд. Четность - при четном количестве единиц в байте, разряд Знак - при единичном значении старшего разряда, разряд Дополнительный перенос - при переходе 1 из младших четырех разрядов в старшие.

При вьтолнении команд пересылок и загрузки регистров формирователь 5 декодирует ту часть команды, в которой определен адрес регистра и передает по внутренней шине управления соответствующие управляющие сигналы на узел 12 и мультиплексор 7, и требуемый регистр блока 8 подключается к шине 34, через которую осуществляется передача информации. Если регистры используются для адресации памяти, то формирователь 5 вырабатываВТ сигналы, в соответствии с которыми информация из регистров пересылается в регистр 11 и оттуда через регистр 17 на шину 33, при этом в блок 18 записывается управляющее слово, определяющее режим работы с памятью. Аналогично выполняются и команды работы со стеком, В этом случае для адресации используется узел 9

Для обработки программы пользователя в потактном режиме необходимо посредством блока 23 ввести команду Старт программы с указанием на-; чального адреса программы, переключатель 32 перевести в положение ШГ,

8720

при этом на вход данных триггера 2 7 подается Лог.О для. формирования на выходе rppjrrepa 27 сигнала Не готов, в противном случае Лог. 1 для формирования сигнала готовности. Выбор величины шага осуществляется переключателем 30. При этом на вход записи триггера 27 коммутируется через элемент И-НЕ 26

Q либо сигнал Ml с блока 18, сигнализирующий о том, что происходит выборка первого байта команды и это соответ- ртвует выполнению первого (покоманд- ного) режима работы, либо синхросиг5 нал с формирователя 5 управляющих сигналов, что соответствует поэтапному выполнению программы. Перед передачей управления анализируемой программе в триггер 24 по сигналу ВВЗП, поQ ступающему с блока 18 на синхровход триггера 24, записывается Лог,1 с нулевого разряда О шины 35, при этом на вход установки счетчика 25 посту-, пает Лог.О, тем самым выход счет25 чика 25 (0,1,2) сбрасывается в О и Лог.О выхода счетчика 25 поступает на элемент ИЛИ 28, разрешая прохождение синхросигналов с формирователя 5. Таким образом, счетчик 25

0 получает возможность считать рабочие циклы выполнения команды, которые определяются синхросигналами,, поступающими с формирователя 5, По истечении шести рабочих циклов, а именцо столько продолжается выполнение команд , необходимый для перехода на обрабатываемую программу в автоматическом режиме, на выходе счетчика 25 появляется Лог.1, которая поступаQ ет на вход элемента ИЛИ 28, запрещая дальнейший счет, так как на выходе этой схемы будет постоянно присутствовать Лог.1, а не последовательность импульсов. По сигналу Ml в поg командном режиме по синхросигналу

в поэтапном режиме выполнения команды, поступающем на вход записи триггера 27, в триггер 27 записывается значение входа данных (в режиме ШГ - Лог.О) триггера 27 и с выхода этого триггера на вход формирователя 5 IT роступает сигнал Не готов, который переводит опер&ционное устройст- во (ОУ) в состояние ожидания. Из

р этого состояния ОУ выходит по положительному фронту короткого сигнала, .. поступающего с переключателя 31 на вход установки триггера 27. Тем самым выход триггера устанавливается

35

в 1 , что соответствует сигналу Го (I

тов.

Таким образом, обеспечивается по- фактный режим выполнения команд с индикацией адреса, данных и управляющих сигналов посредством блока 22,

Формула изобретения

Устройство для контроля программ, содержащее оперативную память, соединенную двусторонней информационной ({связью с шиной данных устройства, фоединенной с информационным входом флока индикации и информационными фыходами постоянной памяти и блока вода информации, адресные входы оперативной памяти, постоянной памя- фи, блока индикации и блока ввода 1 нформации соединены с шиной адреса Устройства, буферный регистр, соеди- йенный двусторонними связями с шиной данных устройства и через шину обме-г йа устройства с информационными входами-выходами буферной памяти, регит С тра временного хранения и мультиплексора, информационными выходами регистра признаков и арифметико-логического блока и информационным вхо- дом регистра команд, выход которого через дешифратор команд соединен с информационным входом распределителя управляющих сигналов, первый управляющий выход которого соединен с управляющими входами регистра времен його хранения, регистра буферной памяти и буферной памяти, информацион- ньй вькод которого через регистр буферной памяти соединен с первым информационным входом арифметико-логического блока, второй информационный вход которого соединен с выходом регистра временного хранения, вход и выход признаков арифметико-логического блока соединен с управляклцим соответственно выходом и первым управляющим входом регистра признаков J вход и выход коррекции арифметико-логического блока соединены с информационными соответственно выходом и входом блока десятичной коррекции, второй управляющий вход регистра признаков, управляющие входы арифметико-логического блока и блока десятичной коррекции соединены с вторым управляющим выходом распределителя управляющих сигналов, третий управляющий выход которого соединен

с управляющими входами буферного, регистра, регистра команд, дешифратора команд, управляющего регистра, узла выбора регистра и мультиплексора, соединенного двусторонней информационной связью с блоком регистров, соединенного двусторонней информационной связью с узлом указателя стека,

выходы узла выбора регистра спедине- toi с управляющими входами блока регистра, узла указателя стека и счетчика команд, выход которого через управляющий регистр соединен с входом буферного регистра адреса, выход которого соединен с шиной адреса устройства, тактовый генератор, выходы которого соединены с первым и вторым входами синхронизации распределителя

управляющих сигналов, выход признака вьщачи информации и выход разрешения приема информации которого соединены соответственно с первым и вторым входами установки блока дешифрации, информационный вход которого соединен с шиной данных устройства, выход управления записью в память блока дешифрации соединен с первым управляющим входом оперативной памяти, выход управления чтением из памяти блока дешифрации соединен с вторым управляющим входом оперативной памяти и управляющим входом постоянной памяти, выходы управления записью и чтением ввода-вывода соединены с управляющими входами соответственно блока индикации и блока ввода информации , первый триггер, элемент И-НЕ, отличающееся тем, что,

с целью повышения полноты контроля и сокращения временных.затрат при контроле, в него введены счетчик, второй триггер, три переключателя, элемент ИЛИ, причем, выход управле-. ния записью ввода-вывода блока дешифрации соединен с синхровходом первого триггера, а выход с устано- вочнь1М входом счетчика, выход которого соединен с первым входом элемента И-НЕ и элемента ИЛИ, выход синхронизации распределителя управляющих сигналов соединен с первым входом первого переключателя, управляющим входом блока дешифрации и вторым входом элемента ИЛИ, выход которого соединен со счетным входом счетчика, информационный вход первого триггера соединен с шиной данных уст р ойства, выход, управления началом цикла коман

7 14187208

ды блока дешифрации соединен с вто- вход готовности распределителя управ- рым входом первого, переключателя, вы ляющих сигналов соединен .с выходом ход которого соединен с вторым вхо- второго триггера, информационный дом элемента И-НЕ, выход которого вход которого, соединен с выходом соединен с синхровходом второго триг-третьего переключателя, первый и вто- гера, вход установки которого черезрой входы которого соединены с шина- второй переключатель соединен с ши-ми соответственно единичного и ну- .ной единичного сигнала устройства,левого потенциала устройства.

| Бородин С.М | |||

| и Новиков Ю.В. | |||

| Модель логического анализатора для контрольно-измерительных систем на базе микроэвм.-Микропроцессорные средства и системы, ВНИИПМ, 1987, № 1, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

Авторы

Даты

1988-08-23—Публикация

1987-06-22—Подача