1

Изобретение относится к вычислительной технике и может быть использовано для автоматической проверки функционирования и нахоледения неисправностей в цифровых системах и устройствах обработки информации.

Известно устройство для автоматического нахождения неисправностей в схемах, содержащее постоянный запоминающий блок, блок управления, счетчик команд, блок вывода информации, входные и выходные коммутаторы, блок сравнения и блок индикации.

Недостатком известного устройства является сложность и прямая зависимость роста затрат оборудования при увеличении количества выходов и узлов в .проверяемой системе.

Целью изОбретения является повышение надежности работы устройства.

Поставленная цель достигается тем, что в него введены регистр приема информации, сумматор, схемы «ИЛИ и схемы «И, причем контролируемые вы.ходы проверяемой системы, подключенные к выходному коммутатору, соединены со входами первой схеады «ИЛИ, выход которой подключен к первым входам третьей и четвертой схем «ИЛИ, а также через первую схему «И и вторую схему «ИЛИ соединен со входом регистра приема, упра1вляющий вход которого подключен к одному из выходов блока управления, а выход - ко входу сумматора и к первому

входу второй схемы «И, второй вход которой соединен с выходом блока управления, выход второй схемы «И через третью схему «ИЛИ подключен к одному из входов блока сравнения, два других входа которого соединены с блоком управления и блоком вывода информации, а выход - с блоком индикации и одним из вы.ходав блока вывода информации, два других выхода которого подключены к входному коммутатору и второму входу четвертой схемы «ИЛИ, а входы - к блоку .управления и постоянному запоминающему блоку, соединенному с блоком правления, блоком индикации и счетчиком команд, выходы

блока управления соединены с блоком индикации, входным коммутатором, сумматором, вторым входом первой схемы «И и выходным коммутатором, выходы входного коммутатора подключены ко входам проверяемой

системы.

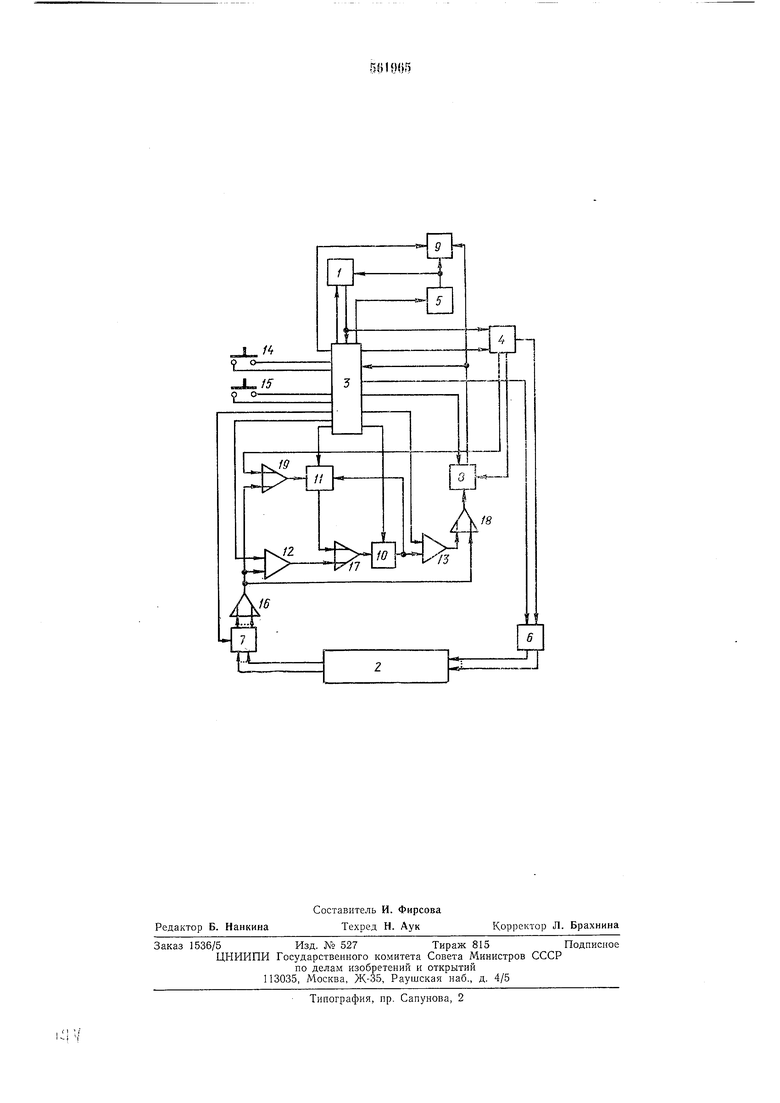

Принципиальная схема предлагаемого устройства представлена на .чертеже.

Устройство для обнаружения неисправностей цифровых систем содержит постоянный

запоминающий блок 1, предназначенный для хранения программы проверок контролируемой системы 2. Его информационные выходы связаны с блоком управления 3 и блоком 4 вывода информации. Блок 3 управляет работой остальных блоков и схем устройства в

Ьбответствий с программой проеерок, залисанной в ПОСТОЯНН01М запоминающем блоке 1. Для этого выходы блока 3 связаны с управляющими входами nOiCTOHHHoro запоминающего блока 1, блока 4 вывода информации, счетчика 5, предназначенного для организации последовательной выборки кнформа-цйи из постоянного запоминающего блока 1; коммутатора 6 входных шин (входного коммутатора), овязаяиого с блоком вывода информации, выходного коммутатора 7, блока сравнения 8, служащего для сравнения информации, приходящей из проверяемой системы 2, с эталонной информацией, поступающей через блок 4 вывода информации из постоянного запоминающего блока 1; блока индикации 9, предназначенного для высвечивания в двоичном коде местонахождения неисправности, информационные входы которого соединены с выходами счетчика команд 5, а другой упра1вляющий вход связан с выходом блока сравнения 8; регистра приема 10, служащего для приема и суммирования информации системы 2, одноразрядного сумматора 11, предназначенного для суммирования по модулю 2, где п - число разрядов регистра приема 10, информации из постоян.ного запоминающего блочка 1 или проверяемой системы 2, первой схемы «И 12, второй схемы «И 13.

Входы блока управления 3 соединены с выходом блока сравнения 8, с выходами кнопки «Пуск 14, служащей для запуска устройства, и кнопки «Сброс 15, предназначенной для приведения предлагаемого устройст1ва в нулевое состояние. Контролируемые выходы проверяемой системы 2, управляемые выходным коммутатором 7, связаны со входо1М первой схемы «ИЛИ 16, выход которой через первую схему «И 12 и вторую схему «ИЛИ

17,второй вход которой соединен с выходом сумматора И, связан со входом регистра приема 10. Выход регистра приема 10 соединен с одним из входов сумматора Ни через вторую схему «И 13 и третью схему «ИЛИ

18,второй вход которой связан с первой схемой «ИЛИ 16, подключен ко входу блока сравнения 8. Втодой вход сумматора 11 связане с выходом четвертой схемы «ИЛИ 19, один вход которой соединен с выходом первой схемы «ИЛИ 16, а второй - с одним из выходов блока вывода информации.

Работает устройство следующим образом.

При нажатии кнопки «Пуск начинается списывание информации из ячейки постоянного занОМинающего блока 1, адрес которой указан в счетчике, команд 5. Информация из постоянного запоминающего блока поступает в блок управления 3 и блок 4 вывода информации, из которого по входным шинам, управляемым входным коммутатором 6, в проверяемую систему 2 поступает последовательность входных Двоичных сигналов.

При испра1вности проверяемой системы 2 каждой последовательности входных двоичных сигналов соответствует последовательность онределенных выходных двоичных сигналов, вырабатываемых определенной схемой проверяемой системы 2. При каждой посылке

последовательности входных двоичных сигналов опрашивается состояние только одной выходной шины и производится сравнение последовательности выходных двоичных сигналов с эталонной последовательностью.

Каждой эталонной последовательности соответствует определенная схема в проверяемой системе 2 и определенное значение счетчика команд 5. Тем самым устанавливается местонахождение неисправности в проверяемои системе.

Информация из проверяемой системы 2 через выходной коммутатор 7 поступает на первую схему «ИЛИ 16, с выхода которой через третью схему «ИЛИ 18 поступает на вход

блока сравнения 8, где при наличии сигнала на управляющем входе производится поразрядное сравнение с эталонной последовательностью выходных двоичных сигналов, поступающей из постоянного запоминающего блока 1 через блок 4 вывода информации. При наличии сигнала на управляющем входе первой схемы «И 12 и управляющем входе регистра приема 10, информация с выхода первой схемы «ИЛИ 16 через первую схему

«И и вторую схему «ИЛИ 17 поступает на вход регистра приема 10.

В конце цикла приема на регистре приема находится последовательность выходных ДВОИЧ1НЫХ сигналов, соответствующая данной

последовательности входных двоичных сигналов.

При наличии сигнала на управляющем входе второй схемы «И 13 информация с регистра приема 10 через вторую схему «И 13 и

третью схему «ИЛИ 18 поступает на вход блока сравнения 8, где производится поразрядное сравнение с эталонной последовательностью выходных двоичных сигналов. Сигнал несравнения, вырабатываемый блоком сравнения 8, воздействует на блок управления 3 и блок индикации 9, по которому производится останов устройства и высвечивание содержимого счетчика команд 5, указывающего местонахождение неисправности в проверяемой

системе 2. При нажатии кнопки «Пуск блок индикации обнуляется и производится дальнейшая проверка системы 2.

Для полной проверки некоторых схем необходимо k раз производить выдачу определенных последовательностей входных двоичных сигналов в столько же раз производить сравнение информации, приходящей по какой-либо одной из выходных шин, с эталонными последовательностями выходных двоич

ных сигналов, соответствующих определенной схеме с проверяемой системе 2.

В этом случае для сокращения объема памяти постоянного запоминающего блока производится суммирование по модулю 2 информации, приходящей из проверяемой сиетемы 2. Информация, являющаяся реакцией проверяемой системы на посылку первой последовательности входных двоичных сипналое, с выхода первой схемы «ИЛИ через первую схему «И и вторую схему «ИЛИ записывается на регистр приема 10. При последующем приеме информа:ции из проверяемой системы первая схема закрывается, и информация с выхода первой схемы «ИЛИ через четвертую схему «Или поступает на вход одноразрядного сумматора, на второй вход которого поступает информация с выхода регистра приема 10. Результат поразрядного суммирования через вторую схему «ИЛИ поступает на вход регистра приема. После п сдвигов на регистре приема находится сумма первой и второй последовательностей выходных двоичных сигналов. Данная операция повторяется k раз. Затем информация с регистра приема через вторую схему «И и третью с.хему «ИЛИ поступает на вход блока сравнения, на второй вход которого поступает эталон«ая сумма.

Правильность записи информации в постоянном запоминающем блоке также проверяется нутем суммирования по модулю 2 и последующим сравнением с эталонной суммой. При этом информация последовательно считывается нз каждой ячейки постоянного запоминающего блока и через блок вывода информации и четвертую схему «ИЛИ ностуиает на вход сумматора, где осуществляется поразрядное суммирование с информацией, находящейся в регистре приема.

Формула изобретения

Устройство для обнаружения неисправностей цифровых систем, содержащее постоянный запоминающий блок, блок управлений, счетчик команд, блок вывода информации, входные и выходные коммутаторы, блок сравнения и блок индикации, отличающееся тем, что, с целью повышення надежности работы устройства, в него введены регистр приема информании, сумматор, с.хемы «ИЛИ и схемы «И, причем контролнруемые выходы проверяемой системы, подключенные к

выходному коммутатору, соединены со входами первой схемы «ИЛИ, выход которой подключен к первым входам третьей и четвертой схем «ИЛИ, а также через первую схему «И и вторую схему «ИЛИ соединен

со входом регистра приема, управляющий вход которого подключен к одному из выходов блока управления, а выход - ко входу сумматора и к первому входу второй схемы «И, второй вход которой соединен с выходом

блока правления, выход второй схемы «И через третью схему «ИЛИ подключен к одному из входов блока сравнения, два других входа которого соединены с блоком управления и блоком вывода информации, а выход-

с блоком индикации и одним из выходов блока вьгвода информации, два других выхода которого подключены к входному коммутатору и второму входу четвертой схемы «ИлИ, а входы - к блоку управления и постоянпому запомннаюи1,ему блоку, соеднненпому с блоком унравлення, блоком индикацни и счетчиком команд, выходы блока унравления соединены с блоком индикации, входным коммутатором, сумматором, вторым входом иервой схемы «И и выходным коммутатором, выходы входного коммутатора подключены ко входам проверяемой системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей цифровых систем | 1979 |

|

SU949659A2 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля дискретных объектов | 1978 |

|

SU728130A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

Авторы

Даты

1977-06-15—Публикация

1973-01-09—Подача