Изобретение отк сится к области цифровой вычислительной техники, в частности к автоматизированньм сйстб мам контроля цифровых устройств. Известны устройства для контраля цифровых блоков, работающие по принципу контроля функционирования блока заключающемуся в том, что на входы контролируемых блоков подается после довательность входных наборов и выходные значения сигналов сравнйва- ются с эталонными наборами. Известное устройство 1 содержит запоминающее устройство для хранени тестов, регистр теста; устройство записи информации из запоминающего устройства в регистр теста, формирователи входных и выходных сигналов, коммутационное устройство, устройство сравнения и осуществл Гет контроль путем подачи из запоминающего устройства поел адов ательности входных наборов на входы контролируемого устройства через устройство записи информации, регистр тест формирователи выходных сигналов и коммутационное устройство и сравнения с эталоном выходных значений сигналов, поступающих с контролируемого устройства через входные формирователи. Недостатком этого устройства является невозможность конт1эолн устройств, имеющих число контактов, превышающее йсло раэ ндов регистра теста, без увеличения числа его разрядов. Известно также устройство 2, содержащее ПбСтоянный запоминающий блок, блок ввода информации, вхсщные и исходные коммутаторы, блок йравнёнйя и блок индикации, регистр приема информации, сумматор, схемы И и схемы ИЛИ, которое обнар5 нвает неисправности цифровых систем, подавая входные сигналы из постоянного запоминающего блока с помощью блока управления по адресу, полученному из счетчика команд, чеЕ1ез блок ввода информации и входной коммутатор и сравнивая с эталоном полученную от контролируемого устройства информацию . Недостатком устройства является необходимость увеличения разрядности постоянного запоминающего блока, блока сравнения, блока индикации при контроле устройств с числом контактов, превышающим разрядность известного устройства. Устройство .3 наиболее .близко предлагаемому по технической сущности и содержит блок ввода, блок памяти, коммутатор, блок сравнений, блок управления, причем первый выхо блока ввода соединен с первым входом блока памяти, первый и второй выходы блока управления соединены соответственно с входом блока ввода и вторым входом блока памяти, первый и второй выходаа блока памяти соедийёны Ьоответственно с первым входом коммутатора и с первым входом блока сравнения, первый и второй .входы . блока управления соединенысоответственно с выходом блока сравнения и вторым выходом блока ввода, третий и четвертый выходы блока управления соединены соответственно с вторым входом блока сравнения и вторым входом коммутатора.

Контроль в данном устройстве осуществляется подачей на входы контролируемых цифровых блоков последова тельности входных наборов, считываемых из блока памяти, сравнения значений выходных сигналов, образующихся на выходах контролируемых блоков с наборами, считанными из блока памяти , Выявление блоком сравнения неравенства хотя бы при одном сравнении свидетельствует о неисправности в контролируемом цифровом блоке. НедЬста тком этого устройства является невозможность контроля цифровых блоков, число контактов которых п;ре.вышает разрядность блока памяти.

Целью изобретения яйляется раоиирение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство для контроля дискретных объектов, содержащее последовательно соединенные,блок ввода, блок памяти и первый коммутатор, а также блок управления, выхОДН которого соединены с управляющими входами блока ввода, --блока памяти, блока сравнения и первого коймутатора, а входы - с управляющими выходами блока ввода и блока сравнения, первый вход которого подключен к второму выходу блока памяти, введены многовходовой элемент ИЛИ и второй коммутатор, управляющий вход которого соединен с соответствующим выходом блока управления, первый выход - с вторым входом блока сравнения, а второй ВыхОд - с пёрвыми входами многовходовбго элемента ИЛИ, вторыми входами подключенйого к выходу первого коммутатора.

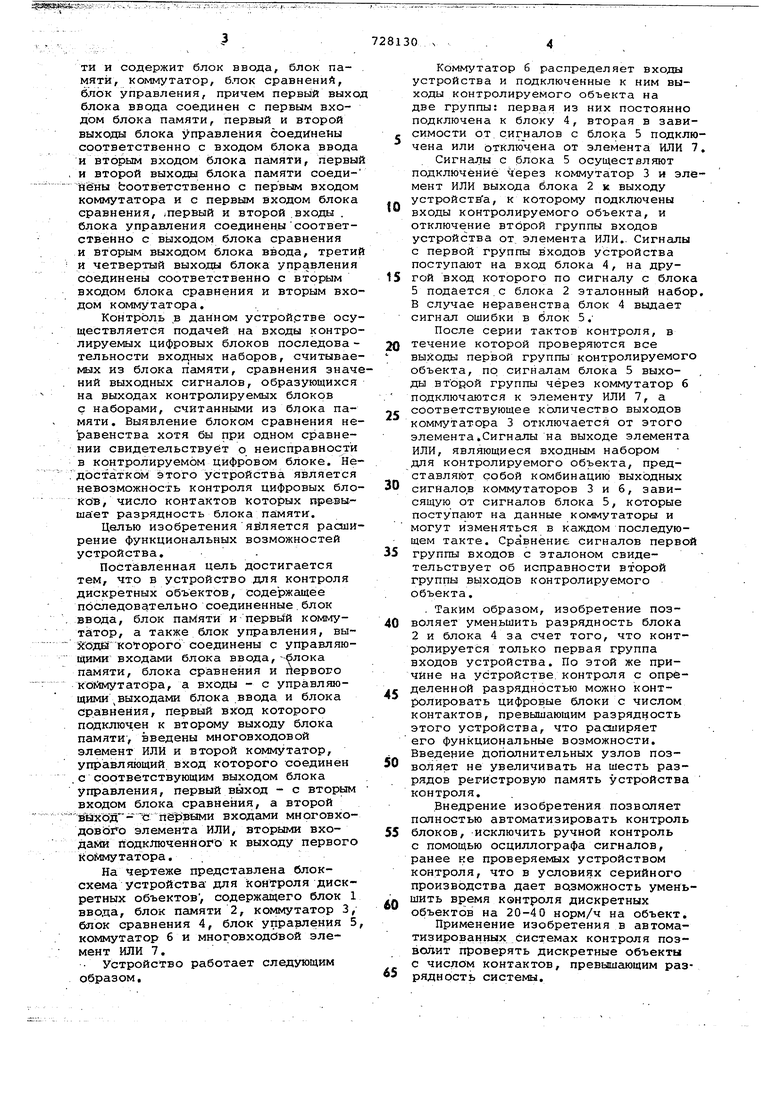

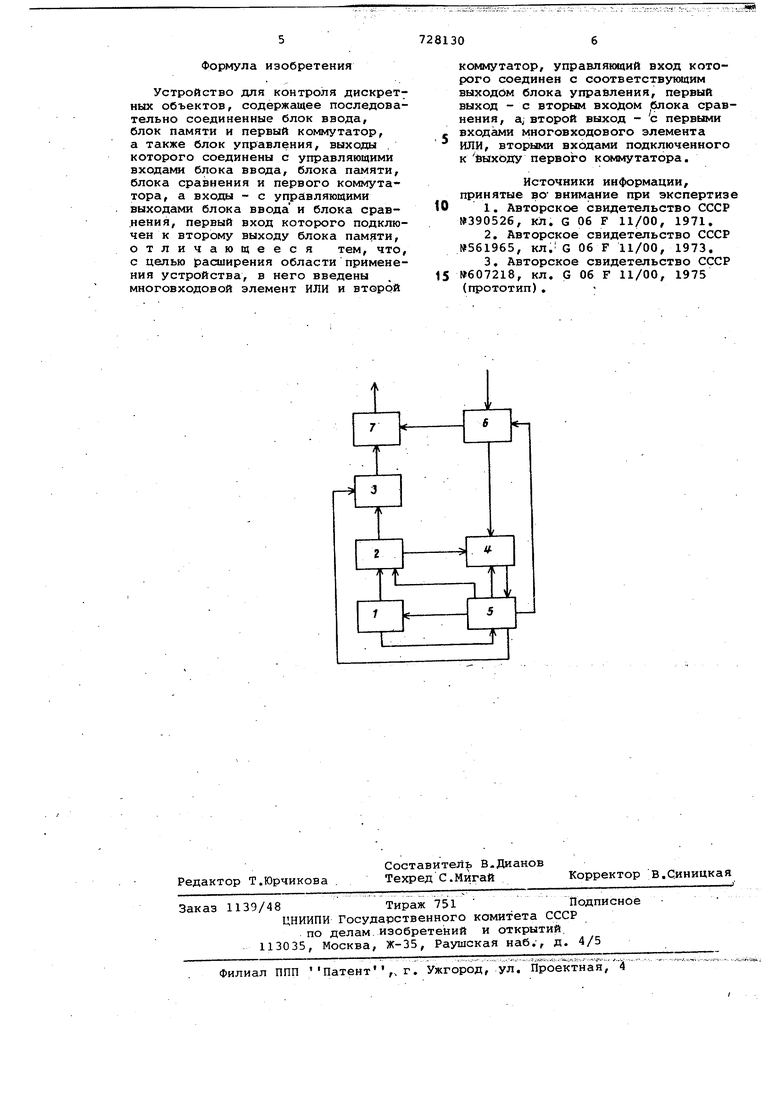

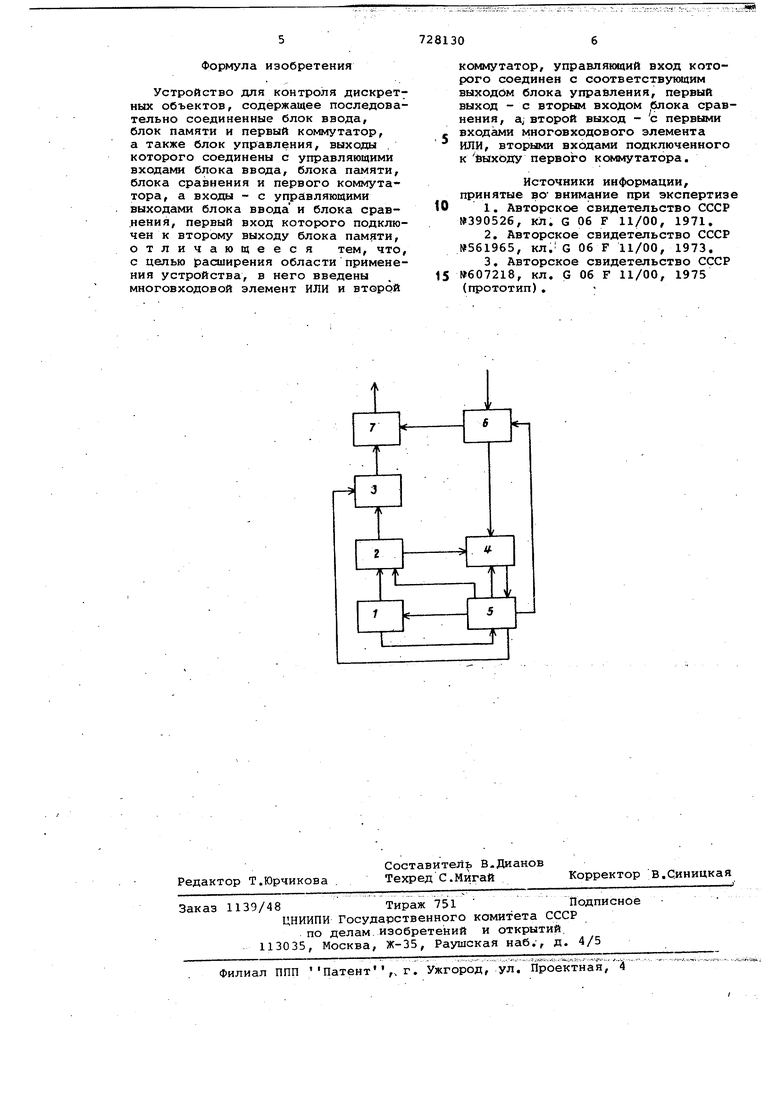

На чертеже представлена блоксхема устройства для контроля дискретных объектов , содержащего блок 1 ввода, блок памяти 2, коммутатор 3, блок сравнения 4, блок управления 5 коммутатор 6 и многовходовой элемент ИЛИ 7.

Устройство работает следующим образом.

Коммутатор 6 распределяет входы устройства и подключенные к ним выходы контролируемого объекта на две группы: первая из них постоянно подключена к блоку 4, вторая в зависимости от сигналов с блока 5 подклчена или отключена от элемента ИЛИ

Сигналы с блока 5 осуществляют подключение через коммутатор 3 и элмент ИЛИ выхода блока 2 к выходу устройства, к которому подключены входы контролируемого объекта, и отключение второй группы входов устройства от элемента ИЛИ.. Сигналы с первой группы входов устройства поступают на вход блока 4, на другой вход которого по сигналу с блок 5 подается с блока 2 эталонный набо В случае неравенства блок 4 вьщает сигнал ошибки в блок 5.

После серии тактов контроля, в течение которой проверяются все выходы первой группы контролируемог объекта, по сигналам блока 5 выходы второй группы через коммутатор 6 подключаются к элементу ИЛИ 7, а соответствующее количество выходов коммутатора 3 отключается от этого элемента Сигналы на выходе элемента ИЛИ, являющиеся входным набором для контролируемого объекта, представляют собой комбинацию выходных сигналов коммутаторов 3 и б, зависящую от сигналов блока 5, которые поступают на данные коммутаторы и могут изменяться в каждом последующем такте. Сравнение сигналов перво группы входов с эталоном свидетельствует об исправности второй группы выходов контролируемого объекта.

. Таким образом, изобретение позволяет уменьшить разрядность блока 2 и блока 4 за счет того, что контролируется только первая группа входов устройства. По этой же причине на устройстве/контроля с определенной разрядностью можно контролировать цифровые блоки с числом контактов, превышающим разрядность этого устройства, что расширяет его функциональные возможности. Введение дополнительных узлов позволяет не увеличивать на шесть разрядов регистровую память устройства контроля.

Внедрение изобретения позволяет полностью автоматизировать контроль блоков, исключить ручной контроль с помощью осциллографа сигналов, ранее ке проверяемых устройством контроля, что в условиях серийного производства дает возможность уменьшить время контроля дискретных объектов на 20-40 норм/ч на объект.

Применение изобретения в автоматизированных системах контроля позволит проверять дискретные объекты с числом контактов, превышающим разрядность системы.

Формула изобретения

Устройство для контроля дискретных объектов, содержащее последовательно соединенные блок ввода, блок памяти и первый коммутатор, а также блок управления, выходы которого соединены с управляющими входами блока ввода, блока памяти, блока сравнения и первого коммутатора, а входы - с управляющими выходами блока ввода и блока срав.нения, первый вход которого подключен к второму выходу блока памяти, отличающееся тем, что, с целью расширения области применения устройства, в него введены многовходовой элемент ИЛИ и второй

коммутатор, управляющий вход которого соединен с соответствующим выходом блока упрайления, первый выход - с вторым входом «5лока сравнения, aj второй выход - с первыми входами многовходового элемента ИЛИ, вторыми входами подключенного к йыхоДу первого коммутатора.

Источники информации, принятые во- внимание при экспертизе

0

1.Авторское свидетельство СССР №390526, кл. G 06 F 11/00, 1971,

2.Авторское свидетельство СССР №561965, кл. G 06 F 11/00, 1973.

3.Авторское свидетельство СССР 5 №607218, кл. G 06 F 11/00, 1975

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных объектов | 1982 |

|

SU1026143A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Тестер контроля и диагностики электронных модулей | 1986 |

|

SU1396099A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1012265A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

Авторы

Даты

1980-04-15—Публикация

1978-09-21—Подача