, второго триггера, второй вход которо го соединен с выходом пятого дешифратора, выхода элементов И группы и выходы первого и второго элементов И , образуют информационньй выход устройства, блок сопряжения содержит два узла согласования, два регистра сдвига, два регистра адреса, два приемопередатчика, дешифратор управляющих слов, два узла выходных усилителей, причем информационные входы первого и второго УЗЛОВ согласования соединены с информационным выходом блока памяти, управляющий вход второго узла согласования соединен с соответствующим вькодом микроприказов блока управления, выход первого узла согласования соединен с входом регистра сдвига, соединенного двухсторонней связью с первым приемопередатчиком, линией связи соединенным с вторым приемопередатчиком, двухсторонней связью соединенным с вторым регистром сдвига, первьй выход которого соединен с информационным входом первого регистра адреса, управляющий вход которого соединен с соответствующим выходом второго приемопередатчика, а выход - с входом дешифратора управляющих слов, второй выход второго регистра сдвига соединен с входом первого блока выходных усилителей, выход которого соединен с входами первого и второго блоков задания входных воздействий, соединенных также с вькодом дешифратора управляющих слов, выходы первого и второго блоков задания входных воздействий соединены с соответствующими

входами первого и второго коммутйторов, причем второй коммутатор соединен двухсторонней связью с эталон- Hbw блоком, выходы первого и второго коммутаторов соединены с информационным входом второго регистра сдвига блока сопряжения, в котором выход первого регистра сдвига через второй блок выходных усилителей соединен с входом блока сравнения, а выход второго блока согласования соединен с входом второго регистра адреса , информационный выход которого соединен с соответствующим входом

первого регистра сдвига, управлянлций выход второго регистра адреса соединен с соответствующим входом первого приемопередатчика, при этом блок управления содержит генератор тактовых импульсов, память микроопераций, дешифратор микроопераций, сумматор и регистр сдвига, причем выходы генератора тактовых импульсов соединены с тактовыми входами дешифратора микроопераций, регистр сдвига и памяти микроопераций, выход которой соединен с информационным входом дешифратора микроопераций, выходы которого соединены с управляющими входами сумматора и регистра сдвига и являются выходами микроприказов блока управления, первый и второй разрядные входы регистра сдвига являются первым и

вторым входами логических условий блока управления, выход сумматора и информационный- вход регистра сдвига

соединены между собой И образуют входвыход блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1241241A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ДИАГНОСТИКИ ДИСКРЕТНЫХ ОБЪЕКТОВ, содержащее блок ввода, блок памяти, эталонный блок, блок управления, блок сравнения, блок анализа места неисправности и первый коммутатор, причем выход блока ввода соединен с информационным входом блока памяти, соединенного двухсторонней связью с первым входом-выходом блока управления, выходы микроприказов которого соединены с управляющими входами блока ввода и блока сравнения, выход несравнения которого соединен с первым входом логических условий блока управления, первый коммутатор соединен двухсторонней связью с контролируемым объектом, выход равенства блока сравнения соединен с первым входом блока анализа месТа неисправности, . второй вход которого, соединен с соответствующим выходом микроприказов блока управления, блок анализа места неисправности содержит регистр, схему сравнения, триггер, два элемента И, отличающееся тем, что, с целью повышения точности диагностирования, устройство содержит второй коммутатор, два блока задания входных воздействий и блок сопряжения, а в блок анализа места неисправности введены пять дешифраторов, пять регистров, второй триггер и группа элементов И, причем первый вход блока анализа места неисправности соединен с входами первого и второго дешифраторов, выходы первого дешифратора соединены с управляющими входами с первого по шестой регистров, информационные входы которых и входы третьего, четвертого и пятого дешифраторов соединены с информационным выходом блока памяти, выходы, первого, второго, третьего, пятого и шестого регистров и второй вход блока анализа места неисправности соединены соответственно с первыми входами элементов И группы, вторые входы которых соединены с выходами второго дешифратора, выходы третьего и четвертого дешифраторов соединены ( соответственно с первым входом пер СП вого триггера и первыми входами первого и второго элементов И, вторые О5 входы которых соединены соответственно с первым и вторым выходами перво- го триггера, второй вход которого соединен с выходом второго триггера и с вторым входом логических условий блока управления, причем в блоке анализа места неисправности выходы третьего и четвертого регистров соединены с первым и вторым входами схемы сравнения, третий вход которой соединен с соответствующим выходом дешифратора, а выход - с первым входом

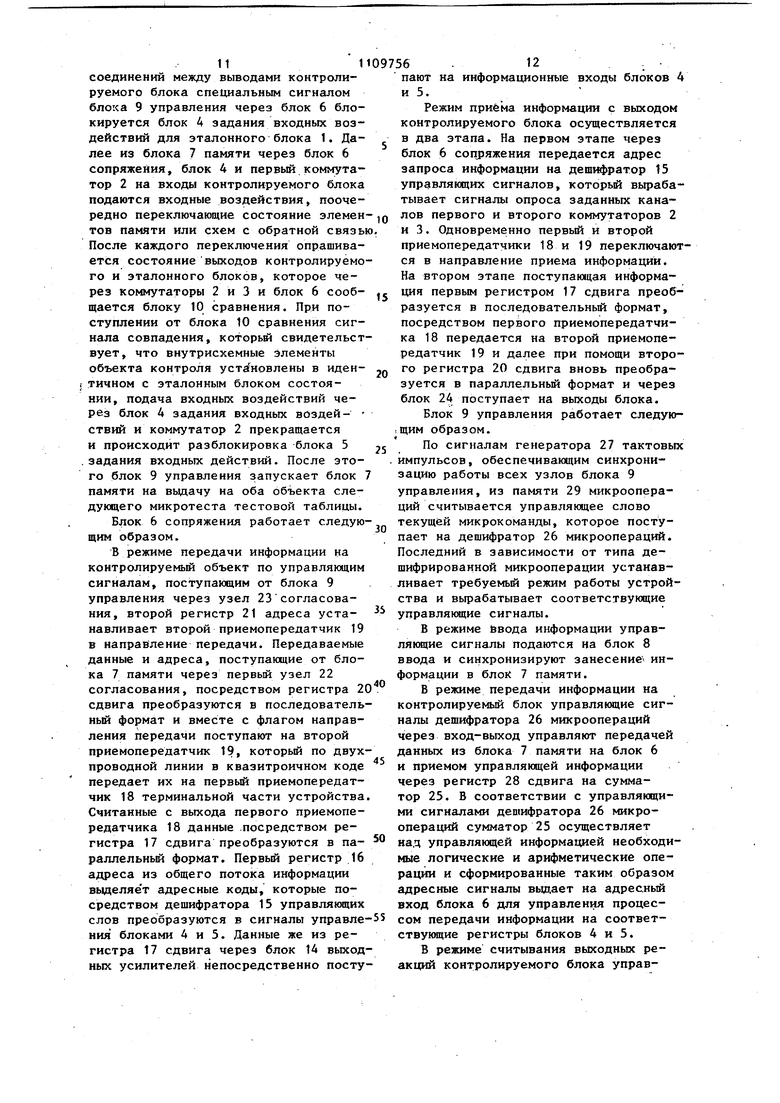

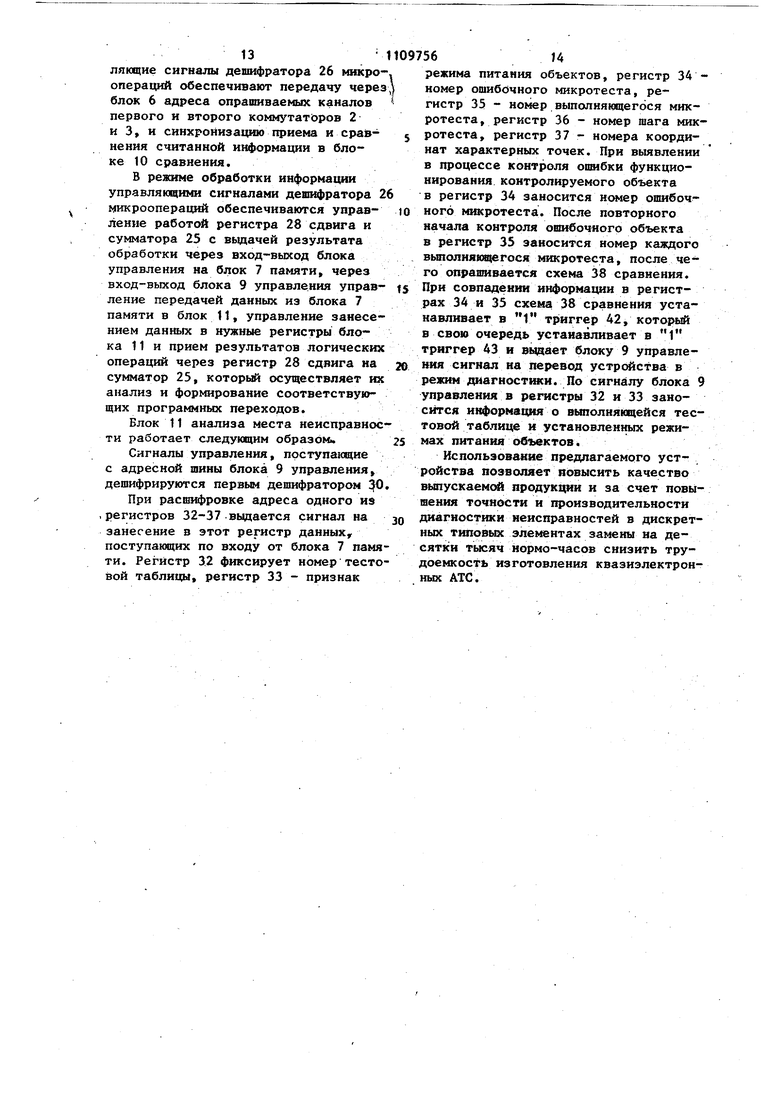

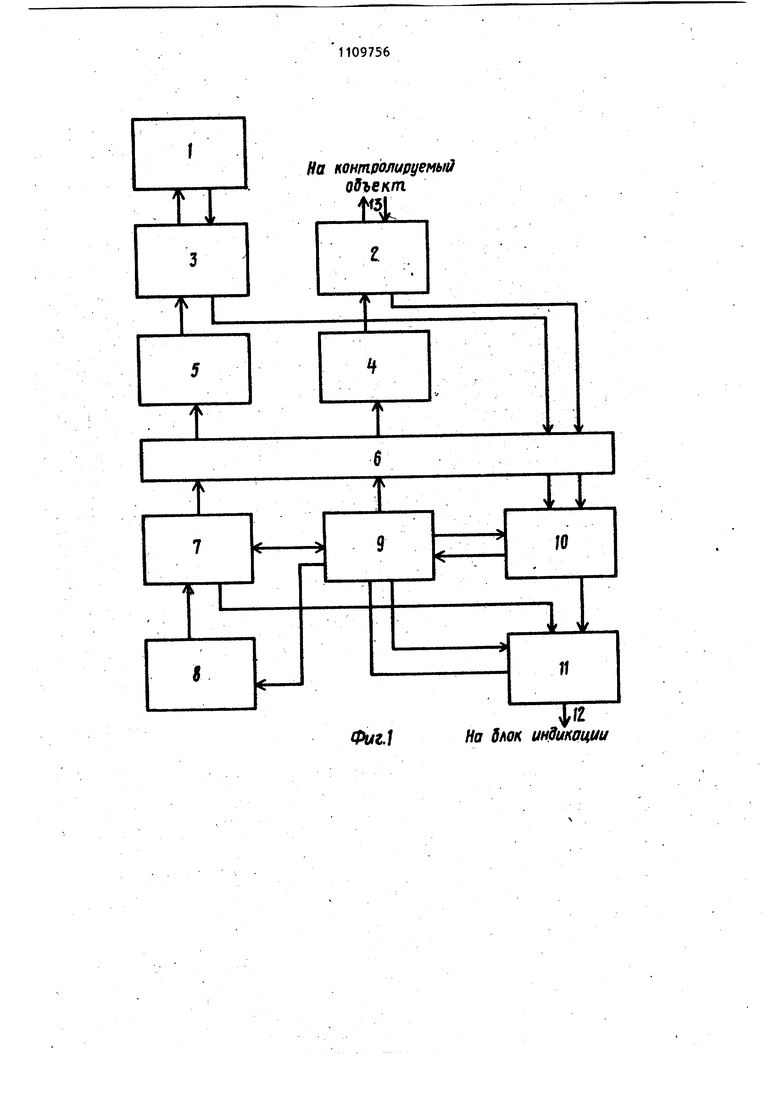

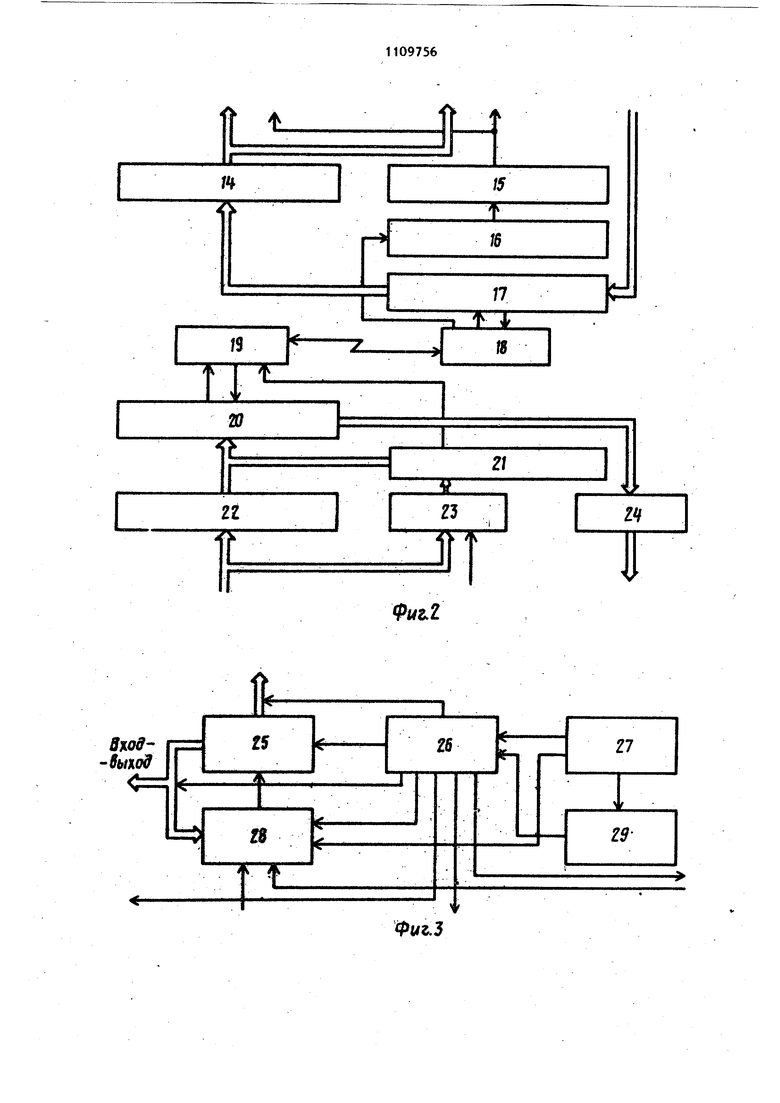

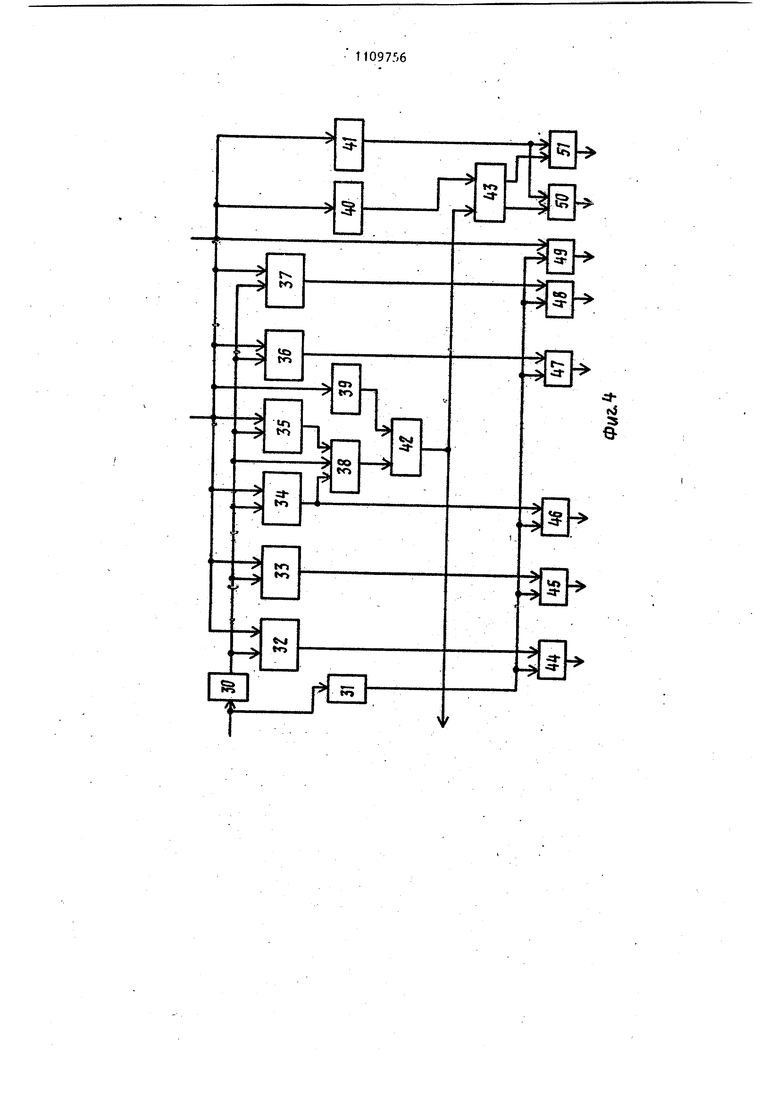

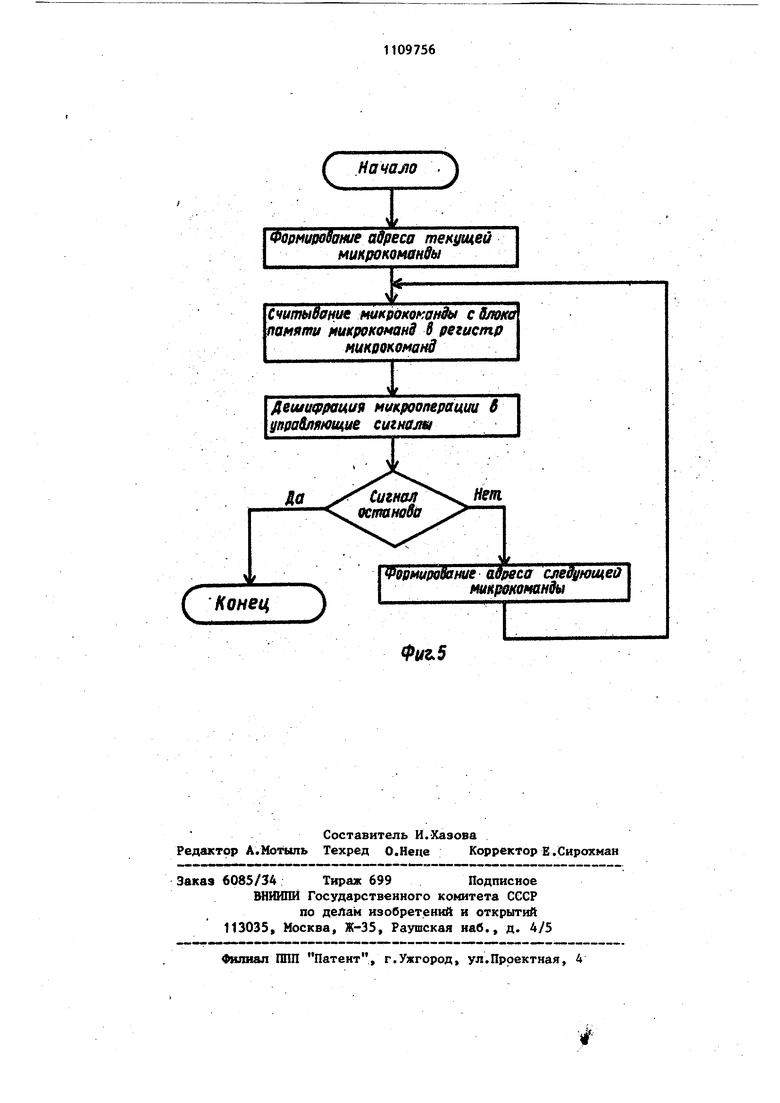

Изобретение относится к вычислительной технике и может быть использовано для а;втоматизированной провер ки функционирования и нахождения неисправностей в ЦИФРОВЫХ узлах и блоках в условиях их производства. Известно устройство для контроля цифровых блоков, содержащее коммутатор, блок индикаций и накопитель, причем первый выход коммутатора -подключен к первому входу блока инщщации, второй и третий выходы коммутатора подключены соответственно к первому и второму входам накопителя, адаптер, блок переключения, дополнительный коммутатор, блок питания, блок фиксации тестового слова, при этом вход-выход адаптера подключен к контролируемому объекту, первый вход адаптера соединен с выходом блока переключения, первьй вход которого подключен к четвертому вйходу коммутатора, пятый выход которого соединен с вторым входом адаптера, выход которого .соединен с первым входом коммутатора, второй вход которого соедин(н с первым выходом дополнительного коммутатора, второй выход которого подключен к первому входу . блока фиксации тестового слова, выход которого соединен с третьим входом коммутатора, четвертый вход которого является тестовым входом устройства, второй вход блока переключения соединен с выходом блока питания, вход которого подключен к треть ему выходу дополнительного коммутатора, четвертый выход которого соеди нен с третьим входом блока переключения, первый вход дополнительного коммутатора- является информационным входом устройства, объединен с вторым входом блока фиксации тестового слова и подключен к третьему выходу коммутатора, второй вход дополнитель ного коммутатора является управляющим входом устройства, пятый выход дополнительного коммутатора соединен с третьим входом накопителя, шестой выход дополнительного коммутатора подключен к второму входу блока инди кации 1 } Недостаток такого устройства низкая точность контроля за счет отсуствия определения возможности места неисправности. Наиболее близким к предлагаемому по технической сущности является устройство для контроля и диагностики дискретных объектов, содержащее блок ввода, первьй блок памяти контролирующих тестов и эталонных реакций, коммута тор, блок сравнения, бло управления, причем первьй выход блока ввода соединен с информационным входом первого блока памяти контроли рующих тестов и эталонных реакций, управляющий вход которого подключён к первому выходу блока управления, второй и третий выходы которого подключены соответственно к первым входам блока сравнения и коммутатора, первьй выход которого подключен к вт рому входу блока сравнения, первый выход которого подключен к первому входу блока управления, второй вход которого соединен с первым выходом первого блока памяти контролирующих тестов и эталонных реакций и с вторы входом коммутатора, третий вход и второй выход которого подключены COOTветственно к выходу-входу проверяемо.го объекта, второй выход первого блока памяти контролирующих тестов и эталонных реакций подключен к третье56 .4 му входу блока сравнения, вход и второй выход блока ввода подключены соответственно к четвертому выходу и третьему входу блока управления, введены блок анализа места неисправности, второй блок памяти эталонной неисправности, третий блок памяти места неисправности, причем третий и четвертьй выходы блока ввода подключены соответственно к первым вхбдам второго блока памяти эталонной неисправности и третьего блока памяти места неисправности, пятъш выход блока управления подключен к первому входу блока анализа места неисправности, второй вход которого подключен к второму выходу блока сравнения, первьй выход блока анализа места неисправности подключен к второму входу третьего блока памяти места неисправности, выход которого подключен к входу индикатора, второй выход и третий вход второго блока памяти места неисправности подключены соответственно к третьему входу и второму выходу блока анализа места неисправности 12 . Недостатками известного устройства являются низкая точность контроля и большая трудоемкость составления диагностических тестов; Цель изобретения - повьшение точности диагностирования. Поставленная цель достигается тем, что в устройство, содержащее, блок ввода, блок памяти, эталонный блок, блок управления, блок сравнения, блок анализа места неисправности и первьй коммутатор, причем выход ёлока ввода соединен с информационным входом блока памяти, соединенного двухсторонней связью с первым входом-выходом блока управления, выходы микроприказов которого соединены с управляющими входами блока ввода и блока сравнения, выход несравнения которого. Соединен с первым входом логических условий блока управления, первьй коммутатор соединен двухсторонней связью с контролируемым объектом, выход равенства блока сравнения соединен с первым входом блока анализа места неисправности, второй вход которого соединен с соответствующим выхоJJ дом микроприказов блока управления. блок анализа места неисправности содержит регистр, схему сравнения, триггер, два элемента И, введены второй коммутатор, два блока задания входных воздействий и блок сопряжени а в блок анализа места неисправности введены пять дешифраторов, пять регистров, второй триггер и группа элементов И, причем первый вход блока анализа места неисправности соеди нен с входами первого и второго дешифраторов, выходы первого дешифрато ра соединены с управляющими входами с первого по шестой регистров, инфор мационные входы которьпс и входы третьего, четвертого и пятого дешифрато ров соединены с информационным выходом блока памяти, выходы первого, второго, третьего, пятого и шестого регистров и второй вход блока анализа места неисправности соединены соответственно с первыми входами эле ментов И группы, вторые входы которы соединены с выходами второго дешифратора, выходы третьего и четвертого дешифраторов соединены соответственно с первым входом первого триггера и первыми входами первого и второго элементов И, вторые входы ко торьгк соединены соответственно с пер вым и вторым выходами первого триггера, второй вход которого соединен с выходом второго триггера и с вторым входом логических условий блока управления, причем в блоке анализа места неисправности выходы третьего и четвертого регистров соединены с первым и вторым входами схемы сравне ния, третий вход крторой соединен с соответствующим выходом дешифратор;а, а выход - с первым входом второго 1 триггера, второй вход которого соеди нен с выходом пятого дешифратора, выходь элементов И группы и выходы nepBioro и второго элементов И образуют информационный выход устройства блок сопряжения содержит два узла согласования, два регистра сдвига, два регистра адреса, два приемопередатчика, дешифратор управлякяцих слов два узла выходных усилителей, причем информационные входы первого и второ чго узлов согласования соединены с информационным выходом блока памяти, управляющий вход второго узла.согласования соединен с соответствующим выходом микроприказов блока управления, выход первого узла согласования соединен с входом регистра сдвига, соединенного двухсторонней связ-ью с первым приемопередатчиком, линией связи соединенным с вторым приемопер датчиком, соединенным двухсторонней связью со вторым регистром сдвига, первый выход которого соединен с информационным входом первого регистра адреса, управляющий вход которого соединен с соответствующим выходом второго приемопередатчика, а выход с входом дешифратора управляющих слов, второй выход второго регистра сдвига соединен с входом первого блока выходных усилителей, выход которого соединен с входами первого и второго блоков задания.входных воздействий, соединенньк также с выходом дешифратора управляющих слов, выходы перво-/ го и второго блоков задания входных воздействий соединены с соответствующими входами первого и второго ком-. мутаторов, причем второй коммутатор соединен двухсторонней связью с эталонным блоком, выходы первого и второго коммутаторов соединены с информационным входом второго регистра сдвига блока сопряжения, в котором выход первого регистра сдвига через второй блок вькодных усилителей соединен с входом блока сравнения, а выход второго блока согласования соединен с входом второго регистра адреса, информационный выход которого соединен с соответствующим входом первого регистра сдвига, управляющий выход второго регистра адреса соединен с соответствующим входом первого приемопередатчика, при этом блок управления содержит генератор тактовых импульсов, память микроопераций, дешифратор микроопераций, сумматор и регистр сдвига, причем выходы гене.рато.ра тактовых импульсов соединены с 73КТОВЫМИ входами дешифратора микроопераций, регистра сдвига и памяти микроопераций, выход которой соединен с информационным входом дешифратора | кроопераций, выходы которого соединены с управляющими входами сумматора и регистра сдвига и являются выходами микроприказов блока управления, первый и второй разрядные входы регистра сдвига являются Первым и вторым входами логических условий блока управления, выход сумматора и информационный вход регистра сдвига соединены между собой и образуют вход-выход блока управления. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока сопряжения; на фиг. 3 - схема блока управления; на фиг. - схема блока анализа неисправностей; на фиг. 5 - блок-схема алгоритма для бл ка управления. Устройство (фиг. 1) содержит эталонный блок 1, первый 2 и второй 3 коммутаторы, первый 4 и второй 5 олокй задания входных воздействий, блок 6 сопряжения,блок 7 памяти, блок 8 ввода, блок 9 управления, блок 10 сравнения, и блок 11 анализа места неисправности, информационнь выход 12, вход-выход 13. Блок 6 сопряжения координат (фиг, 2) содержит первый блок 14 выходных усилителей, дешифратор 15 управляющих слов, первьй регистр 16 адреса, второГг регистр 17 сдвига, первьА 18 и второй 19 приемопередатчики, первый регистр 20 сдвига, второй регистр 21 адреса, первый 22 и второй.23 узлы согласования и второй блок 24 выходных усилителей. Блок 9 управления (фиг. 3) состои из сумматора 25, дешифратора 26 микроопераций, генератора 27 тактовых импульсов, регистра 28 сдвига, памя ти 29 микроопераций. Блок 11 анализа места неисправнос ти (фиг. 4) состоит из первого 30 и второго 31 дешифраторов, регистров 32-37, схемы 38 сравнения, пятого 39, третьего 40 и четвертого 41 дешифраторов, второго 42 и первого 43 триггеров, группы элементов И 44-49, первого 50 и второго 51 элементов И. Эталонный блок 1 представляет собой заведомо исправный цифровой узел или блок, аналогичный контролируемому, и предназначен для определения эталонных значений сигналов как на выходах объекта, так и в его внутрисхемных точках. Первый 2 и второй 3 коммутаторы представляют собой наборы ключей на базе логических элементов И, обеспечивающих коммутацию сигналов между эталонным и соответственно контролируемым объектом с одной стороны и блоками 4 и 5, а также блоком 6 с др гой стороны. Первый 4 и второй 5 блоки задания входных воздействий предназначены дл запоминания входных воздействий, подаваемых на эталонный блок 1 и соответственно контролируемый объект как в процессе контроля, так и в процессе диагностики цифрового узла. Блок 6 сопряжения координат обесп чивает передачу входных воздействий. поступающих от блока 7 памяти, на соответствующие блоки 4 и5, а также коммутацию выходных реакций, поступающих от коммутаторов 2 и 3 на блок 10 сравнения по управляющим сигналам ; блока 9 управления. Блок 6 выполняет также роль дистанционного приемопередатчика между блоками 2-5 устройства,выполненными в виде рабочего терминала, и блоками 7-11 устройства, выг полненны «1 в виде управлякицей ЭВМ. Блок 7 памяти состоит из запоминающих элементов, предназначенных для хранения и вьздачи на контролируе1« 1й и эталонный объекты контрольно-диагностических тестов. Блок 8 ввода содержит считыватель и узлы сопряжения и предназначен для ввода с носителя (перфолента, магнитная лента и т.д.) информации, необходимой для анализа схем. Блок 9 управления предназначен для выработки управляющих сигналов и синхронизации работы всего устройства в зависимости от сигналов, поступающих на него из блока 7 памяти, блока 10 сравнения и блока 11 анализа места неисправности. Блок 10 сравнения содержит регистры и элементы И, предназначенные для выявления факта совпадения или несовпадения реакций эталонного и проверяемого объектов как в процессе контроля, так и в процессе диагностики. Блок 11 анализа места неисправности предназначен для запоминания номера ошибочного микротеста, осуществления алгоритма поиска неисправности в режиме пошаговой диагностики, а также для выработки и выдачи на блок индикации информации о месте неисправности. Устройство работает следующим образом. По команде с блока 9 управления из блока 8 ввода в блок 7 памяти записываются контрольно-диагностические тесты. При этом в каждой тестовой строке (далее микротесте) информация об изменении воздействий на объект контроля записывается в определенном порядке и разбита на отдельные тестовые шаги для дальнейшего облегчения диагностики места неисправности. К устройству подключается эталонный блок 1, соответствующий контролируемому объекту, и с пульта управления устройства инициализируется тестовая таблица данного объекта. После этого к устройству, подключается очередной контролируемый объект и по сигналу блока 9 управления устанавливаются в исходное состояние блоки 4 и 5 и соответственно входные контакты эталонного и контролируемого объектов. Далее с помощью определенной подпрограммы, содержащейся в блоке 7 памяти, проверяется отсутствие ложных замыкан1Й и наличие нужных соединений между выводами контролируемого объекта. При соответствии соединений на объекте контроля с соединениями на эталонном блоке 1, к обоим объектам подключается напряжение питания и начинается контроль объекта. По сигналу из блока 9 управления блок 7 памяти через блок 6, блоки 4 и 5 и коммутаторы 2 и 3, вьвдает на входы контролируемого и эталонного блоков первый микротест. После этого блок 6 сопряжения череэ коммутаторы 2 и 3 опра шивает выходы контролируемого и эталонного блоков и передает полученную информацию на блок 10 сравнения. Блок 10 сравнения сопоставляет реакции обоих объектов и в случае их совпадения выдает на блок 9 управления сигнал, по которому в последнем вырабатывается сигнал запуска следукяцего микротеста. Очередной и последующие микротесты выбираются из блока 7 памяти и обрабатываются устройством описанным образом. В случае совпадения всех реакций контролируемого и эталонного объектов блок 9 управления через блок 11 анализа места неисправности выдает на блок индикации сообщение об исправности контролируемого объекта. В случае несовпадения реакций эталонного и контролируемого блоков сигнал несовпадения с блока 10 сравнения поступает на блок 9 управления, по команде которого с блока 7 памяти считывается и запоминается в блоке 11 номер ошибочного микротеста N. После этого блок 9 управления возобновляет контроль объекта с первого микротеста описанным способом. Одновременно блок 11 выделения неисправности следит за номером выполнякнцегося микротеста и после выполнения Н{ микротеста переводит устройство на режим диагностики неисправности. В данном режиме ошибочный микротест N выполняется по отдельным тестовым шагам, т.е. с заранее установленной последо16 вательностью осуществляется изменение сигнала воздействия лишь на одном входном контакте контролируемого объекта. После каждого тестового шага по сигналам блока 9 управления через блок 6 и коммутаторы 2 и 3 запрашиваются реакции выходов эталонного и контролируемого блоков и осуществляется их сопоставление посредством блока 10 сравнения. По обнаружении несоответствия выполнение микротеста прекращается, блок 11 анализа места неисправности выводит на блок индикации диагностическое сообщение, содержащее номер микротеста, номер шага в микротесте, номера выходных контактов с несрвпадавшими реакциями блоков и координаты характерных внутрисхемных точек данного микротеста. Поскольку на обоих блоках сохраняется текущее состояние элементов схемы на момент неисправности, отображенной диагностической информации достаточно. Чтобы регулировщик с помощью диагностического щупа мог выявить неисправность с точностью до одной микросхемы. Если при выполнении N. микротеста в диагностическом режиме несовпадение реакций обоих объектов не имеет места до появления признака конца микротеста, блок 11 прекращает режим диагностики и по сигналам блока 9 управления продолжается выполнение последугацих микротестов в режиме контроля. Подобная ситуация возможна в случаях, если в контролируемом объекте возникли случайные ошибки, которые при повторном выполнении теста не повторяются. В этом случае по завершению контроля объекта блок 11 выводит на блок индикации предупреждаюцее сообщение о появлении случайной ошибки при выполнении определенного микротеста. Применение в предлагаемом устройстве для эталонного и контролируемого блоков отдельных блоков 4 и 5 задания входных воздействий позволяет реализовать дополнительный режим контроля (так называемое выравнивание счетчиков). Данный режим необходим в случаях, когда контролируемый блок содержит внутрисхемные элементы памяти и схемы с обратной связью, недоступные для установки в исходное состояние определенным входным сигналом. После подключения такого объек- та к питанию и проверки правильности соединении между выводами контролируемого блока специальным сигналом блока 9 управления через блок 6 блокируется блок 4 задания входных воздействий для эталонного блока 1. Далее из блока 7 памяти через блок 6 сопряжения, блок 4 и первый коммутатор 2 на входы контролируемого блока подаются входные воздействия, поочередно переключающие состояние элемен тов памяти или схем с обратной связь После каждого переключения опрашивается состояние выходов контролируемо го и эталонного блоков, которое через коммутаторы 2 и 3 и блок 6 сообщается блоку 10 сравнения. При поступлении от блока 10 сравнения сигнала совпадения, которьй свидетельст вует, что внутрисхемные элементы объекта контроля уста новлены в идентичном с эталонным блоком состоянии, подача входных воздействий через блок А задания входных воздей- ствий и коммутатор 2 прекращается и происходит разблокировка блока 5 задания входных действий. После этого блок 9 управления запускает блок памяти на вьщачу на оба объекта следующего микротеста тестовой таблицы. Блок 6 сопряжения работает следую щим образом. В режиме передачи информации на контролируемый объект по управляющим сигналам, поступающим от блока 9 управления через узел 23 согласования, второй регистр 21 адреса устанавливает второй приемопередатчик 19 в направление передачи. Передаваемые данные и адреса, поступающие от блока 7 памяти через первый узел 22 согласования, посредством регистра 2 сдвига преобразуются в последователь ный формат и вместе с флагом направления передачи поступают на второй приемопередатчик 19, который по двух проводной линии в квазитроичном коде передает их на первый приемопередатчик 18 терминальной части устройства Считанные с выхода первого приемопередатчика 18 данные .посредством регистра 17 сдвига преобразуются в параллельный формат. Первый регистр 16 адреса из общего потока информации выделяет адресные коды, которые посредством дешифратора 15 управляющих слов преобразуются в сигналы управле ния блоками 4 и 5. Данные же из регистра 17 сдвига через блок 14 выход ных усилителей непосредственно посту пают на информационные входы блоков 4 и 5. Режим приёма информации с выходом контролируемого блока осуществляется в два этапа. На первом этапе через блок 6 соплзяжения передается адрес запроса информации на дещифратор 13 управляющих сигналов, которьй вырабатывает сигналы опроса заданных каналов первого и второго коммутаторов 2 и 3. Одновременно первый и второй приемопередатчики 18 и 19 переключаются в направление приема информации. На втором этапе поступающая информация первым регистром 17 сдвига преобразуется в последовательньй формат, посредством первого приемопередатчика 18 передается на второй приемопередатчик 19 и далее при помощи второго регистра 20 сдвига вновь преобразуется в параллельный формат и через блок 24 поступает на выходы блока. Блок 9 управления работает следую.щим образом. По сигналам генератора 27 тактовых импульсов, обеспечивающим синхронизацию работы всех узлов блока 9 управления, из памяти 29 микроопераций считывается управляющее слово текущей микрокоманды, которое поступает на дешифратор 26 микроопераций. Последний в зависимости от типа дешифрированной микрооперации устанавливает требуемый режим работы устройства и вырабатывает соответствующие управлягацие сигналы. В режиме Ьвода информации управляющие сигналы подаются на блок 8 ввода и синхронизируют занесение- информации в блок 7 памяти. В режиме передачи информации на контролируемый блок управляющие сигналы дешифратора 26 микроопераций через вход-выход управляют передачей данных из блока 7 памяти на блок 6 и приемом управляющей информации через регистр 28 сдвига на сумматор 25. В соответствии с управляющими сигналами дешифратора 26 микроопераций сумматор 25 осуществляет над управляющей информацией необходимые логические и арифметические операции и сформированные таким образом адресные сигналы вьщает на адресный вход блока 6 для управления процессом передачи информации на соответствукяцие регистры блоков 4 и 5. В режиме считывания выходных реакций контролируемого блока управлякхцие сигналы дешифратора 26 мнкро-. операций обеспечивают передачу через, блок 6 адреса опрашиваемых каналов первого и второго коммутаторов 2 и 3, и синхронизацию приема и сравнения считанной информации в блоке 10 сравнения.

В режиме обработки информации управляющими сигналами дешифратора 26 микроопераций обеспечиваются управление работой регистра 28 сдвига и сумматора 25 с вьщачей результата обработки через вход-выход блока управления на блок 7 памяти, через вход-выход блока 9 управления управление передачей данных из блока 7 памяти в блок 11, управление занесением данных в нужные регистры блока 11 и прием результатов логических операций через регистр 28 сдвига на сумматор 25, котор1Л осуществляет их анализ и формирование соответствующих программных переходов.

Блок 11 анализа места неисправности работает следуюцим образом.

Сигналы управления, поступающие с адресной шины блока 9 управления, дешифрируются первьш дешифратором ,

При расшифровке адреса одного из .регистров 32-37 выдается сигнал на занесение в этот регистр данных, поступающих по входу от блока 7 памяти. Регистр 32 фиксирует номер тестовой таблицы, регистр 33 - признак

режима питания объектов, регистр 34 номер ошибочного микротеста, регистр 35 - номер выполнякицегося микротеста , регистр 36 - номер шага микротеста, регистр 37 - номера координат характерных точек. При выявлении в процессе контроля оошбки функционирования контролируемого объекта в регистр 34 заносится нсшер ошибочного микротеста. После повторного начала контроля ошибочного объекта в регистр 35 заносится номер каящого вгаюлнякщегося микротеста, после чего опраатвается схема 38 сравнения. При совпадении информации в регистрах 34 и 35 схема 38 сравнения устанавливает в 1 триггер 42, который в свою очередь устанавливает в 1 триггер 43 и выдает блоку 9 управления сигнал на перевод ycTpdtctBa в режим диагностики.По сигналу блока 9 управления в регистры 32 и 33 заносится информация о выполняющейся тестовой таблице и установленных режимах питания объектов.

Использование предлагаемого устройства позволяет повысить качество выпускаемой продукщ1и и за счет повышения точности и производительности диагностики неисправностей в дискретных типовьк элементах замены на десятки тысяч нормо-часов снизить трудоемкость изготовления квазиэлектронных АТС.

фГ2 Фиг./На длок индикации

Ф11г.3

5

:ai ОФормирование адреса текущей микромманвы

Считывание микрококднды cS/юко памяти микрок анЗ 8 регистр

Деи/шррация микрооперации б управляющие сигналш

Начало микрокоманд

Г Конец

VopMupo&XHue йвреса слевуюи еО микроногшнды

Фиг.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровыхблОКОВ | 1979 |

|

SU807305A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-08—Подача