(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ НЕИСПРАВНОСТЕЙ ЦИФРОВЫХ СИСТЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Устройство для контроля работоспособности аналого-цифровых преобразователей | 1979 |

|

SU864545A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1166121A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

| Система для контроля параметров | 1985 |

|

SU1255996A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Система централизованного контроля радиоэлектронных изделий | 1978 |

|

SU744481A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых систем.

По основному авт.св. № 561965 известно устройство для обнаружения неисправностей цифровых систем,содержащее постоянный запоминающий блок, блок управления, счетчик команд, блок вывода информации, входные и выходные коммутаторы, блок сравнения, блок индикации, регистр приема инфор-; мации, сумматор, схемы ИЛИ и схемы И причем контролируелеле выходы проверяемой системы, подключенные к выходному коммутатору, соединены с входами первой схемы ИЛИ, выход которой под- ключен к первым входам третьей и четвертой схем ИЛИ, а также через первую схему И и вторую схему ИЛИ соединен с входом регистра приема, управляющий которого подключен к одному из выходов блока управления, а выход к входу сумматора и к первому входу второй схемы И, второй вход которой соединен с выходом блока управления, выход второй схемы И через третью схему ИЛИ подключен к одному из входов блока сравнения, два других входа которого соединены ,с блоком управления и блоком вывода информации, а

выход - с блоком индикации и одним из входов блока управления, два других выхода блока вывода информации подключены к входному коммутатору и второму входу четвертой схемы ИЛИ, а входы - к блоку управления и постоянному загГЬминающему блоку, соединенному с блоком управления, блоком индикации и счетчиком команд, выхо10ды блока управления соединены с блоком индикации, входным коммутатором, сумматором, вторым входом первой схек И и выходным ко1«4утатором, выходы входного коммутатора подключены к входам проверяемой системы tl3...

15

Недостатком известного устройства является трудность разделения неисправности между проверяемой системой и устройством для обнаружения неисп20равностей, так как в режиме автоматической самопроверки в известном устройстве не проверяются блок вывода информации, входной и выходной коммутаторы,первая схема ИЛИ, первая схема

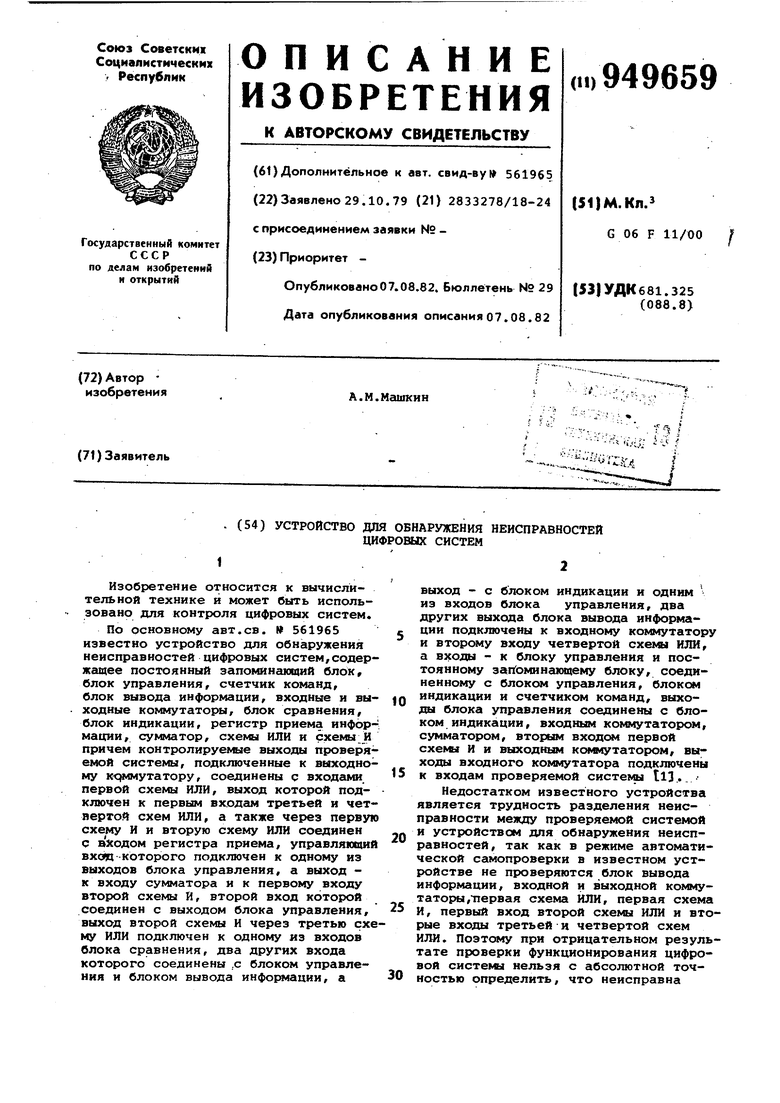

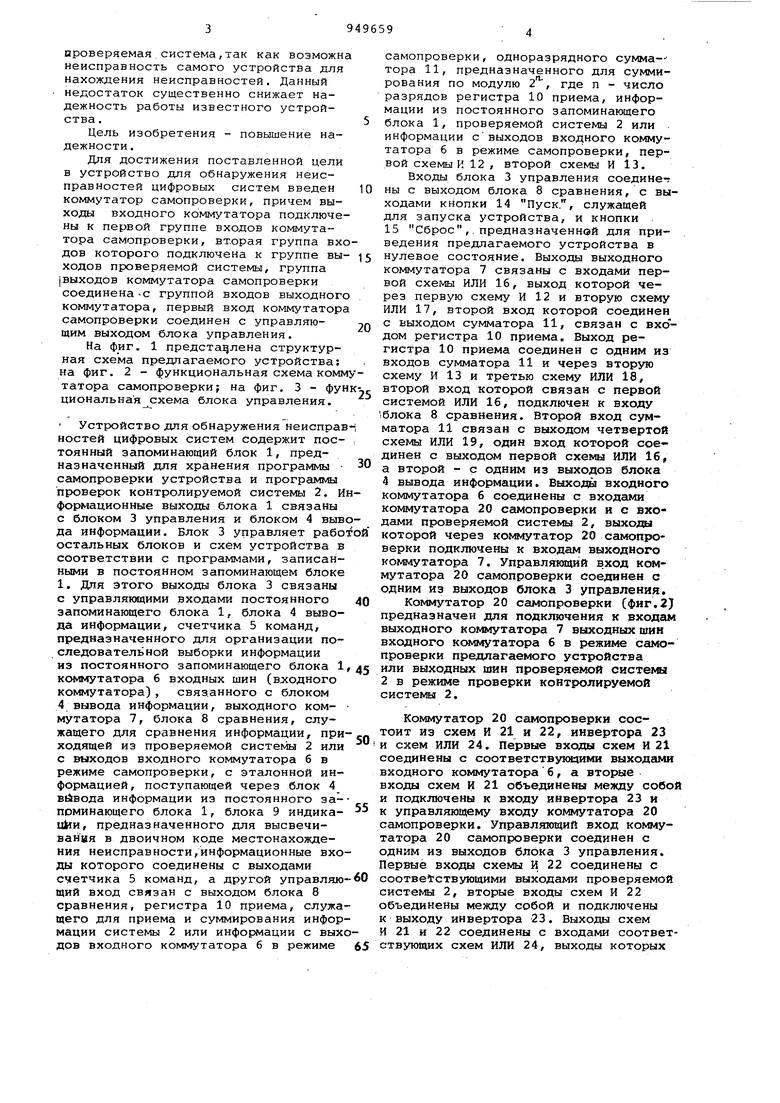

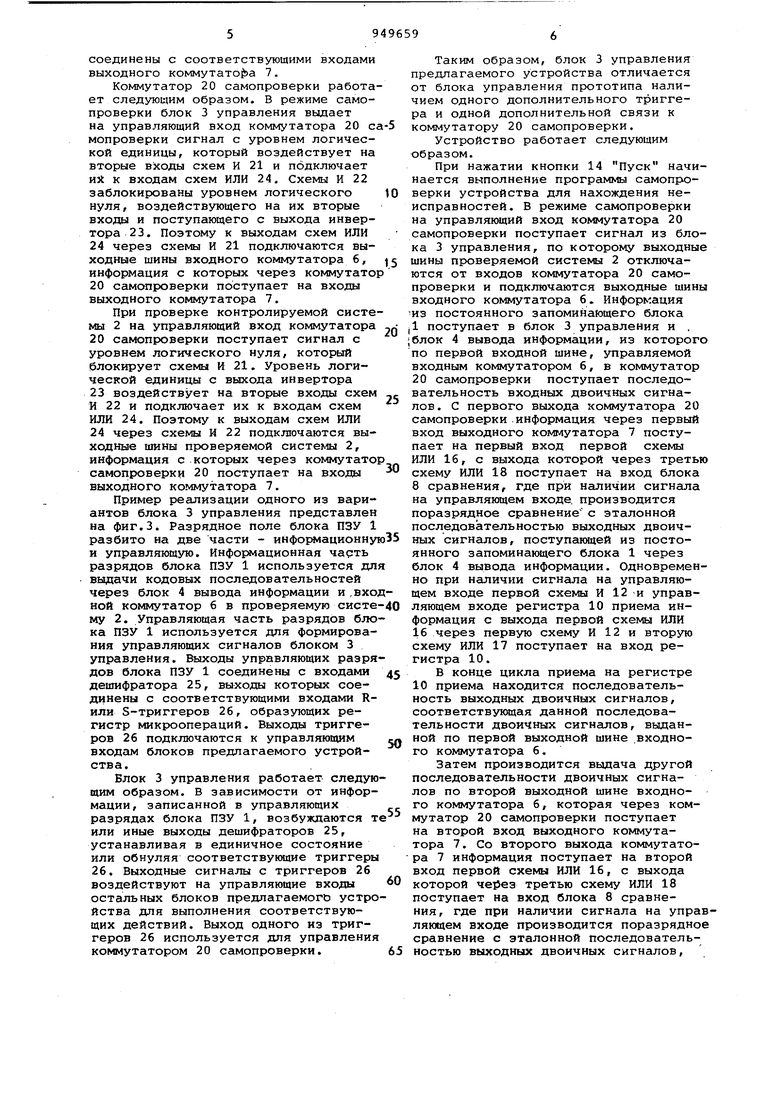

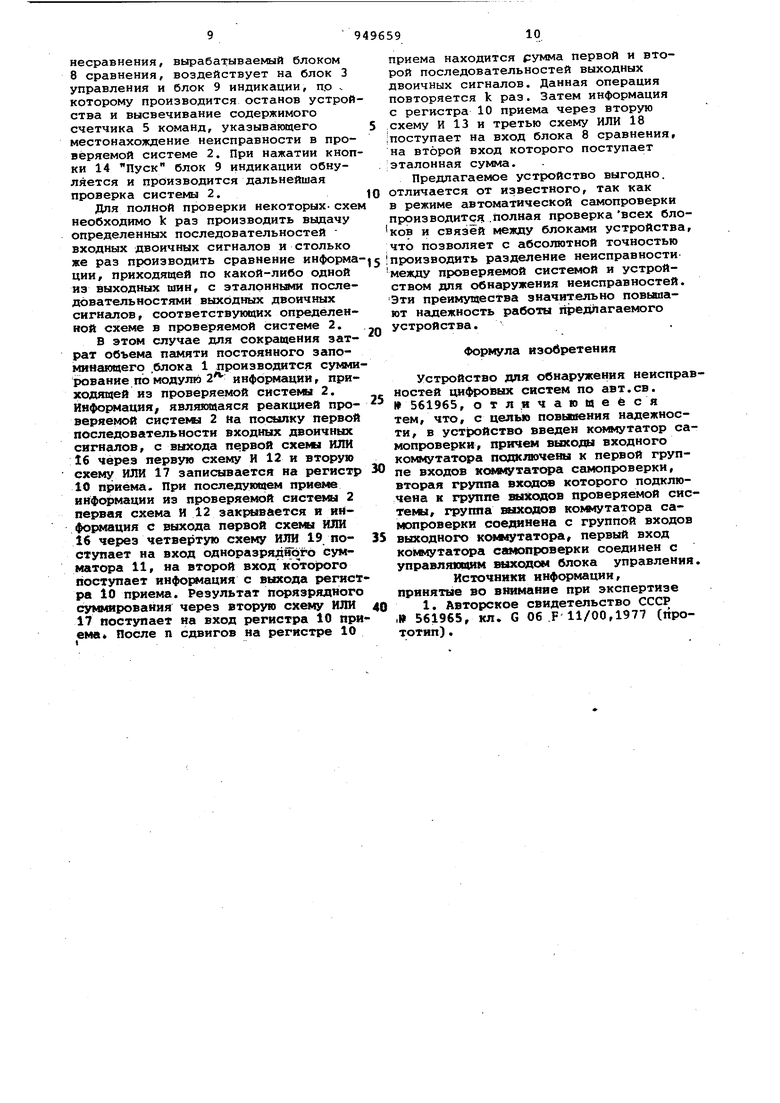

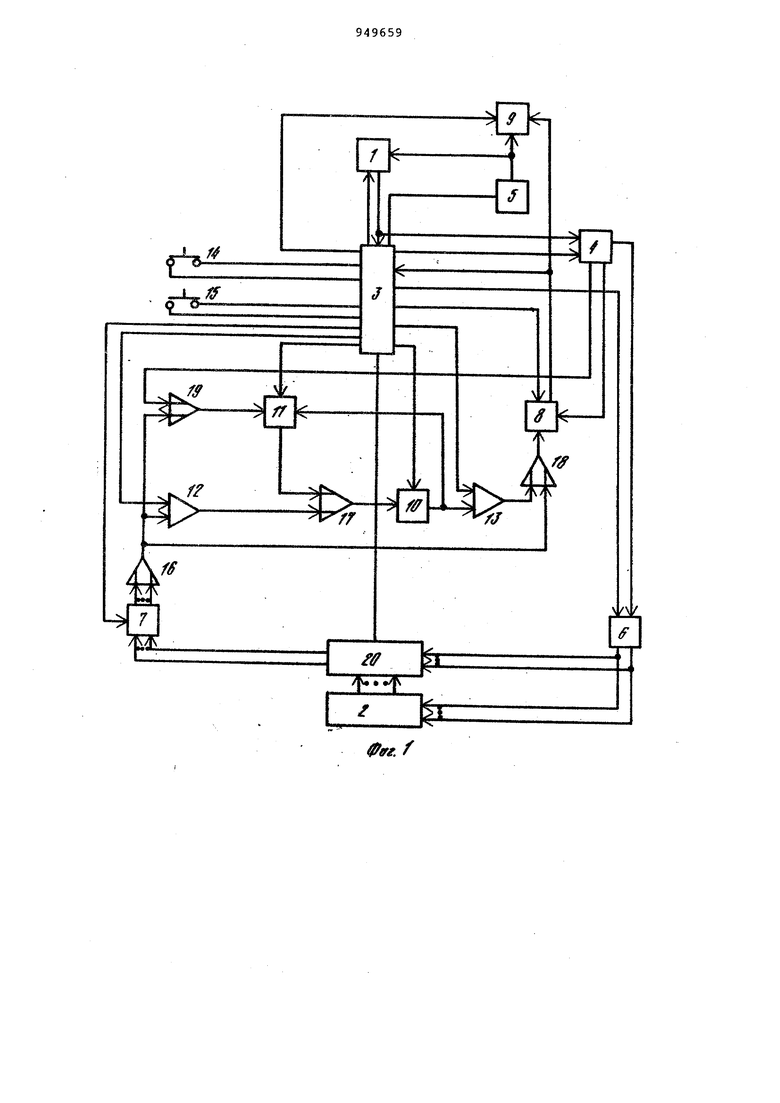

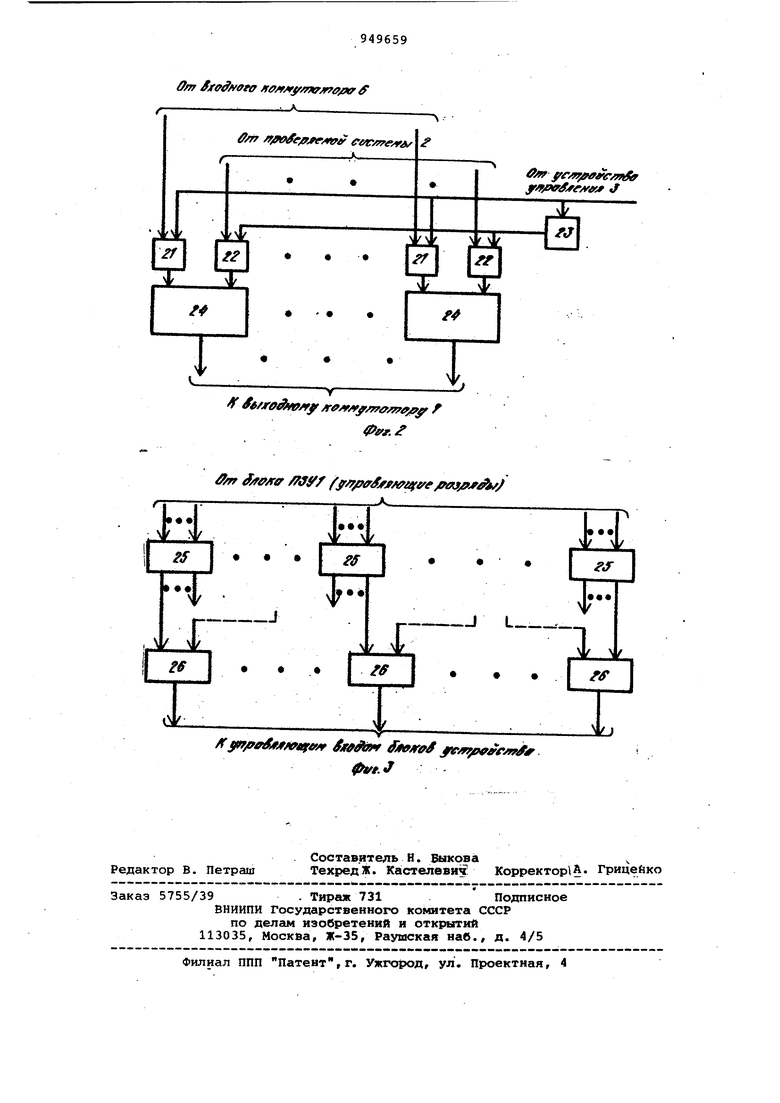

25 И, первый вход второй схемы ИЛИ и вторые входы третьей и четвертой схем ИЛИ. Поэтому при отрицательном результате проверки функционирования цифровой системы нельзя с абсолютной точ30ностью определить, что неисправна проверяемая система,так как возможна неисправность самого устройства для нахождения неисправностей. Данный недостаток существенно снижает надежность работы известного устройства. Цель изобретения - повышение надежности. Для достижения поставленной цели в устройство для обнаружения неисправностей цифровых систем введен коммутатор самопроверки, причем выходы входного коммутатора подключены к первой группе входов коммутатора самопроверки, вторая группа вхо дов которого подключена к группе выходов проверяемой системы, группа ВЫХОДОВ коммутатора самопроверки соединена -с группой входов выходного коммутатора, первый вход коммутатора самопроверки соединен с управляющим выходом блока управления. На фиг. 1 предста:длена структурная схема предлагаемого устройства: на фиг. 2 - функциональная схема комм татора самопроверки; на фиг. 3 - фун циональная схема блока управления. Устройство для обнаружения неисправ ностей цифровых систем содержит постоянный запоминающий блок 1, предназначенный для хранения программы самопроверки устройства и программы прюверок контролируемой системы 2. И формационные выходы блока 1 связаны с блоком 3 управления и блоком 4 выв да информации. Блок 3 управляет рабо остальных блоков и схем устройства в соответствии с программами, записанными в постоянном запоминающем блоке 1, Для этого выходы блока 3 связаны с управлякицими входами постоянного запоминающего блока 1, блока 4 вывода информации, счетчика 5 команд, предназначенного для организации последовательной выборки информации из постоянного запоминающего блока 1 коммутатора 6 входных шин (входного коммутатора), связанного с блоком 4 вывода информации, выходного коммутатора 7, блока 8 сравнения, служащего для сравнения информации, при ходящей из проверяемой системы 2 или с выходов входного коммутатора б в режиме самопроверки, с эталонной информацией , поступающей через блок 4 вывода информации из постоянного запоминающего блока 1, блока 9 индикацйи, предназначенного для высвечивания в двоичном коде местонахождения неисправности,информационные вхо ды которого соединены с выходами счетчика 5 команд, а другой управляю щий вход связан с выходом блока 8 сравнения, регистра 10 приема, служа щего для приема и суммирования инфор мации системы 2 или информации с вых дов входного коммутатора б в режиме самопроверки, одноразрядного сумма--тора 11, предназначенного для суммирования по модулю 2 , где п - число разрядов регистра 10 приема, информации из постоянного запоминающего блока 1, проверяемой системы 2 или информации свыходов входного коммутатора 6 в режиме самопроверки, первой схемы К 12 , второй схемы И 13. Входы блока 3 управления соедине-т ны с выходом блока 8 сравнения, с выходами кнопки 14 Пуск, служащей для запуска устройства, и кнопки 15 Сброс,,предназначенной для приведения предлагаемого устройства в нулевое состояние. Выходы выходного коммутатора 7 связаны с входами первой схемы ИЛИ 16, выход которой через первую схему И 12 и вторую схему ИЛИ 17, второй вход которой соединен с выходом сумматора 11, связан с входом регистра 10 приема. Выход регистра 10 приема соединен с одним из входов сумматора 11 и через вторую схему И 13 и третью схему ИЛИ 18, второй вход которой связан с первой системой ИЛИ 16, подключен к входу Яблока 8 сравнения. Второй вход сумматора 11 связан с выходом четвертой схемы ИЛИ 19, один вход которой соединен с выходом первой схемы ИЛИ 16, а второй - с одним из выходов блока 4 вывода информации. Выхода входного коммутатора 6 соединены с входами коммутатора 20 самопроверки и с входами проверяемой системы 2, выходы которой через коммутатор 20 самрпроверки подключены к входам выходного коммутатора 7. Управлякмдий вход коммутатора 20 самопроверки соединен с одним из выходов блока 3 управления, Ко1Умутатор 20 самопроверки Сфиг.2) предназначен для подключения к входам выходного ко1юиутатора 7 выходных шин входного коммутатора 6 в режиме самопроверки предлагаемого устройства или выходных шин проверяемой системы 2 в режиме проверки контролируемой системы 2. Коммутатор 20 самопроверки состоит из схем И 21 и 22, инвертора 23 и схем ИЛИ 24. Первые входы схем И 21 соединены с соответствующими выходг1ми входного коммутатора б, а вторые входы схем И 21 объединены между собой и подключены к входу инвертора 23 и к управляющему входу коммутатора 20 самопроверки. Управлянлций вход коммутатора 20 самопроверки соединен с одним из выходов блока 3 управления. Первые входы схемы И 22 соединены с соотве ствующими выходами проверяемой системы 2, вторые входы схем И 22 объединены между собой и подключены к выходу инвертора 23, Выходы схем Я 21 н 22 соединены с входами соответствующих схем ИЛИ 24, выходы которых соединены с соответствующими входами выходного коммутатора 7. Коммутатор 20 самопроверки работа ет следующим образом. В режиме самопроверки блок 3 управления вьщает на управляющий вход коммутатора 20 с мопроверки сигнал с уровнем логической единицы, который воздействует на вторые входы схем И 21 и подключает к:а к входам схем ИЛИ 24, Схемы И 22 заблокированы уровнем логического нуля, воздействующего на их вторые входы и поступающего с выхода инвертора 23. Поэтому к выходам схем ИЛИ 24 через схемы И 21 подключаются выходные шины входного коммутатора 6, информация с которых через коммутато 20 самопроверки поступает на входы выходного коммутатора 7. При проверке контролируемой систе мы 2 на управляющий вход коммутатора 20 самопроверки поступает сигнал с уровнем логического нуля, который блокирует схемы И 21. Уровень логической единицы с выхода инвертора 23воздействует на вторые входы схем И 22 и подключает их к входам схем ИЛИ 24. Поэтому к выходам схем ИЛИ 24через схемы И 22 подключаются выходные шины проверяемой системы 2, информация с которых через коммутато самопроверки 20 поступает на входы выходного коммутатора 7. Пример реализации одного из вариантов блока 3 управления представлен на фиг.З. Разрядное поле блока ПЗУ 1 разбито на две части - информационну и управляющую. Информационная чарть разрядов блока ПЗУ 1 используется дл выдачи кодовых последовательностей через блок 4 вывода информации и ,вхо ной коммутатор 6 в проверяемую систе му 2. Управляющая часть разрядов бло ка ПЗУ 1 используется для формирования управляющих сигналов блоком 3 управления. Выходы управляющих разря дов блока ПЗУ 1 соединены с входами дешифратора 25, выходы которых соединены с соответствующими входами Rили S-триггеров 26, образующих регистр микроопераций. Выходы триггеров 26 подключаются к управляющим входам блоков предлагаемого устройства. Блок 3 управления работает следую щим образом. В зависимости от информации, записанной в управляющих разрядах блока ПЗУ 1, возбуждаются т или иные выходы дешифраторов 25, устанавливая в единичное состояние или обнуляя соответствующие триггеры 26. Выходные сигналы с триггеров 26 воздействуют на управляющие входы остальных блоков предлагаемого устро йства для выполнения соответствующих действий. Выход одного из триггеров 26 используется для управления коммутатором 20 самопроверки. Таким образом, блок 3 управления предлагаемого устройства отличается от блока управления прототипа наличием одного дополнительного триггера и одной дополнительной связи к коммутатору 20 самопроверки. Устройство работает следующим образом. При нажатии кнопки 14 Пуск начинается выполнение программы самопроверки устройства для нахождения неисправностей. В режиме самопроверки на управляющий вход коммутатора 20 самопроверки поступает сигнал из блока 3 управления, по которому выходные шины проверяемой систе ы 2 отключаются от входов коммутатора 20 самопроверки и подключаются выходные шины входного коммутатора 6.. Информация ИЗ постоянного запоминающего блока 1 поступает в блок 3 управления и , блок 4 вывода информации, из которого по первой входной шине, управляемой входным коммутатором 6, в коммутатор 20 самопроверки поступает последовательность входных двоичных сигналов . С первого выхода коммутатора 20 самопроверки информация через первый вход выходного комглутатора 7 поступает на первый вход первой схемы ИЛИ 16, с выхода которой через третью схему ИЛИ 18 поступает на вход блока 8 сравнения, где при наличии сигнала на управляющем входе, производится поразрядное сравнение с эталонной последовательностью выходных двоичных сигналов, поступакнцей из постоянного запоминающего блока 1 через блок 4 вывода информации. Одновременно при наличии сигнала на управляющем входе первой схемы И 12 -и управляющем входе регистра 10 приема информация с выхода первой схемы ИЛИ 16 через первую схему И 12 и вторую схему ИЛИ 17 поступает на вход регистра 10. В конце цикла приема на регистре 10 приема находится последовательность выходных двоичных сигналов, соответствующая данной последовательности двоичных сигналов, выданной по первой выходной шине .входного коммутатора 6. Затем производится выдача другой последовательности двоичных сигналов по второй выходной шине входного коммутатора 6, которая через коммутатор 20 самопроверки поступает на второй вход выходного коммутатора 7. Со второго выхода коммутатора 7 информация поступает на второй вход первой схемы ИЛИ 16, с выхода которой через третью схему ИЛИ 18 поступает на вход блока 8 сравнения, где при наличии сигнала на управляющем входе производится поразрядное сравнение с эталонной последовательностью выходных двоичных сигналов. поступающей из постоянного зУпоминающего блока 1 через блок 4 вывода информации. При приеме второй последовательности двоичных сигналов первая схема И 12 закрывается, и информация с выхода первой схемы ИЛИ 16через четвертую схему ИЛИ 19 поступает на вход одноразрядного сумма тора 11, на второй вход которого поступает информация с выхода регистра 10 приема. Результат поразрядного суммирования через вторую схему ИЛИ 17поступает на вход регистра 10. После п сдвигов на регистре 10 приема находится сумма по модулю 2 первой и второй последовательности двоичных сигналов. Аналогичным образом производится выдача и прием информации по остальным входным и выходным шинам предлагаемого устройства. После приема последней последовательности двоичных сигналов на регистре 10 приема находитс5Г сумма по модулю 2 всех последовательностей двоичных сигналов, принятых по выходным шинам коммутатора 20 самопроверки. Затем информация с регистра 10 приема через вторую схему И 13 и третью схему ИЛИ 18 поступает на вход блока 8 сравнения, на второй вход которого поступает эталонная сумма. Правильность записи информации в постоянном запоминакицем блоке 1 также проверяется путем суммирования по модулю 2 и последующего сравнени с эталонной суммой. При этом информа ция последовательно считывается из каж дои ячейки постоянного запоминающего б ка 1 и через блок 4 вывода информаци и четвертую схему ИЛИ 19 поступает . на вход сумматора 11, где осуществляется поразрядное суммирование с ин формацией, находящейся в регистре 10 приема. В случае несравнения информации, проходящей по какой-либо из выходных шин, с эталонной информацией блок 8 вырабатывает сигнал несравнения, который воздействует на блок 3 управле ния и блок 9 индикации и по которому производится останов устройства и вы вечивание содержимого счетчийа 5 команд, указывающего местонахождение неисправности в предлагаемом устройстве. При нажатии кнопки 14 Пуск блок 9 индикации обнуляется и произвидится дальнейшая самопроверка пред дагаемого устройства. Таким образом, в режиме самопроверки производится полная проверка всех блоков и связей между блоками предлагаемого устройства. . В конце режима самопроверки сигна с управляющего входа коммутатора.20 самопроверки снимается блоком 3 упра ления.. При этом выходные шины входного коммутатора 6 отключаются от Iвходов коммутатора 20 самопроверки -и подключаются выходные шины проверяемой системы 2. После окончания режима самопроверки производится программный останов устройства. При нажатии кнопки 14 Пуск начинается выполнение программы проверки контролируемой системы 2. Информация из постоянного запоминающего блока 1 поступает в блок 3 управления и блок 4 вывода информации, из которого по входным шинам, управляемым входным коммутатором 6, в проверяемую систему 2 поступает последовательность входных двоичных сигналов. При исправности проверяемой системы- 2 каждой последовательности входных двоичных сигналов соответствует последовательность определенных выходных сигналов, вырабатываемых определенной схемой проверяемой системы 2. При каждой посылке последовательности входных двоичных сигналов опрашивается состояние только одной выходной шины и производится сравнение последовательности выходных двоичных сигналов с эталонной последовательностью. Каждой эталонной последовательности соответствует определенная схема в проверяемой системе 2 и определенное значение счетчика 5 команд. Тем самым устанавливается местонахождение неисправности в проверяемой системе 2. Информация из проверяемой системы 2 через коммутатор 20 самопроверки и выходной коммутатор 7 поступает на первую схему ИЛИ 16, с выхода которой через третью схему ИЛИ 18 поступает на вход блока 8 сравнения, где при наличии сигнала на управляющем входе производится поразрядное сравнение с эталонной последовательностью вы- . ходных двоичных сигналов, поступающей из постоянного запоминающего блока 1 через блок 4 вывода информации. При наличии сигнала на управляющем входе первой схемы И 12 и управляющем входе регистра 10 приема информация с выхода первой схемы ИЛИ 16 через первую схему И 12 и вторую схему ИЛИ 17 поступает на вход регистра 10 приема. В конце цикла приема на регистре 10 приема находится последовательность выходных двоичных сигналов, соответствующая данной последовательности входных двоичных сигналов. При наличии сигнала на управляющем входе второй схемы И 13 информация с регистра 10 приема через вторую схему И 13 и третью схему ИЛИ 18 поступает на вход блока 8 сравнения, где производится поразрядное сравнение с эталонной последовательностью выходных двоичных сигналов. Сигнал

несравнения, вырабатываемый блоком 8 сравнения, воздействует на блок 3 управления и блок 9 индикации, пр которому производится останов устройства и высвечивание содержимого счетчика 5 команд, указывающего местонахождение неисправности в проверяемой системе 2. При нажатии кнопки 14 Пуск блок 9 индикации обнуляется и производится дальнейшая проверка системы 2.

Для полной проверки некоторых-схе необходимо k раз производить выдачу определенных последовательностей входных двоичных сигналов и столько же раз производить сравнение информации, приходящей по какой-либо одной из выходных шин, с эталрнньфш последовательностями выходных двоичных сигналов, соответствующих определенной схеме в проверяемой системе 2.

В этом случае для сокращения затрат объема памяти постоянного запоминаюцего .блока 1 производится суммирование по модулю информации, приходящей из проверяемой системы 2. Информация, являющаяся реакцией проверяемой системы 2 tta посылку первой последовательности входных двоичных сигналов, с выхода первой схемы ИЛИ 16 через первую схему И 12 и вторую схему ИЛИ 17 записывается на регистр 10 приема. При последующем приеме информации из проверяемой системы 2 первая схема И 12 зак|%1вается и информация с выхода первой схемы ИЛИ

16через четвертую схему ИЛИ 19 поступает на вход одноразрядного сумматора 11, иа второй вход KOTojporo поступает информация с выхода регистра 10 приема. Результат П(ч язрядиого суммирования через вторую схему ИЛИ

17поступает на вход регистра 10 приема После п сдвигов на регистре 10

приема находится румма первой и второй последовательностей выходных двоичных сигналов. Данная операция повторяется k раз. Затем информация с регистра 10 приема через вторую схему И 13 и третью схему ИЛИ 18

|поступает на вход блока 8 сравнения, на второй вход которого поступает эталонная сумма.

Предлагаемое устройство выгодно, отличается от известного, так как в режиме автоматической самопроверки производится .полная проверкавсех блоков и связей между блоками устройства что позволяет с абсолютной точностью

; производить разделение неисправности

между проверяемой системой и устройством для обнаружеиия неисправностей.

Эти преимущества значительно повышают надежность работы предлагаемого устройства.

Формула изобретения

Устройство для обнаружения неиспраностей 1и1фро вых систем по авт.св. 1 561965, отличающееся тем, что, с целые повышения надежности, в устройство введен кок 1утатор самопроверки, причем выходы входного KONGMyTaTopa подаслючены к первой группе входов коитутатора самопроверки, вторая группа входов которого подключена к группе шлходов проверяемой системы, группа )П2ходо9 ко1 утатора самопроверки соединена с группой входов выходного ксммутатора, первый вход коммутатора сююпроверки соединен с управляющим выходом блока управления

Источники инф(я мации, принятые во внимание при экспертизе

0ffg. f

ffm /jTff Afffff /fff y f ff/off ff

.. A

f2

f

-T

fjroAfff y /гл иу/даг) 5рг5г /

ff/rr /W/ fjrffpffAfjf afyfAM3/P

1

f

( M J iJLj 11

Oil

/f yr ffAnffffi tf/f j /ff fff/in

ff

f fff.

(

u 0vt. I.,

Авторы

Даты

1982-08-07—Публикация

1979-10-29—Подача