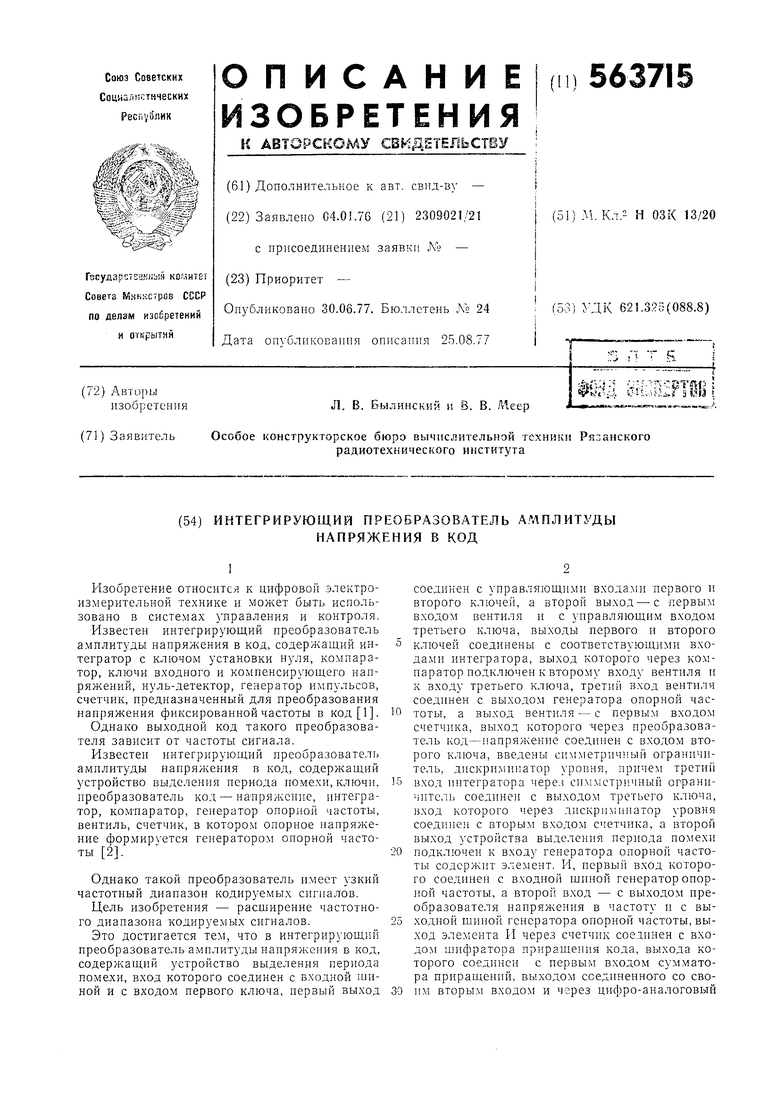

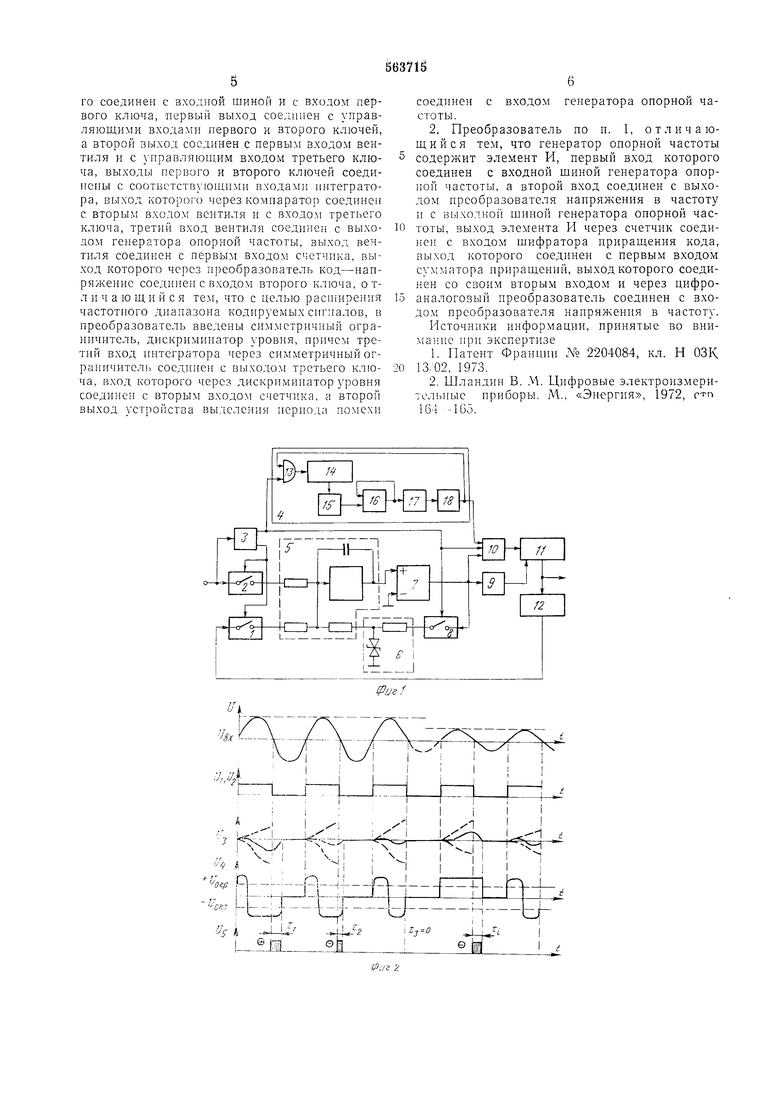

преобразователь с входом преобразователя напряжения в частоту. На- фит. 1 приведена структурная схема предлагаемого преобразователя; па фпг. 2-временные диаграммы, поясияющне прппцип работы преобразователя. Интегрнруюгцпй преобразователь амплптуды напряженпя в код еодерж11Т ключп 1 и 2, устройство 3 выделеппя перпода помехи, генератор 4 опорной частоты, интегратор о, симметричный ограничитель 6, комнаратор 7, ключ 8, дискриминатор 9 уровня, вентиль 10, счетчик II, нреобразователь 12 код - папряжеппе, элемент И 13, счетчик 14, Н1пфратор 15 приращения кода, сумматор 16 прпращенн, цнфро-апалоговый нреобразовате;1ь 17 п преобразователь 18 нанряжепия в частоту. Преобразователь работает следующим образом. Синусоидальное входное иаиряжение поступает на вход устройства 3 выделепия периода помехи, парафазпые выходы которого вырабатывают сигналы, унравля ощне режимами работы преобразователя. При поетупленип положительной полуволны кодируемого наиряжения ключп 1 н 2 открываются унравляюнхпмп сигналами с устройства 3 выделения периода помехи и интегратор 5 интегрирует входное напряжение и 11апряжепие нротнвоноложной нолярпоети преобразователя 12 код - напряжение. Такт интегрирования длится полнерпода Т/2 коднруемого нанряженпя. В течение этого времени унравляющим сигналом с второго выхода устройства 3 ключ 8 разомкнут п занрещепа работа вентиля 10. Затем ключи 1 и 2 размыкаются, ключ 8 замыкается, а с вентиля 10 снимается сигнал занрета. Если выходное напряжение на выходе интегратора о не равно пулю, па выходе компаратора 7 образуется папряжеппе того же знака, что и на выходе интегратора 5, которое через еимметрнчпый ограппчитель 6, пмеющпй порог ограниченпя Uoi-p, прикладываегся к третьему входу интегратора 5 и разряжает конденсатор интегратора 5 до нулевого значения за время т. Выходным сигналом с компаратора 7 на время т открывается вентиль 10, который пропуекает ечетпые импульсы с генератора 4 опорной частоты на счетчик И. В зависимости от знака выходного напряжепия компаратора 7 диекримипатор 9 устапавливает режим работы счетчика: нри нолол ительном нанряжении -вычитание, нри отрицательном - суммирование. Когда выход интегратора 5 и одновременно с ним выход компаратора 7 принилтет пулевое зиачение, запрещается работа вептиля 10. В дальнейшем выход интегратора 5 удерживается па пулево.м уровне до начала следуюн;его такта игггегрировапия за счет следящей обратной связи, образованной компаратором 7, ключом 8, симметричным ограннчителем 6. Новое значение кода счетчика 11 постуиает и 1 1 -(1 -5 30 35 5 5J 55 65 на преобразователь 12 код-папряжение, выходное нанряженне которого в 1ювом такте интегрирования подается через ключ 1 :та интег)атор о. При уета)1овпвп1емся режпме работы интегрирующего преобразователя напряжепия в копне такта интегрирования становится равным нулю и временной интервал т не формируется. В этом случае значение кода счетчика 1 1 пронорнионально амн.чптуде входного нанряже 1ия. Чтобы диапазон кодир емых амплитуд синусондального сигнала не завнсел от его частоты, генератор 4 опорной частоты меняет частоту счетных имн)льсов в зависи.мости от частоты входного сигнала. ,Для этого временной интервал, равный по;1овпне пернода кодируемого напряжения, иодается на элеме1гг И с выхода устройства. В течешю этого времени счетчик 14 фиксирует чис;ю нмнул|,сов, поступивших па пего с преобразователя 18. При различиых изменениях частоты кодируемого си Ч1ала частота FQ генератора 4 устанавливается такой велпчипы, чтобы за И1ггервал 1/2/ в счетчике 14 фиксирова,тось определенное количество имиульсов Ло. Прн отклонеппи числа импульсов от опорного значения Ло шифратор 15 вырабатывает код и)н)ап1еиия, который с учетом знака суммир}т тся с содержимым накаиливаюи его сумматора 16. Повое значение кода ноступает на нифро-аналоговьи нреобразователь 17, управлиюни1Й преобразователем 18 нанряжения в частоту. В соответствии е выходным 1анряжением цифро-аналогового преобразователя 17 из.меняется частота /о, чтобы отклонением числа имну.тьсов, зафикеироваииых в ечетчике 14, от оиорпого зпачения Ло нривестн к нулю. 4акн.м образом, в нредлагаемом преобразователе в нервом такте интегрирования на интегратор одновремеппо поступают два нанряженпя: кодпруемое и компенсирующее с преобразователя код - напряжение, а чаетота счетных импульсов, зависящая от частоты кодируемого сигнала, вырабатывается генератором опорпой частоты. Это дает возможность кодировать и сохрапять диапазоп кодируемых амилитуд синусондального сигнала независимо от его частоты. Кроме того, в нредлагаемом нреобразователе не требуется высокая стабильность частоты счетных имнульсов, точность кодирования не зависит от интегрирующего кондеиеатора, симметричного ограничителя п компаратора. К симметричному ограничителю нредъявляется ли1нь требование равенства верхнего н нижнего уровней ограничения, а влияние норога срабатывания компаратора устранено за счет пременення следящей обратной связи. Фор м у л а и 3 о б р е т е н и я 1. Интегрирующий преобразователь амплигуды нанряжения в код, содержащий устройство выделенпя перпода помехи, вход которого соединен с входной шинои и с входом первото ключа, первый выход соедннен с управляющими входами первого и второго ключей, а второй выход соединен с первым входом вентиля и с управляющим входом третьего ключа, выходы первого и второго ключей соедииепы с соответствующими входами интегратора, выход кото;)ог() через компаратор соединен е вторым входом вентиля и с входом третьего ключа, третий вход вентиля соединен с выходом геиератора опорной частоты, выход вентиля соединен с первым входом счетчика, выход которого через преобразователь код-напряжение соедпиен с входом второго ключа, отличающийся тем, что с целью расн1ирен Я частотного диапазона кодируемых еигналов, в преОбразователь введены симметричный ограничитель, дискримииатор уровня, причем третий вход интегратора через симметричный ограничител) соединеи с выходом третьего ключа, вход которого через дискримииаторуровня соединен с вторым входом счетчика, а второй выход устройства выделения периода помехи

соединен с входом генератора опорной частоты.

2. Преобразователь по п. 1, отличающийся тем, что генератор опорной частоты содержит элемент И, первый вход которого соединен с входной щиной генератора опорной частоты, а второй вход соединен с выходом нреобразователя напрял ения в частоту и с выходной гппной генератора опорной частоты, выход элемента И через счетчик соединен с входом шифратора приращения кода, выход которого соединен с первым входом cyNSMaTOpa приращений, выход которого соединен со своим вторым входом и через цифроаналоговый преобразователь соединен с входом преобразователя нанряжепия в частоту. Источники информации, принятые во внимание при эксперт)1зе

1.Патент Франции Л 2204084, кл. Н ОЗК 13/02, 1973.

2.Шландин В. . Цифровые электроизмерительные приборы. М., «Энергия, 1972, гтп

164 --165.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU1056449A1 |

| Интегрирующий преобразователь аналог-код | 1981 |

|

SU962992A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1978 |

|

SU741459A1 |

| Интегрирующий преобразователь "аналог-код | 1980 |

|

SU903903A1 |

| Устройство время-импульсного преобразования | 1978 |

|

SU731577A1 |

| Способ измерения напряжений постоянного тока и устройство для его осуществления | 1981 |

|

SU974577A1 |

| Интегрирующий многошаговый аналогоцифровой преобразователь | 1971 |

|

SU472453A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Устройство для измерения температуры | 1984 |

|

SU1268970A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1978 |

|

SU769734A1 |

Авторы

Даты

1977-06-30—Публикация

1976-01-04—Подача