(54) ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий преобразователь "аналог-код | 1980 |

|

SU903903A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1056449A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| Дифференциально-трансформаторный преобразователь аналог-код | 1980 |

|

SU1005127A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

Изобретение относится к преобразованию аналоговых сигналов постоянного тока в цифровые коды и может .быть использовано в качестве аналого-цифрового преобразователя в системах сбора и обработки данных.

Известен интегрирующий аналогоцифровой преобразователь, использующий метод двутактного интегрирования для преобразования сигналов постоянного тока в код и содержащий интегратор, компаратор, схему управления и переключающие схемы

Однако известный преобразователь обеспечивает эффективное подавление помех при аналого-цифровом преобразовании только в том случае, если период помехи совпадает с длительностью первого такта интегрирования.

Известен также аналого-цифровой преобразователь, который для повышения эффективности подавления помехи содержит специальные устройства, осуществляющие подстройку времени преобразователя в зависимости от частоты и фазы помехи 2.

Данный преобразователь является медленнодействующим и требует интервала времени в несколько периодов помехи.

Наиболее близким к предлагаемому по технической сущности является устройство аналого-цифрового преобразования, состоящее из интегратора с двумя ключами на входе и одним ключом в цепи обратной связи интегратора, компаратора, формирователя импульсов, двух счетчиков, генератора импульсов, триггера со счетным

10 входом, RS-триггера и пяти схем И.

Данное устройство работает по методу двута.ктного интегрирования На первом такте входное напряжение интегрируется в течение интервала

15 времени, равного периоду помехи. При этом для того, чтобы колебания частоты помехи не влияли на степень ее подавления и на стабильность коэффициента передачи преобразователя,

20 первый такт интегрирования разбит .на два интервала, отстоящих друг от друга на половину периода помехи. На втором такте интегрируется напряжение опорного источника t3j.

25

Недостатками данного устройства являются невысокое быстродействие и сложность.

Быстродействие преобразователя определяется длительностью первого

30 и второго тактов интегрирования.

Дл-итедьность перво1-о такта нитегрирования в целях помехоподавления равна периоду помехи. Длительность второго такта интегрирования выбирается равной длительности первого такта интегрирования, при этом упрощается синхронизация преобразователя и повышается его линейность.

Таким образом, быстродействие данного преобразователя равно двум .периодам помехи.

Сложность устройств.а определяется наличием значительного числа логических элементов„

Цель изобретения повышение быстродействия и упрощение устройства.

ПocтaвлeнE aя цель достигается тем, что в интегрирующий преобразователь аналог-крд, содержащий операционный усилитель, вход которого через последовательно соединенные первый ключ и первый масштабный резистор подключен к сигнальному входу, а через последовательно соединенные второй ключ и второй масштабный резистор - ко входу опорного напряжения преобразователя и через интегрирующий конденсатор - к выходу операционного усилителя, соединенному с первым входом компаратора, второй вход которого подключен ко входу опорного напряжения преобразователя, счетчик, выходкоторого является выходом преобразователя, счетный вход соединен с выходом элемента И, а вход сброса подключен к первому выходу формирователя, импульсов, вход которого является тактирующим входом преобразователя, причем первый и второй элементы И соедин.ены соответственно с выходом генератора импульсов и прямым выходом . триггера, введен третий масштабный резистор, включенный между выходом операционного усилителя и общим выходом первого ключа и первого масштабного резистора, управляющие входы первого и второго ключей соединены соответственно с инверсным и выходами триггера, нулевой и единичный входы которого связаны соответственно с выходом рсомпаратора и вторым выходом форм15рователя импульсов.

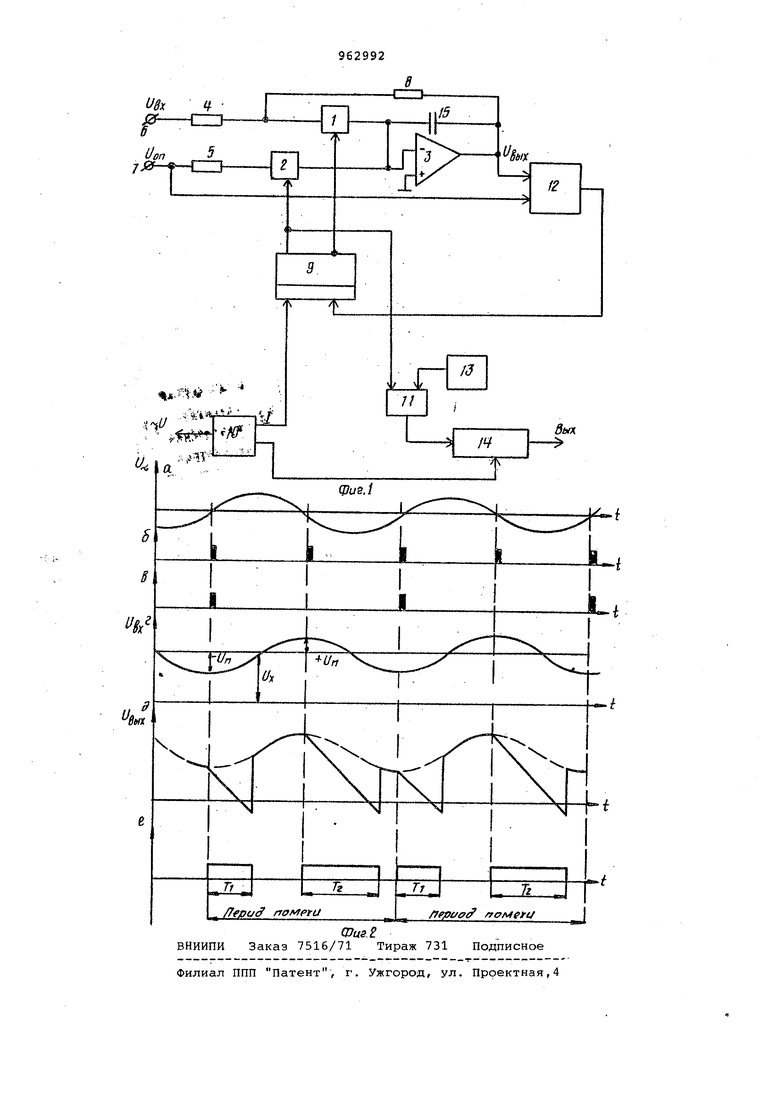

На фиг. 1 представлена .функционал-ьная cxeMSi интегрирующего преобразователя; на фиг. 2 - временная . диаграмма работы устройства.

Интегрирующий преобразователь аналог-код (фиг.1) содержит ключи 1 и 2, выходом соединенные с входом операционного усилителя 3, а входом 1ерез масщтабн 1е резисторы 4 и 5 с сигнальным входом 6 и входом 7 опорного напряжения, масштабный резистор 8, соединенный с общим выводом ключа 1 и резистора 4, а другим.выводом с выходом операционного усилителя 3

триггер 9, управляющий ключами 1 и 2, формирователь-10 импульсов, элемент И 11, компаратор 12, генератор 13 импульсов, счетчик 14 и конденсатор 15, .Включенный.в цепь обратной

связи операционного усилителя 3.

Преобразоват.ель работает следующим образом..

На вход формирователя 10 импульсов поступает-управляющее переменное

0 напряжение (фиг.2а} с частотой, равной частоте помехи, которое преобразуется на выходах формирователя 10 в импульсы (фиг.2сГи -S) . Счетчик 14 сбрасывается в ноль в момент прихода импульса с выхода-формирователя 10 импульсов.

До момента времени t (фиг.2) ключ 1 замкнут, а ключ 2 разомкнут. Операционный усилитель 3 из-за налиQ чия прецизионного масштабного резистора. 8 работает в режиме повторителя входного сигнала,- при этом напряжение на выходе- операционного усилителя .3 повторяет входное напряжение

5 (фиг,2г и Э1 , .

В момент времени t (фиг.2) с выхода I формирователя 10, поступает импульс, который переключает триггер 9, устанавливая на прямом

0 его выходе состояние един:ицы. При этом ключ 1 размыкается, а ключ 2. замыкается. Напряжение на выходе операционного усилителя 3 запоминается на конденсаторе 15. Начинается первый такт интегрирования, при котором интегрируется опорное напряжение через замкнутый ключ 2. Одновременно в момент времени t через, элемент И Ц начинают поступать импульсы в счетчик 14 (фиг.26). . Когда напряжение на выходе операционного усилителя 3 будет равно напряжению срабатывания компаратора, на его выходе появляется импульс,

tc который перебрасывает триггер 9 в исходное состояние. Ключ 1 замыкается, ключ 2 размыкается и элемент И 11 запирается., прекращая поступление импульсов на счетчик 14. Операционный усилитель 3 снова переводится в режим повторения входного -напряжения. В счетчике 14 .хранится код, соответствующий длительности первого интервала интегрирования Т (фиг.2е).

Ь в момент времени t,ji (фиг.2с5 на--, чинается второй такт Интегрирования напряжения. При этом импульсы, поступающие в счетчик в течение интервала ин-тегрирования T, суммируются с содер.жи1у1ым счетчика 14 за ив-, тервал времени Т. , На этом преобразование заканчивается.

В момент в.ремени t, счетчик 14 сбрасывается в начинается

65 новый цикл преобразования (фиг.26).

Так как мгновенные значения наложенной на сигнал помехи (фиг.Зг), отстоящие на половину периода помехи, равны по величине и противоположны по знаку, то сумма прёобразованньЕХ в код мгновенных значений ВХОДНОГО: сигнала (t и tj.) пропорциональна измеряемогду напряжению Uy и не содержит составляющих помехи.

Действительно, в момент t Сфиг.2с() преобразуется в код значе- ние входного, сигнала X а в момент t (фиг.2с{) - значение UgX-to. w Сумма кодов за два такта прямо пропорциональна преобразуемому напряжению Uj( и не содержит помехи, .

Таким образом, преобразователь осуществляет подавление наложенных на сигнал помех за счет преобразования в код мгновенных значений сигна ла, отстоящих на половину периода помехи, .

В предлагаемом преобразователе отсутствует такт интегрирования входного напряжения, а вместо него введен такт интегрирования опорного напряжения, :т,е. преобразователь также работает по методу двутактного интегрирования, тольков оба такта интегрируетсяопорное напряжение. Такое построение преобразователя позволяет объединить функции подавления помехи и преобразования напряжения Т од, за счет чего существенно увеличивается быстродействие преобразователя при сохранении его точности и помехоустойчивости.

Длительность преобразования в предлагаемом прео6раз6ва1;еле не превышает периода помехи (фиг.2е), что не менее чем в два раза выше, чем в известном устройстве.

в промьшщенных системах сбора и обработки данных, работающих На .базе быстродейстйующих ЭВМ,- использование предлагаемого преобразователя позволяет увеличить быстродействие всей системы в -Два раза или же дает возможность подключить к данной системе в два раза .больше датчиков«

Предлагаемый преобразователь явля ется более простым по сравнеийю с известным, что позволяет увеличить

надежность преобразователя и сделать его более дешевым.

Формула изобретения

Интегрирующий преобразователь аналог-код, содержащий операционный усилитель, вход которого через последовательно соединенные первый ключ

И первый масштабный резистор подклю-. чен к сигнальному входу, а через последовательно соединенные второй ключ и второй масштабный резистор ко входу опорного напряжения преобразователя и через интегрирующий конг денсатор - к выходу операционного усилителя, соединенному с первым входом компаратора, второй вход которого подключен ко входу оп рного напряжения преобразователя, счетчик, выход

которого является выходом преобразоватёля, счетный вход соединен с выходом элемента И, а вход сброса подключен к первому выходу формирователя иьлпульсов, вход которого является тактирующим входом преобразователя, причем первый и второй входы элемента И соединены соответственно с выходом генератора импульсов и прямым

выходом триггера, отличающ и и с я тем, .что, с целью повышения быстродействия и упрощения, в него введен третий масштабный резистор, включенный между выходом операционного усилителя и общим выходом первого ключа и первого масштабного резистора/ управляющие входаа первого и второго ключей соединены соответственно q инверсным: и прямым выходами триггера нулевой и единичный входы

которого связаны соответственно с выходом компаратора и вторым выходом формиро:вателя импульсов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-30—Публикация

1981-02-26—Подача