1

Изобретение относится к областям техники, связанным с импульсно-кодовой модуляцией и цифровой вычислительной техникой.

Внедрение систем связи, предназначенных для передачи телевизионного сигнала методом и.миульсно-кодовой модуляции, совершенствование методов обработки изображений на ЭЦВМ обусловливают высокие требования к точности аналого-цифрового преобразователя (АЦП) и стабильности его работы в процессе длительной эксплуатации. Поэтому возникает задача контроля точности аналого-цифрового преобразования.

Известно устройство контроля АЦП сигналов изображения, в котором на вход контролируемого АЦП подается пилообразное напряжение. Выходы разрядов АЦП поочередно подаются на вход видеоконтрольного устройства, на экране которого возникает изображение кодовой таблицы того кода, с которым работает проверяемый преобразователь 1.

Недостатком такого контроля является нарушение функционирования АЦП в системе. Кроме того, контроль осушествляется визуально и поэтому точность его невысокая.

Наиболее близким по технической сущноСТ1И к предлагаемому является устройство, осушествляющее контроль частоты появления нулей в каждой паре соседних разрядов внутри кодовой группы при реальном информационном сигнале на входе АЦП, в котором выход аналого-цифрового преобразователя через преобразователь параллельного кода в последовательный и линию связи соединен с

входом преобразователя последовательного кода в параллельный, выходы которого соединены с цифро-аналоговым преобразователем. Вход преобразователя последовательного кода в параллельный через элемент И, устройство задерл :ки, второй элемент И соединен с входом интегратора. Вход преобразователя через элемент И-НЕ соединен с вторым входом второго элемента И. Выход интегратора через пороговое устройство и мультивибратор

соединен с входом третьего элемента И, второй вход которого через выделитель тактовой частоты соединен с входом преобразователя последовательного кода в параллельный. Выход третьего элемента И соединен с входом

цифрового счетчика. Выходы второй и третьей ячеек цифрового счетчика соединены с вторыми входами первого элемента И и элемента И-НЕ соответственно. Выходы всех ячеек цифрового счетчика соединены с управляющими входами преобразователя последовательного кода в параллельный 2.

Однако в рассмотренном устройстве: - не контролируется функционирование каждого разряда в отдельности;

- контроль производится лишь при нормальном законе распределения значений сигнала, подвергаемого аналого-цифровому преобразованию;

-контроль производится только при кодировании сигнала кодом Грея;

-контроль производится путем последовательного опроса разрядов АЦП, что приводит к большим временным затратам.

Цель изобретения - расширение функцио.нальных возможностей статистического контроля аналого-цифрового преобразователя сигналов изображения.

Это достигается тем, что в устройство, содержащее аналого-цифровой преобразователь, вход которого соединен с шиной входного сигнала, устройство задержки, интегратор, выход которого соединен с первым входом порогового устройства, введены п элементов Запрет I (п-1) эломентов Запрет II, (п--) устройств задержки, п сумматоров, (п-1) интеграторов, (л-1) пороговых устройств, п элементов И I, (п- 1) элементов И II, п элементов И III, п триггеров, дополнительное пороговое устройство, дополнительный элемент И, 2 я индикаторов, причем выход каждого разряда аналого-цифрового преобразователя соединен с первым входом соответствуюш,его элемента Запрет I, второй вход которого подключен к выходу элемента Запрет II, а выход соединен с первым входом сумматора данного разряда и через устройство задержки данного разряда с вторым входом сумматора данного разряда, через интегратор данного разряда соединен с первым входом порогового устройства данного разряда и вторым входом порогового устройства предыдуш;его разряда, первый выход порогового устройства соединен с первыми входами элементов И I и И II данного разряда, первым входом элемента Запрет II данного разряда и вторым входом элемента И II последующего разряда, второй выход порогового устройства соединен с вторыми входами элементов И I и И III последующего разряда и первым входом триггера данного разряда, второй вход которого подключен к выходу элемента И П1 данного разряда, первый выход триггера соединен с вторым входом элемента Запрет II предыдущего разряда, второй выход триггера -соединен с третьими входами элементов И I и И II предыдущего разряда, причем выход триггера первого разряда соединен с первым входом дополнительного элемента И, второй вход которого соединен с вторым входом элемента И П первого разряда и первым выходом дополнительного порогового устройства, второй выход которого соединен с вторыми входами элементов И I и И III первого разряда, первый вход дополнительного порогового устройства соединен с выходом интегратора первого разряда, а второй вход подключен к шине питания, первые входы элементов И III соединены с шнной сброса, выходы элементов И I, И II и дополнительного элемента И соединены с входами

соответствующих индикаторов, второй вход порогового устройства последнего «-го разряда соединен с шиной питания, а первый выход-с первым входом элемента И I и вторым входом элемента Запрет I данного разряда.

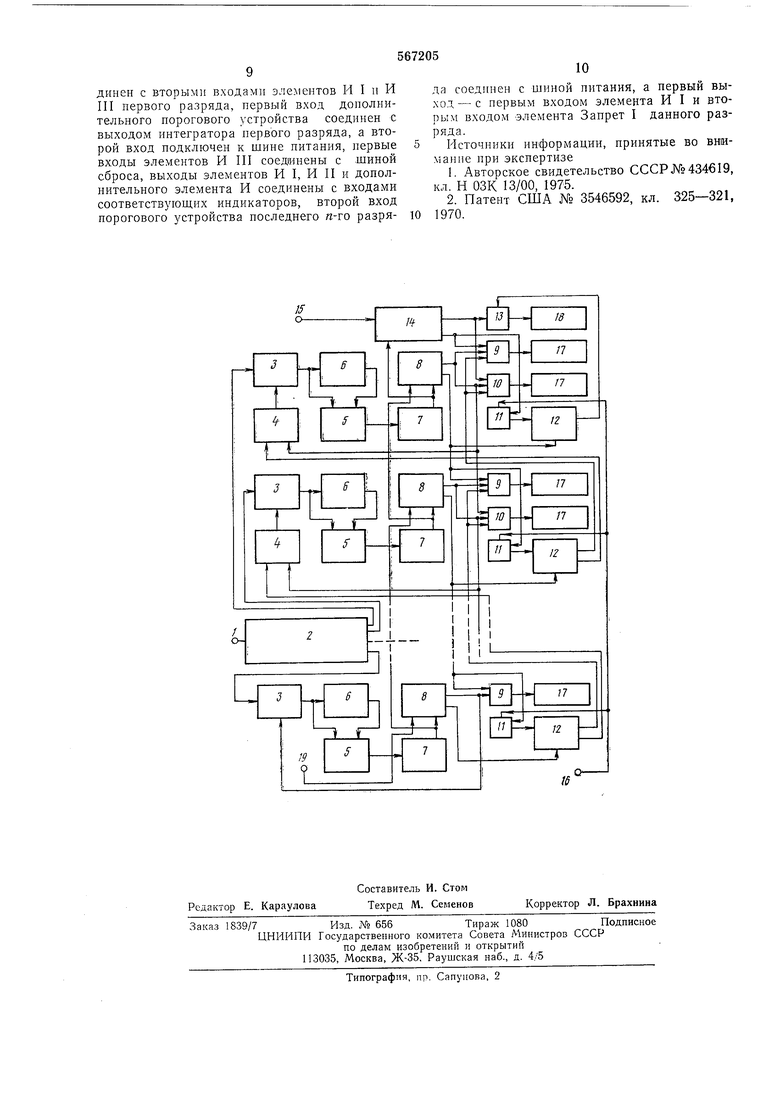

На чертеже показана структурная электричеслая схема предлагаемого устройства статистического контроля аналого-цифрового преОбразователя сигналов изображения.

Шнна I входного -сигнала через АЦЦ 2 соединена с входом каждого из п элементов Запрет I 3. Второй вход каждого элемента Запрет I 3 подключен к выходу элемента Запрет II 4, а выход соединен с первым входом сумматора 5 данного разряда и через устройство 6 задержки данного разряда с вторым входом сумматора 5 данного разряда. Выход сумматора 5 через интегратор 7 данного разряда соединен с первым входом порогового устройства 8 данного разряда и вторым входом порогового устройства 8 предыдущего разряда. Первый выход порогового устройства 8 соединен с первыми входами элементов

И I 9 и И П 10 данного разряда, первым входом элемента Запрет II 4 данного разряда и вторым входом элемента И П 10 последующего разряда. Второй выход порогового устройства 8 соединен с вторыми входами элементов И I 9 и И III 11 последующего разряда и первым входом триггера 12 данного разряда. Второй вход триггера 12 подключен к выходу элемента И III 11 данного разряда. Первый выход триггера 12 -соединен с вторым

входом элемента Запрет II 4 предыдущего разряда, а второй выход триггера 12 соединен с третьими входами элементов И I 9 и И П 10 предыдущего разряда. Первый выход триггера 12 первого разряда соединен с первым

входом дополнительного элемента И 13. Второй вход дополнительного элемента И 13 соединен с вторым входом элемента И II 10 первого разряда и первым выходом дополнительного порогового устройства 14. Второй выход

дополнительного порогового устройства 14 соединен с вторыми входами элементов И I 9 и И III 11 первого разряда, первый вход соединен с выходом интегратора 7 первого разряда, а второй вход подключен к шине 16 питания. Первые входы элементов И III 11 соединены с щиной 16 сброса. Выходы элементов И I 9 и И П 10 и дополнительного элемента И 13 соединены с входами соответствующих индикаторов 17 и 18. Второй вход порогового

устройства 8 последнего и-го разряда соединен с шиной 19 питания, а первый выход--с первым входом элемента И I 9 и вторым входом элемента Запрет I 3 данного разряда. Устройство работает следующим образом.

Телевизионный вещательный -аигнал по шине 1 входного сигнала поступает на вход

АЦП 2. Кодовые импульсы с выхода 1, 2

п-то разряда АЦП 2 поступают соответственно на вход 1, 2,..., tt-ro элемента Запрет I 3.

При наличии разрешающего потенциала на втором входе элемента Запрет I 3 данного разряда кодовые имлульсы через элемент Запрет I 3 поступают на первый вход сумматора 5по модулю два данного разряда и через устройство 6 задержки данного разряда на второй вход сумматора 5. Устройство 6 задержки осуществляет задержку кодовых импульсов на один такт, т. е. на период временной дискретизации вещательного телевизионного сигнала, производимой в АЦП 2. На выходе сумматора 5 возникает логическая «1 яри несовпадении двоичных сигналов на его входах. Таким образом, частота появления «1 на выходе сумматора 5 пропорциональна частоте изменения посылок или в цепи данного разряда АЦП 2. С выхода сумматора 5 Оигнал поступает на интегратор 7, напряжение Ui на выходе которого пропорционально вероятности появления «1 на выходе сумматора 5. С выхода интегратора 7 сигнал поступает на первый вход порогового устройства 8 данного разряда и второй вход порогового устройства 8 предыдущего разряда. На второй вход порогового устройства 8 данного разряда подается сигнал с выхода интегратора 7 последующего разряда. При нормальной работе п-разрядното АЦП 2 для напряжений на выходе интеграторов 7 должно выполняться соотношение ,.У, ...f7,..., (1) поскольку аналогичное соотношение можно записать для вероятностей изменения посылок Pi в цепях соответствующих разрядов АЦП 2: ....РК.. . (2) Соотношения (1) и (2) связаны со статистическими свойствами сигналов изображения, подвергаемых аналого-цифровому преобразованию, отличительной особенностью которых является сильная корреляционная связь между соседними значениями сигнала. Таким образом, вероятность скачка в сигнале с ростом величины скачка падает практически по экспоненте. Для переключения старшего разряда (например, 1-го) АЦП с меньшей частотой, чем у младшего (например, 2-го), надо, чтобы скачки большой величины происходили реже, чем скачки малой величины. Это выполняется для сигнала изображения и приводит к возникновению соотношений (1) и (2). В зависимости от соотношения напряжений на интеграторах 7 можно рассмотреть три режима работы устройства. 1. Первый разряд функционирует нормально:,f/,f/,,(3) где El - напряжение на шине 15 питания; i-ый разряд функционирует нормально: f/,,f/,y,+,; (4) га-й разряд функционирует нормально: ,.(5) где EZ - напряжение на шйне 19 питания. В этом случае с первого выхода порогового устройства 8 данного разряда логический «О поступает на первые входы элементов И I 9 и И И 10 данного разряда, второй вход элемента И И 10 последующего разряда и на первый вход элемента Запрет II 4 данного разряда. С выхода элемента Запрет II 4 логический «О поступает на второй вход элемента Запрет I 3 данного разряда. Таким образом, кодовые импульсы данного разряда беспрепятственно проходят через элемент Запрет I 3, а соответствующие индикаторы 17 и 18, в качестве которых можно использовать светодиоды, не гор.ят. 2. На выходах АЦП 2 возникают дополнительные переходы или О 1: ,f/,f/,; ,. В. этом случае пороговое устройство 8 данного разряда срабатывает, и логическая «1 с его первого выхода поступает на первые входы соответствующих элементов И I 9 и И II 10. На вторые входы элементов И I 9 и И II 10 поступают соответственно логические «1 и «О с первого и второго выходов порогового устройства 8 предыдущего разряда. ТаКИМ образом, через элемент И I 9 логическая «1 поступает на индикатор 17, который загорается, указывая на возникновение дополнительных переходов или в данном разряде. Одновременно логическая «1 с первого выхода порогового устройства 8 данного разряда через элемент Запрет II 4 поступает на второй вход элемента Запрет I 3 данного разряда. Кодовые импульсы перестают проходить через элемент Запрет I 3, элемент Запрет II 4 или сумматор 5. Пороговое устройство 8 данного разряда переключается в исходное состояние, индикатор 17 гаснет, кодовые импульсы снова беспрепятственно: проходят через элемент Запрет I 3. Напряжение на интеграторе 7 снова начинает возрастать, что приводит к срабатыванию порогового устройства 8 и индикатора 17, и т. д. Таким образом, индикатор 17, мигая, указывает на дополнительные переходы в t-м разряде, а напряжение (7, на выходе интегратора 7 данного разряда автоматически поддерживается в соответствии с соотношением . Колебательный процесс продолжается до устранения неисправности в цепи данного разряда и восстановления соотношения , 3. На выходах АЦП 2 происходит недопустимое уменьшение -числа перехода или 0-1: Е,и,и,Ui-i U,, ,, u,Un-. в этом случае пороговое устройство 8 данного разряда остается в исходном положении, а срабатывает пороговое устройство 8 предыдущего (f- 1)-го разряда, так как для него нарушается соотношение . При этом в цепи предыдуш,его разряда возникает колебательный процесс, аналогичный описанному выше для цепи данного разряда, и автоматически поддерживается соотношение Ui-i Л;; f/t ;f/j-2- Соотношение приводит к срабатыванию порогового устройства 8 в цепи (/ - 2)-го разряда. При этом логические «1 и «О соответтсвенно с оервото и второго выходов порогового устройства 8 (i - 2)-го разряда поступают на вторые входы элементов И I 9 и И II 10 в цепи (i- 1)-го разряда, и сигнал с первого выхода порогового устройства 8 в депи (t- 1)-,го разряда поступает через элемент И II 10 в цепи (/-1)-го разряда на индикатор 18, который указывает на недопустимое уменьшение числа переходов 1 0 или в данном -/-ом разряде. Срабатывание порогового устройства 8 в цепи (/-1)-го разряда устанавливает -соответствующий триггер 12 в такое состояние, что логический «О с его второго выхода подается на третьи входы элементов И I 9 и И II 10 в цепи (i - 2)-го разряда, препятствуя тем самым срабатыванию индикатора 17 в цепи (i - 2)-го разряда от логической «1 на первом выходе порогового устройства 8 в (t -2)-м разряде. Логическая «1 с первого выхода триггера 12 в цепи (i- 1)-го разряда поступает на второй вход схемы Запрет II 4 в цепи (i - 2)-го разряда, тем самым разрывая петлю обратной связи в цепи (i - 2)-го разряда. Таким образом, пороговое устройство 8 в цепи (j - 2)-го разряда после срабатывания остается в этом состоянии до восстановления исходных соотношений напряжений на выходах интеграторов 7 и обеспечивает устойчивую индикацию недопустимого уменьшения числа переходов или в -м разряде. После устранения неисправности соответствующая индикация прекраш,ается. Однако для восстановления функциональных возможностей устройства необходимо установить триггер 12 в цепи (г-1)-го и ()-го разрядов в исходное состояние. Для этого на их вторые входы через соответствующие элементы И III И поступают импульсы сброса с щины 16. Элементы И 1П 11 управляются сигналом с второго выхода порогового устройства. 8 в цепи предыдущего разряда. Это необходимо для того, чтобы не произощло восстановления цепи обратной связи в цепи (i - 2)-го разряда при сработавшем соответствующем пороговом устройстве 8, что может привести к ложной индикации. Индикация недопустимого уменьшения числа переходов О 1 или в первом разряде производится при логической «1 на первом выходе дополнительного порогового устройства 14 индикатором 18 при отсутствии логического «О на втором входе дополнительного элемента И 13. Таким образом, индикация недопустимого увеличения числа переходов О 1 или производится индикаторами 17, а уменьшения-индикаторами 18. Формула изобретения Устройство статистического контроля аналогоцифрового преобразователя сигналов изображения, содержашее аналого-цифровой преобразователь, вход которого соединен с шиной входного сигнала, устройства задержки, интегратор, выход которого соединен с первым входом порогового устройства, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены я элементов Запрет I, (п- 1) элементов Запрет II, (п- 1) устройств задержки, п сумматоров, (п-1) интеграторов, («-1) пороговых устройств, п элементов И I, (п-1) элементов И II, п элементов И III, п триггеров, дополнительное пороговое устройство, дополнительный элемент И, 2 о индикаторов, причем выход каждого разряда аналого-цифрового преобразователя соединен с первым входом соответствующего элемента Запрет I, второй вход которого подключен к выходу элемента Запрет II, а выход соединен с первым входом сумматора данного разряда и через устройство задержки данного разряда с вторым входом сумматора данного разряда, через интегратор данного разряда соединен с первым входом порогового устройства данного разряда и вторым входом порогового устройства предыдущего разряда, первый выход порогового устройства соединен с первыми входами элементов И I и И II данного разряда, первым входом элемента Запрет 11 данного разряда и вторым входом элемента И II последующего разряда, второй выход порогового устройства соединен с вторыми входами элементов И I и И III последующего разряда и первым входом триггера данного разряда, второй вход которого подключен к выходу элемента И III данного разряда, первый выход триггера соединен с вторым входом элемента Запрет II предыдущего разряда, второй выход триггера соединен с третьими входами элементов И I и И II предыдущего разряда, причем выход триггера первого разряда соединен с первым входом дополнительного элемента И, второй вход которого соединен с вторым входом элемента И II первого разряда и первым выходом дополнительного порогового устройства, второй выход которого соединен с вторыми входами элементов И I и И III первого разряда, первый вход дополнительного порогового устройства соединен с выходом интегратора первого разряда, а второй вход подключен к шине питания, первые входы элементов И III соединены с шиной сброса, выходы элементов И I, И II и дополнительного элемента И соединены с входами соответствующих индикаторов, второй вход порогового устройства последнего «-го разряда соединен с шиной питания, а первый выход - с первым входом элемента И I и вторым входом элемента Запрет I данного разряда.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР№434619, кл. Н ОЗК 13/00, 1975.

2.Патент США № 3546592, кл. 325-321, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1974 |

|

SU738153A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU855993A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1027814A2 |

| Спектральный анализатор | 1984 |

|

SU1275468A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2552147C1 |

| Устройство цифровой передачи и приема телевизионного сигнала | 1985 |

|

SU1309327A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Интегратор хроматографических данных | 1981 |

|

SU991443A1 |

| Система передачи и приема сигналов изображения | 1979 |

|

SU907869A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU924854A1 |

Авторы

Даты

1977-07-30—Публикация

1975-04-28—Подача