4

00

со

о со

№

314

Изобретение относится к радиотехнике и может быть использовано для получения дискретной сетки стабильных частот от одного источника опорных колебаний.

Целью изобретения является снижение потребления мощности от источника питания.

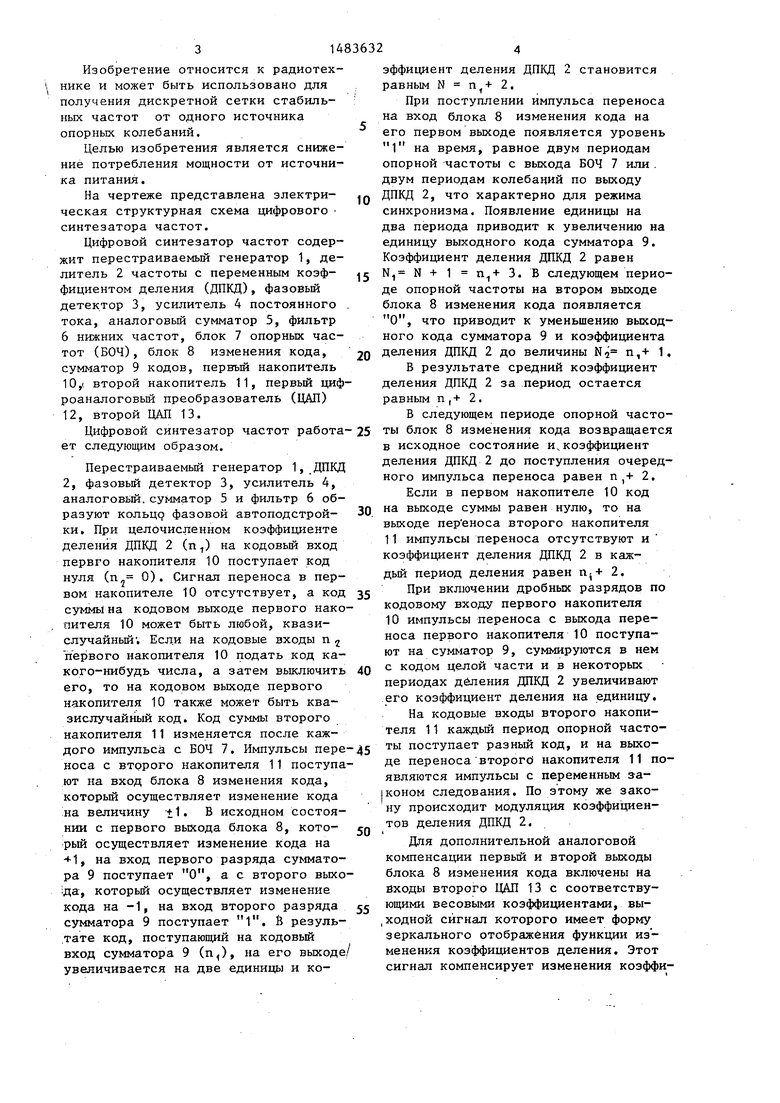

На чертеже представлена электрическая структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит перестраиваемый генератор 1, делитель 2 частоты с переменным коэффициентом деления (ДПКД), фазовый детектор 3, усилитель 4 постоянного

тока, аналоговый сумматор 5, фильтр

де опорной частоты на втором выходе блока 8 изменения кода появляется О, что приводит к уменьшению выходного кода сумматора 9 и коэффициента деления ДПКД 2 до величины N n,+ 1,

В результате средний коэффициент деления ДПКД 2 за период остается равным п,+ 2.

В следующем периоде опорной часто6 нижних частот, блок 7 опорных частот (БОЧ), блок 8 изменения кода, 20 сумматор 9 кодов, первый накопитель 10, второй накопитель 11, первый циф- роаналоговый преобразователь (ЦАП) 12, второй ЦАП 13.

Цифровой синтезатор частот работа- 25 ты блок 8 изменения кода возвращается ет следующим образом.в исходное состояние ичкоэффициент

Перестраиваемый генератор 1, ДПКД 2, фазовый детектор 3, усилитель 4, аналоговьй.сумматор 5 и фильтр 6 об-

30

разуют кольцо фазовой автоподстройки При целочисленном коэффициенте деления ДПКД 2 (п,) на кодовый вход первго накопителя 10 поступает код нуля (п, 0). Сигнал переноса в первом накопителе 10 отсутствует, а код 35 суммы на кодовом выходе первого накопителя 10 может быть любой, квазислучайный . Если на кодовые входы n 2 первого накопителя 10 подать код какого-нибудь числа, а затем выключить 40 его, то на кодовом выходе первого накопителя 10 также может быть квазислучайный код. Код суммы второго накопителя 11 изменяется после кажделения ДПКД 2 до поступления очередного импульса переноса равен п,+ 2.

Если в первом накопителе 10 код на выходе суммы равен нулю, то на выходе пер еноса второго накопителя 11 импульсы переноса отсутствуют и коэффициент деления ДПКД 2 в каждый период деления равен п(+ 2.

При включении дробных разрядов по кодовому входу первого накопителя 10 импульсы переноса с выхода переноса первого накопителя 10 поступают на сумматор 9, суммируются в нем с кодом целой части и в некоторых периодах деления ДПКД 2 увеличивают его коэффициент деления на единицу.

На кодовые входы второго накопителя 11 каждый период опорной частодого импульса с БОЧ 7. Импульсы пере-45 ты поступает разный код, и на вько- носа с второго накопителя 11 поступают на вход блока 8 изменения кода, который осуществляет изменение кода на величину + 1. В исходном состоянии с первого выхода блока 8, кото- JQ рый осуществляет изменение кода на +1, на вход первого разряда сумматора 9 поступает О, а с второго выхода, который осуществляет изменение кода на -1, на вход второго разряда 55 сумматора 9 поступает 1. В результате код, поступающий на кодовый вход сумматора 9 (п), на его выходе/ увеличивается на две единицы и коде переноса второго накопителя 11 появляются импульсы с переменным законом следования. По этому же закону происходит модуляция коэффициентов деления ДПКД 2.

Для дополнительной аналоговой компенсации первый и второй выходы блока 8 изменения кода включены на входы второго ЦАП 13 с соответствующими весовыми коэффициентами, выходной сигнал которого имеет форму зеркального отображения функции изменения коэффициентов деления. Этот сигнал компенсирует изменения коэффиэффициент деления ДПКД 2 становится равным N 2.

При поступлении импульса переноса на вход блока 8 изменения кода на его первом выходе появляется уровень 1 на время, равное двум периодам опорной частоты с выхода БОЧ 7 или двум периодам колебаний по выходу ДПКД 2, что характерно для режима синхронизма. Появление единицы на два периода приводит к увеличению на единицу выходного кода сумматора 9. Коэффициент деления ДПКД 2 равен j . В следующем перио0

де опорной частоты на втором выходе блока 8 изменения кода появляется О, что приводит к уменьшению выходного кода сумматора 9 и коэффициента деления ДПКД 2 до величины N n,+ 1,

В результате средний коэффициент деления ДПКД 2 за период остается равным п,+ 2.

В следующем периоде опорной частоделения ДПКД 2 до поступления очередного импульса переноса равен п,+ 2.

Если в первом накопителе 10 код на выходе суммы равен нулю, то на выходе пер еноса второго накопителя 11 импульсы переноса отсутствуют и коэффициент деления ДПКД 2 в каждый период деления равен п(+ 2.

При включении дробных разрядов по кодовому входу первого накопителя 10 импульсы переноса с выхода переноса первого накопителя 10 поступают на сумматор 9, суммируются в нем с кодом целой части и в некоторых периодах деления ДПКД 2 увеличивают его коэффициент деления на единицу.

На кодовые входы второго накопителя 11 каждый период опорной частоты поступает разный код, и на вько-

де переноса второго накопителя 11 пявляются импульсы с переменным законом следования. По этому же закону происходит модуляция коэффициентов деления ДПКД 2.

Для дополнительной аналоговой компенсации первый и второй выходы блока 8 изменения кода включены на входы второго ЦАП 13 с соответствующими весовыми коэффициентами, выходной сигнал которого имеет форму зеркального отображения функции изменения коэффициентов деления. Этот сигнал компенсирует изменения коэффциентов деления, связанные с образованием импульсов переноса второго накопителя 11, т.е. с модуляцией коэффициентов деления, а изменения, связанные с изменением суммы на кодовом выходе второго накопителя 11, компенсируются при помощи первого ЦАП 12.

Сигналы первого и второго ЦАП 12 и 13 поступают на аналоговый сумматор 5 со своими весовыми коэффициентами, которые зависят от параметров кольца фазовой автоподстройки.

Поскольку изменение коэффициентов деления ДПКД 2 на величину fl производится с помощью сумматора 9 по установочному входу ДПКД 2 на частоте в п раз ниже частоты перестраиваемого генератора 1, это позволяет снизить потребляемую мощность от источников питания. Соединение тактовых входов первого и второго накопителей 10, 11 и блока 8 изменения кода с выходом БОЧ 7 позволяет также уменьшить время точной подстройки на нужную частоту, так как программа управления коэффициентами деления в ДПКД 2 не зависит от его входной частоты.

Формула изобретения

Цифровой синтезатор частот, содержащий соединенные в кольцо перестраиваемый генератор, делитель частоты с переменным коэффициентом деления, фазовый детектор, усилитель

10

15

836326

постоянного тока, аналоговый сумма- тор и фильтр нижних частот, блок - опорных частот, выход которого подключен к другому входу фазового детектора, первый и второй цифроанало- говые преобразователи, выходы которых подключены соответственно к второму и третьему входам аналогового сумматора, отличающийся тем, что, с целью снижения потребления мощности от источника питания, в него введены последовательно соединенные первый накопитель, второй накопитель, блок изменения кода и сумматор кодов, выход и вход переноса которого подключены соответственно к установочному входу делителя частоты с переменным коэффициентом деления, и к выходу переноса первого накопителя информационный выход . второго накопителя соединен с входом первого цифроаналогового преобразователя, тактовые входы первого накопителя, второго накопителя и блока изменения кода объединены и подключены к выходу блока опорных частот, второй выход блока изменения кода соединен с вторым входом сумматора 30 кодов, а первый и второй выходы

блока изменения кода подключены соответственно к первому и второму входам второго цифроаналогового преобразователя, кодовые входы первого накопителя и сумматора кодов являются соответственно входом дробной части и входом целой части коэффициентов деления.

20

25

35

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1987 |

|

SU1501265A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

Изобретение относится к радиотехнике и м.б. использовано для получения дискретной сетки стабильных частот от одного источника опорных колебаний. Цель изобретения - снижение потребления мощности от источника питания. Цифровой синтезатор частот содержит перестраиваемый г-р 1, делитель частоты 2 с переменным коэффициентом деления (ДПКД), фазовый детектор 3, усилитель 4 постоянного тока, аналоговый сумматор 5, фильтр 6 нижних частот, блок 7 опорных частот, два ЦАП 12 и 13. Для достижения цели введены блок 8 изменения кода, сумматор 9 кодов и два накопителя 10 и 11. Поскольку изменение коэффициентов деления ДПКД 2 на величину ± 1 производится с помощью сумматора 9 по установочному входу ДПКД 2 на частоте, в N1 раз ниже частоты г-ра 1, то снижается потребление мощности от источников питания. Соединение тактовых входов накопителей 10, 11 и блока 8 с выходом блока 7 позволяет также уменьшить время точной подстройки на нужную частоту. 1 ил.

| Способ выращивания дрожжей | 1950 |

|

SU89719A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ВОЛНОВАЯ ЗУБЧАТАЯ ПЕРЕДАЧА | 1997 |

|

RU2117198C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-30—Публикация

1986-12-30—Подача