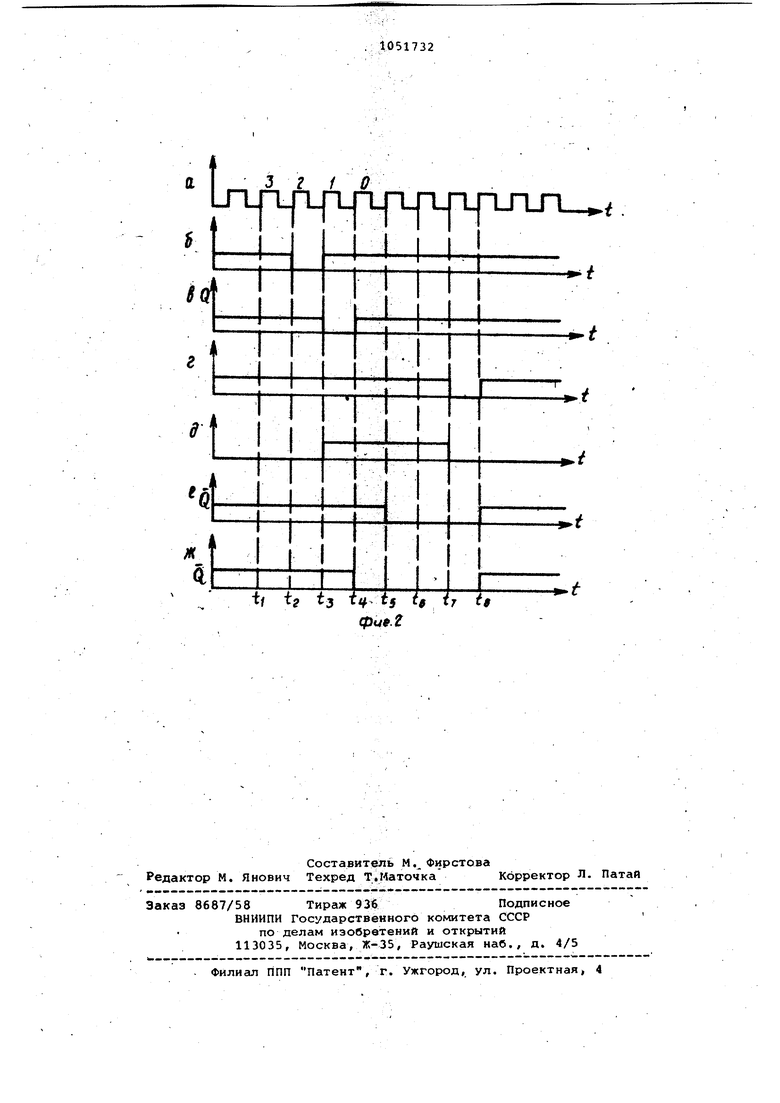

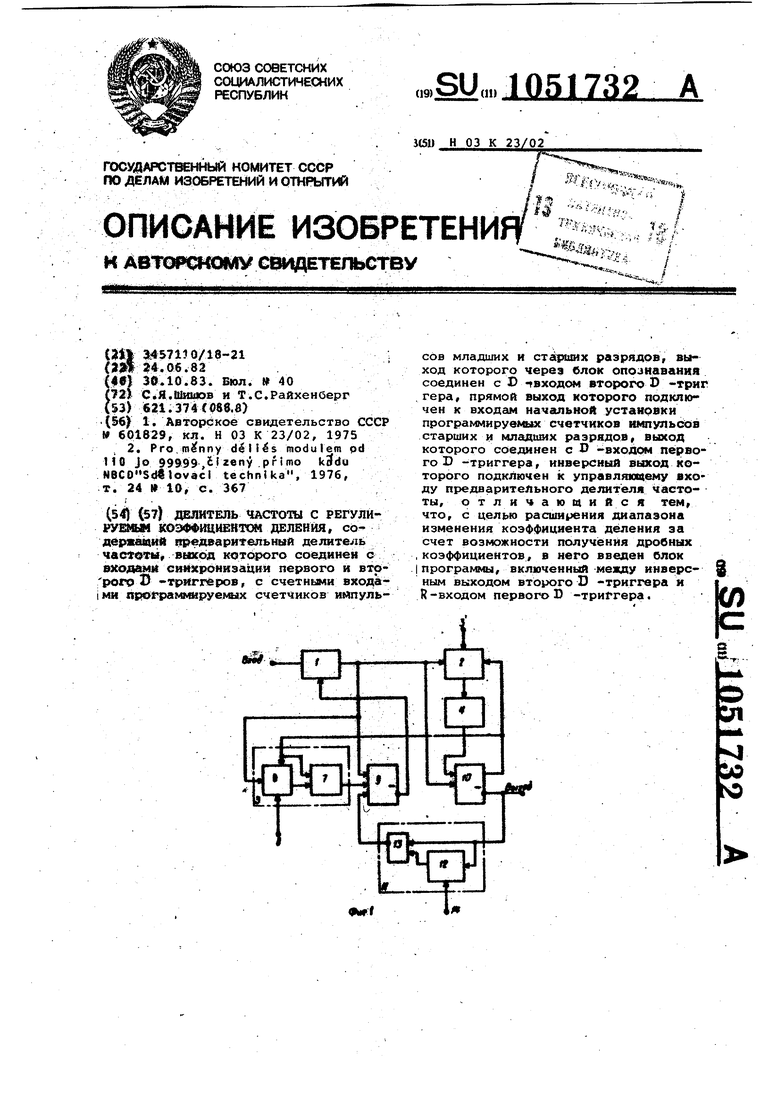

Изобретение относится к импуль ной технике и автоматике и может быть использовано, в аппаратуре об работки цифровой информации. Известен управляемый делитель частоты, содержащий предварительны делитель частоты с двумя коэффициентами деления, программируемый сч чик, делитель частоты с переменным коэффициентом деления, блок введения единичных приращений, блок управления и управляемый преобразова тель параллельного кода в последовательный (блок программы ) f| , Недостатком данного устройства является егоСЛОЖНОСТЬ вследствие наличия специального блока введения единичных приращений. Наиболее близким по технической сущности к предлагаемому является делитель частоты с переменным коэффициентом деления, содержащий предварительный делит,ель частоты, выполненный на четырех D -триггера и трех логических элементах типа 2И-НЕ, выход которого соединен с входами синхронизации первого и вт рого D -триггеров, со счетным входом программируемого счетчика млад ших разрядов, выполненного на реве сивном счетчике единиц коэффициента деления, логических элементах 2И-НЕ, 4ИЛИ-НЕ И инверторе, и со счетным входом программируемого счетчика старших разрядов, представляющего собой последовательное соединение реверсивных счетчиков д сятков, сотен, тысяч, десятков тысяч, сотен тысяч коэффициентов деления, выходы которого подключены к входам бло.ка опознавания, выполненного на четырех логических элементах ИЛИ-НЕ, двух инверторах и логическом элементе И-НЕ, выходом соединенного с D -входом второго D-триггера, прямой выход которого подключен одновременно к входу R тановки первого D -триггера, к вхо дам начальной установки программир емого счетчика старших разрядов и программируекюго счетчика младших разрядов, выходом соединенного с D-входом первого) -триггера, инверсный выход которого подключен к входу управления предварительного делителя. Причем первыйD-триггер необходИм в данном устройстве для нормирования задержки, возникающей при формировании сигнала управления коэффициентом деления предварительно го делителя, которая не должна пре иышать одного такта деления предва рительного делителя, что обеспечивает быстродействие всего устройст ва, равным быстродействию нерегули руемого делителя 2 , Недостатком известного устройства является невозможность попучения .нецелого коэффициента деления. Цель изобретения - расширение диапазона изменения коэффициента деления за счет возможности получения дробных коэффициентов «I Поставленная цель достигается тем, что в делителе частоты с регулируемым коэффициентом давления, содержащем предварительный делитель частоты, выход которого соединен с входами синхронизации первого и вто poroD-триггеров, со счеттлми входами программируемых счетчиков импульсов младших и старших разрядов, выход которого через блок опознавания соединен cD-входом второго-D -триггера, прямой выход которого подключен к входам начальной установки программируелых счетчиков импульсов старших и младших разрядов, выход которого соединен cD-входом первого D -триггера, инверсный выход которого подключен к управляющему входу предварительного} делителя частоты, .введен блок программы, включенный между инверсным выходом второго D -триггера и R -входом первого 1)-триггера. На фиг. 1 приведена структурная электрическая схема предлагаемого делителя частоты с регулируемым коэффициентом деления; на фиг. 2 временные диаграм1« 1, поясняющие рабО ту делителя частоты. Делитель частоты с регулируемым коэффициентом деления содержит пред&аритель1шй делитель 1 частоты с коэффициенто.м деления К или K-fl, (Программируемый счетчик 2 импульсов старших разрядов, шину 3 ввода параллельного кода управления счетчиком 2, блок 4 опознавания, программиpye &Iй счетчик 5 импульсов младших разрядов, состоящий из счетчика б импульсов с предварительной установкой кода и RS -триггера 7, шину 8 ввода параллельного кода управления счетчиком 5 импульсов младших разрядов, первый О-триггер 9, второй Г-триггер 10, блок 11 программы, состоящий из цифрового накопителя 12 и логического элемента 13 И-НЕ и шину 14 ввода параллельного кода управления блоком 11 программы; .. Выход предварительного делителя 1 соединен с входами синхронизации первого и второго D -триггеров 9 и 10 и со счетными входами счетчиков 2 и 6. Выход счётчика 2 соединен с блоком 4 опознавания, выход которого подключен KD -входу триггера 10, прямой выход которого соединен с входами установки начального кода счетчиков 2 и 6 и сS-входой RS-триггера 7. Инверсный выход второго

-триггера 10 является выходом всего устройства и, кроме того, соединен с входом синхронизации цифрового накопителя 12 и первым входом логического элемента 13 И-НЕ, второй вход которого подключен к выходу переноса цифрового накопителя 12, а выход соединен с R -входом первого D -триггера 9. Выход счетчика 6 соединен с Й-входомК5-триггера 7, вЫход которого подключен к1)-входу первого -триггера 9, инверсным выходом со единеииоро с входом управления предагфительного делителя 1. Через шины 3, 8 и 14 в счетчики 2 и 6 и цифро вой накопитель 12 подается параллель-15 ныя код управления старшими, млахвоими и дробными разрядами соответственно.

Устройство работает следующим образом.20

Программируемый счетчик 2 подсчи-. тывает количество тактов деления предварительного делителя 1. Колйчество тактов деления определяется кодом управления старшими разрядами. 25 Цикл счета счетчика 2 является циклом деления всего устройства. За два такта до окончания цикла счета счетчика 2 блок 4 формирует сигнал, который подготавливает к переключе- чл нию второй D -триггер 10 noD -входу. По следующему счетному импyJrIьcy с выхода предварительного делителя 1 за один такт до окончания цикла счета счетчика 2 второйD -триггер 10 переключается it вырабатывает импульс начальной установки кодов программируемых счетчиков 2 и 5, которые устанавливаются в начальное состояние. Импульс последнего цикла счета с выхода предварит ьного делителя 0 1 изменяет состояние счетчиков 2 и 5 и переключает второй D -триггер

10,тем самым заканчивая импульс, начальной установки. По импульсу начальной установки изменяет свое 45 состояние R5-триггер 7 и подготавли|Вает к переключению первый I) -триггер 9 noD-входу.

Бели дробные разряды оэффициенla деления равны нулю, то по им- 50 пульсу последнего такта цикла счета первыйD-триггер 9 не переключится, так как при этом на R -вход первого 0-триггера 9 воздействует импульс начальной установки с выхода блока ,

11,КОТО1Л1Й передает его с инверс- ного выхода второго) -триггера 10. Это необходимо потому, что счетчик

6 не считает импульс последнего такта цикла счета, позтому и переключение первого) -триггера 9 задёрживается на один такт. После переклю чения перйого D -триггера 9 в предварительном делителе 1 устанавливается коэффициент деления, равный , К+1. Счетчик б после отсчета необ-. 65

ходимого количества тактов деления на коэффициент К+1, задаваемого кодом управления младшими разрядами, формирует сигнал, который переключает RS -триггер 7. Паи этом изменяется информация на О -входе первого D -триггера 9. По следующему счетному импульсу с выхода предварительного делителя 1 первый) -триггер 9 переключается и формируется сигнал на установку в предварительном делителе 1 коэффициента. К. Таким образом, в начале цикла счетчик 2 подсчитывает определенное количество тактов деления предварительного делителя 1 с коэффициентом деления K-fl. Далее счетчик 2 подсчитывает такты деления предварительного делителя 1 с коэффициентом деления К до окончания цикла.счета счетчика 2.

Если дробные разряды коэффициент деления не равш нулю, то в некоторых циклах деления, определяе шх блоком 11, коэффициент деления всего устройства увеличивается на единицу. Это достигается тем, что блок 11 не пропускает в этих циклах импульс начальной установки на 9 -вход первого Р -триггера 9. При этом переключение первогоD -триггера 9 не задерживается на один такт, поэтому длительность сигнала с выхода первогхэ D -триггера 9 на установку в предварительном делителе 1 коэффициент увеличивается на один такт. В результате предварительный делитель 1 лишний раз делит частоту входного сигнала на К-И, что увеличивает коэффициент деления всего устройства на единицу. Порядок распределения циклов деления, в которы коэффициент деления всего устройства увеличивается на единицу, определяется принципом работы цифрового накопителя 12 и кодом К управления дробными разрядами. По каждрму выходному импульсу в цифровом накопителе 12 происходит добавление к его содержимому кода К управления дробными разрядами. При переполнении цифрового накопителя 12 на его выходе формируется логический нуль, который запрещает прохождение импульса начальной установки наR -вход первого В -триггера 9. Если емкость цифрового накопителя 12 равна MI то в К из М циклах деления всего устройства происходит переполнение цифрового накопителя 12. При этом коэффициент деления всего устройств увеличивается на величину, равную К/М, и ,дискретность изменения коэффициента деления равна 1/М.

В интервале времени t t tg , когда происходит формирование вторы D-триггером 10 импульса начальной установки и первым -триггером 9 сигнала на установку в предварительном делителе 1 коэффициента деления К4-1 и когда счетчики 2 и 6 работают а режиме обратного счета, и младший разряд коэффициента деления равен 3 (фиг, 2)f устройство работает следуняфнм образом. В момент времени t t счетчик 2 переходит из состояния три а состояние два (фиг. 2 а) , блок 4 опознавания переключается в состояние логического нуля (фиг. 25) и BTqpoftD -триггер 10 подготавливается по В -входу к переключению. В момент времени t tj счетчик 2 переходит в состояние сдан, (фиг. 2о) второй D-триггв р 10 переключается в состояние логического нуля по выходу Q (фиг. 2Ь)т.е. начинается импульс начальной установки, который записалеает в счетчик 2 код старших разря дов коэффициента деления,, в счетчик б - код младшего разряда ко&Ффициента деления равный 3, к переключает Йб-триггер 7 в состояние логической единишы (фиг. 2), подготавливакщий иоD -входу к переключению первый О-триггер 9. Следукмаий счетный импульс с выхода предварительного де лителя 1 в момент времени t t не может изменить записанного состояния счетчиков 2 и б, так как в этот момент времени заканчивается импульс начальной установки (фиг. 2Ь). Если,6лок 11 пропускает импульс начальной установки на/J -вход первого О-триггера то в момент времени первый)-триггер 9 заблокирован по R-входу и переключиться не может (фиг, 2е). В момент времени t 15 счетчики 2 и б начинают счет импульсов с выхода предварительного деЛителя 1 и первый 13 -триггер 9 по выходу Q, переключается в состояние логического нуля, который устанавливгет в предварит&1ьном делителе 1 коэффициент деления, равный К+}.. После отсчета счетчиком 6 трех импульсов в момент времени t « tf на выходе счетчика 6 форм фуется импульс (фиг. 2г) , переключающийRS-триггер 7в состояние логического нуля (фиг. .При этом первый) -триггер 9 подготавливается под -входу к переключению В кюмеит времени t « t первый)-триггер 9 педеключается в состояние логической единицы по выходу Q (фиг, 2е) и устанавливает в предварительном делителе 1 коэффициент деления/рав1швя К Таким образом, три раза в течение цикла деления всего устройства в промежутке времени 15 t &t предварительный делитель 1 имеет коэффициент деления К+1. Если блок 11 ие пропускает импульс начальной установки и на R-вход первого t) -триггера 9, то уже в момент времени t Ц первый 3)-триггер 9 переключится в состояние логического нуля по выходу Q и установит в предварительном делителе коэффициент деления,. равный К+1 (фиг, 2). Далее устройство работает аналогично описанному выше. 8результате четыре раза в течение Цикла деления всего устройства в Промежутке времени . i t ie предварнтельный делитель 1 имеет коэффициент деления К+1. Таким образом, введение новых элементов и связей в делителе частоты с переменным коэффициентом деления позволяет уменьшить дискретность изменения коэффициента деления до значений, меньших единицы.

j г 10

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с программируемым коэффициентом деления | 1987 |

|

SU1649659A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU894877A2 |

| Устройство для вычисления отношения временных интервалов | 1981 |

|

SU966705A2 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ С РЕГУЛЙРУЮвиМ КОЭФФЩИЕНТСМ ДЕЛЕНИЯ, сЬдеряавдий п д арительный делитель выход которого соединен с входами синхронизации первого и вто рого В -триггеров, с счетными входа |мн лрбГранФШруеА&дх счетчиков импуль сов младших и старших разрядов, выход которого череэ блок опознавание соединен с D пвходом второго D -трнг гера, прямой выход которого подключен к входам начальной установки программируек&ис счетчиков нмпульбов старших и Г4ладших разрядов, выход которого соединен с О -входом первого Р -триггера, инверсиый выход которого подключен к управлякцему входу предварительного делителя частоты, отлич ающийся тем, что, с целью расширения диапазона изменения коэффицнеита деления за счет возможности получ1ения дробных коэффициентов, в иего введен блок nporpai««d, включенный между инверсным выходом второго D -триггера и R-входом первого D -триггера.

Авторы

Даты

1983-10-30—Публикация

1982-06-24—Подача