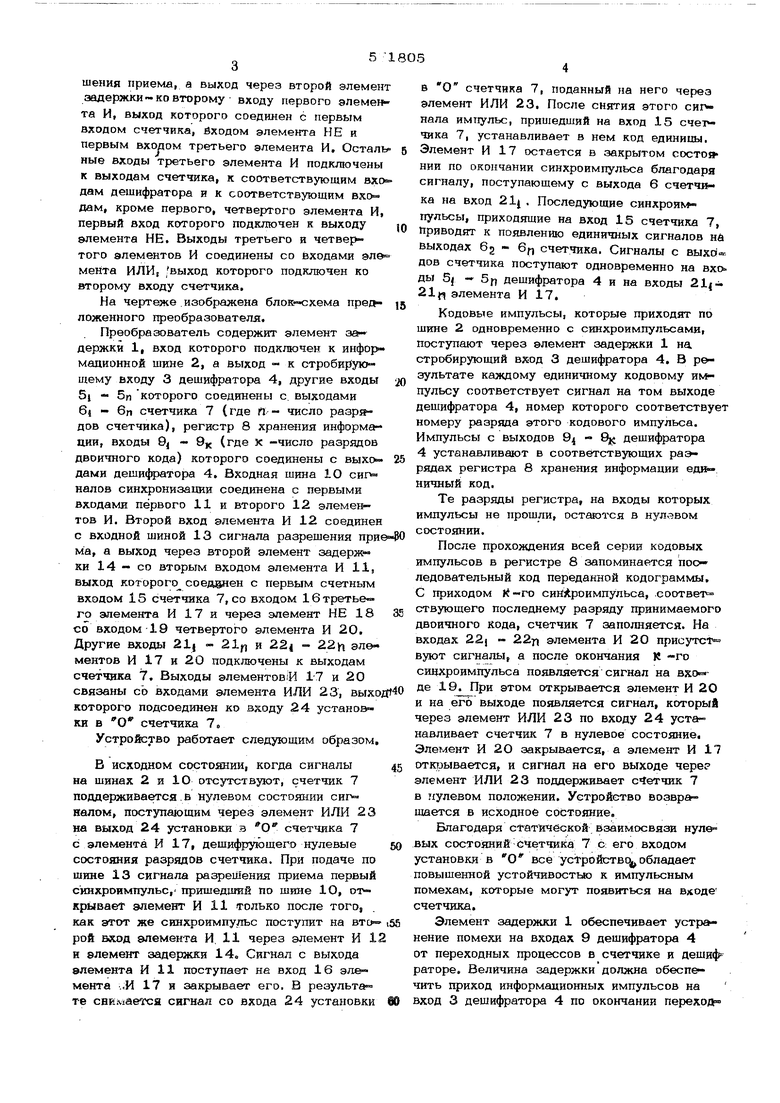

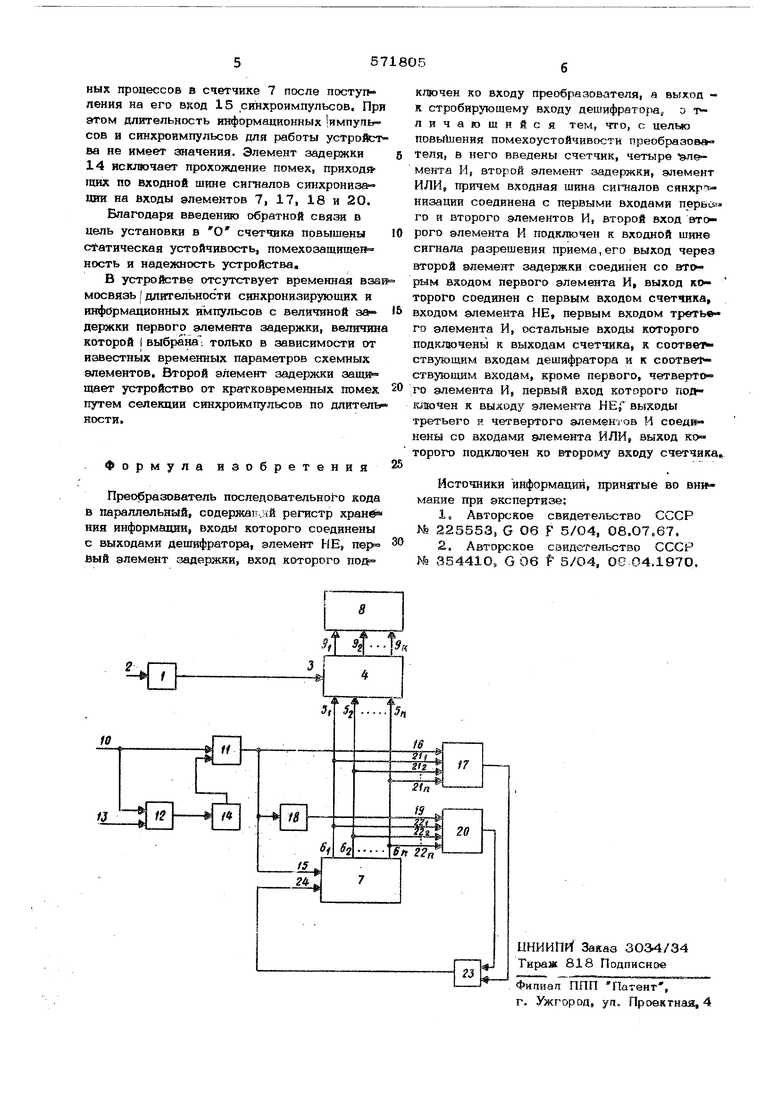

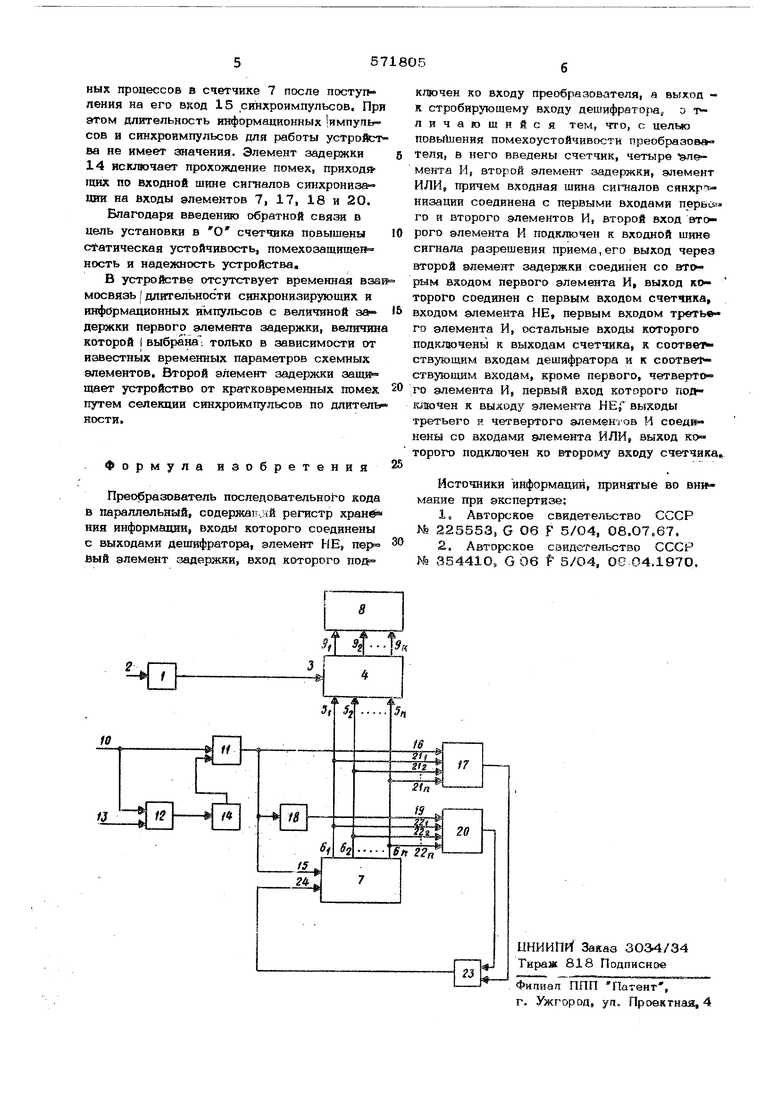

шеиия приема, а выход через второй элемен задержки-ко второму входу первого элеме№ та И, выход которого соединен с первым входом счетчика, Входом элемента НЕ и первым входом третьего элемента И. Осталь ные входы третьего элемента И подключены к выходам счетчика, к соответствующим вхо дам дешифратора и к соответствующим входам, кроме первого, четвертого элемента И, первый вход которого подключен к выходу элемента НЕ. Выходы третьего и четвертого элементов И соединены со входами эле мента ИЛИ, /выход которого подключен ко второму входу счетчика. На чертеже. изображена блок-схема предложенного преобразователя. Преобразователь содержигт элемент з&держки 1, вход которого подключен к инфор)мадионной шине 2, а выход - к строби{ ую щему входу 3 дешифратора 4, другие входы 5i - 5п которого соединены с, выходами 6| - 6п счетчика 7 (где Л - число разрядов счетчика), регистр 8 хранения информации, входы 9| - 9к (где к -число разрядов двоичного кода) которого соединены с выходами дешифратора 4, Входная шина 1О СИР налов синхронизации соединена с первыми входами первого 11 и второго 12 элементов И. Второй вход элемента И 12 соединен с входной шиной 13 сигнала разрешения при ма, а выход через второй элемент задерж ки 14 - со вторым входом элемента И 11, выход которого соеддаен с первым счетным входом 15 счетчика 7, со входом 16 третьего элемента И 17 и через элемент НЕ 18 со входом 19 четвертого элемента И 20. Другие входь 21j - 21 и 224 22 элементов И 17 и 20 подключены к выходам счетчика 7. Выходы элементовiM 17 и 20 связаны со входами элемента ИЛИ 23, выхо которого подсоединен ко входу 24 установки в О счетчика 7 Устройство работает следующим образом, В исходном состоянии, когда сигналы на шинах 2 и 1О отсутствуют, счетчик 7 поддерживается. в нулевом состоянии сипНалом, поступающим через элемент ИЛИ 23 на выход 24 установки з О счетчика 7 с элемента И 17, дешифрующего нулевые состояния разрядов счетчика. При подаче по шине 13 сигнала разрешения приема первый синхроимпульс,-пришедцгай по шине 10, открывает элемент И 11 только псюле того, как этот же синхроимпульс поступит на вто рой вог.од элемента И, 11 через элемент И 12 и элемент задержки 14, Сигнал с выхода элемента И 11 поступает не вход 16 элемента ..И 17 н закрывает его. В результа те снимается сигнал со входа 24 установки в О счетчика 7, поданный на него через элемент ИЛИ 23. После снятия этого сиг нала импульс, пришедший на вход 15 счетчика 7, устанавливает в нем код единицы. Элемент И 17 остается в закрытом состо НИИ по окончании синхроимпульса благодаря сигналу, поступающему с выхода 6 счетчика на вход 21j . Последующие синхронк пульсы, приходящие на вход 15 счетчика 7, Приводят к появлению единичных сигналов на выходах 6э - 6п счетчика. Сигналы с выходов счетчика поступают одновременно на вхо ды 5j - 5п дешифратора 4 и на входы 21|21 f, элемента И 17. Кодовые импульсы, которые приходят по шине 2 одновременно с синхроимпульсами, поступают через элемент задержки 1 на. стробируюший вход 3 дешифратора 4. В р&зультате каждому единичному кодовому ик пульсу соответствует сигнал на том выходе дешифратора 4, номер которого соответствует номеру разряда этого кодового импульса. Импульсы с выходов 9 - 9j4 дешифратора 4 устанавливают в соответствующих разрядах регистра 8 хранения информации единичный код. Те разряды регистра, на входы которых импульсы не прошли, остаются в нулевом состоянии. После прохождения всей серии кодовых импульсов в регистре 8 запоминается поо ледовательный код переданной кодограммы, С приходом k-ro си1й роимпульса, .соотве-п ствуюшего последнему разряду принимаемого двоичного кода, счетчик 7 заполняется. На входах 22) -22 элемента И 20 присутст вуют сигналы, а после окончания К -го синхроимпульса появляется сигнал на 19. При этом открывается элемент И 20 и на ёго выходе появляется сигнал, который через элемент ИЛИ 23 по входу 24 устанавливает счетчик 7 в нулевое состояние. Элемент И 2О закрывается, а элемент И 17 открывается, и сигнал на его выходе чере элемент ИЛИ 23 поддерживает с1етчик 7 в пулевом положении. Устройство возвращается в исходное состояние. Благодаря статической. взаимосвязи нулевых состояний счетчика 7 с; его входом установки в О все усГрОйствс обладает повышенной устойчивостью к импульсным помехам, которые могут появиться на входесчетчика. Элемент задержки 1 обеспечивает устранение помехи на входах 9 дешифратора 4 от переходных процессов в счетчике и дешиф раторе. Величина задержки должна обеспечить приход информационных импульсов на вход 3 дешифратора 4 по окончании переход ных процессов в счетчике 7 после поступления на его вход 15 синхроимпульсов. При этом длительность информационных импульсов и синхроимпульсов для работы устройства не имеет значения. Элемент задержки 14 исключает прохождение помех, приход тих по входной шине сигналов синхронизм дни на входы элементов 7, 17, 18 и 20. Благодаря введению обратной связи в цель установки в О счетчика повышены статическая устойчивость, помехозащище ность и надежность устройства, В устройстве отсутствует временная вза мосвязь I длительности синхронизирующих и информационных импульсов с величиной з держки первого элемента задержки, величина которой I выбрана только в зависимости от известных временных параметров схемных элементов. Второй элемент задержки заши щает устройство от кратковременных помех путем селекции синхроимпульсов по длитель ности. Формула изобретения Преобразователь последовательного кода в параллельный, содержа1г.йй регистр храни ния информации, входы которого соединены с выходами дешифратора, элемент НЕ, пер вый элемент задержки, вход которого под ключей ко входу преобразователя, а выход к стробирующему входу дешифратора, э тпичаюшййся тем, что, с целью повышения помехоустойчивости преобразовав теля, в него введены счетчик, четыре элемента И, второй элемент задержки, элемент ИЛИ, причем входная шина сигналов сянхр низации соединена с первыми входами перьсгг. го и второго элементов И, второй вход второго элемента И подключен к входной шине сигнала разрешения приема, его выход через второй элемент задержки соединен со вторым входом первого элемента И, выход которого соединен с первым входом счетчика, входом элемента НЕ, первым входом третьего элемента И, остальные входы которого подключень к выходам счетчика, к соответствующим входам дешифратора и к соответствующим входам, кроме первого, четвертого элемента И, первый вход которого подключен к выходу элемента HEf выходы третьего и четвертого элемешов И соединены со входами элемента ИЛИ, выход ко торого подключен ко второму входу счетчика Источники информадии, принятые во внимание при экспертиза: 1о Авторское свидетельство СССР № 225553,, G 06 F 5/04, 08.О7о67. 2. Авторское свидетельство СССР № 354410, G06 f 5/О4, ое 04.197О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1980 |

|

SU920729A1 |

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для контроля воспроизведения цифровой информации с магнитного носителя | 1982 |

|

SU1027776A1 |

| Устройство для регистрации информации | 1979 |

|

SU824242A1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1297232A1 |

| Устройство для записи цифровой информации | 1986 |

|

SU1316037A1 |

| Устройство для программногоупРАВлЕНия | 1979 |

|

SU830310A1 |

| Устройство для сопряжения электронной вычислительной машины с абонентом | 1983 |

|

SU1137474A1 |

Авторы

Даты

1977-09-05—Публикация

1975-06-20—Подача