1

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и может быть использовано для преобразования последовательного кода в парал лельный.

Целью изобретения является повышение помехоустойчивости за счет устранения помех типа ложный импульс и дробление импульса.

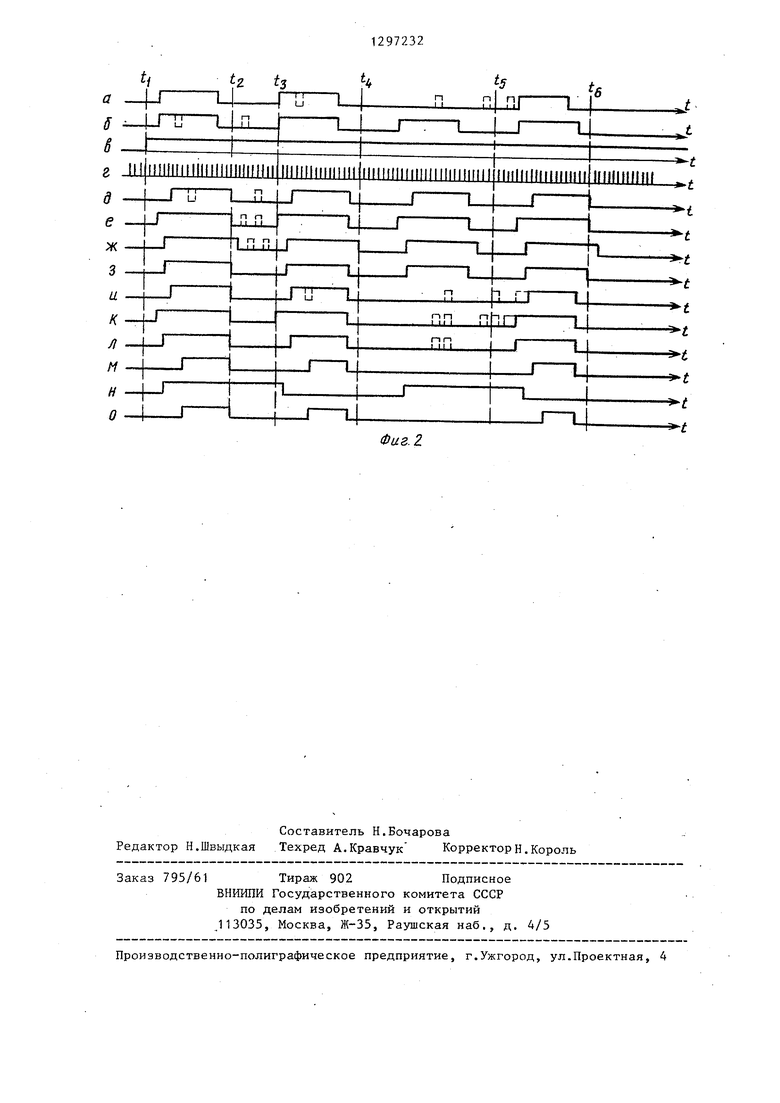

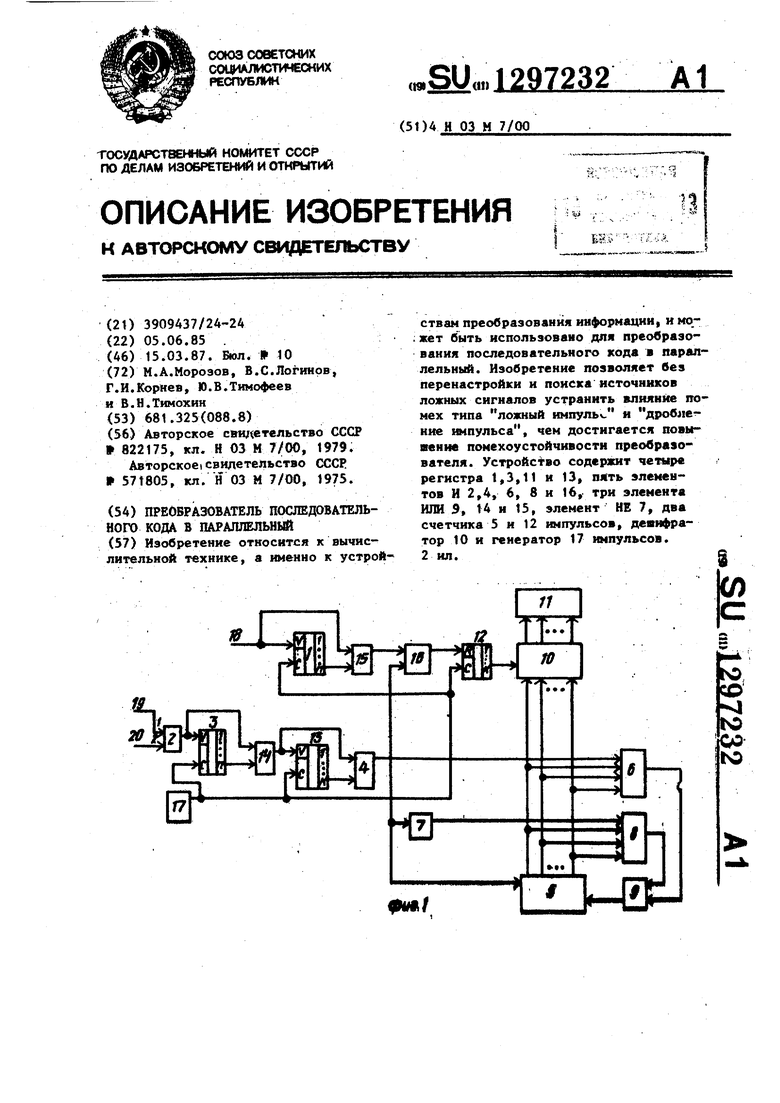

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы,, поясняющие его работу.

Устройство содержит первый регистр 1, первый элемент И 2, второй регистр 3, второй элемент И 4, первый счетчик 5 импульсов, третий элемент И 6, элемент НЕ 7,. четвертый элемент И 8, первый элемент ИЛИ 9, дешифратор 10, третий регистр 11, второй счетчик 12 импульсов, четвер- ть1й регистр 13, второй и третий элементы ИЛИ 14 и 15, пятый элемент И 16 и генератор 17 импульсов.

На фиг. 1 позициями 18, 19 и 20 обозначены соответственно информационный вход, вход синхронизации и управляющий вход устройства.

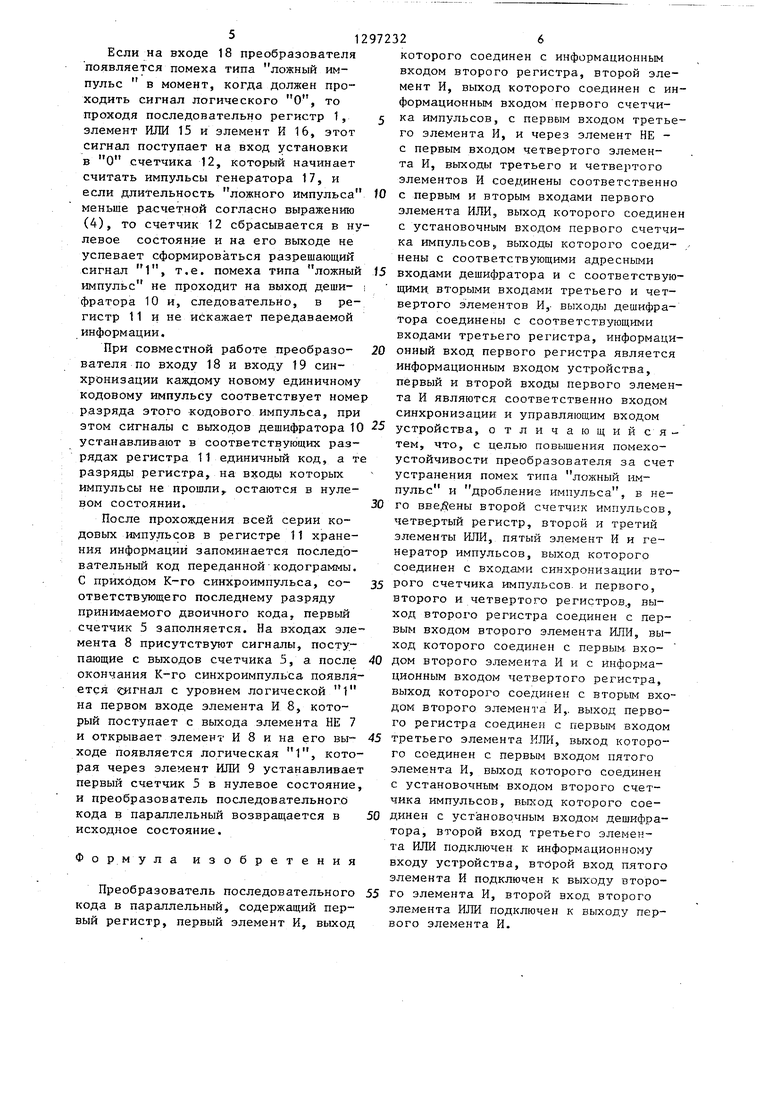

На фиг, 2 обозначено:

а - сигнал на входе 18;

б - сигнал на входе 19;

в - сигнал на входе 20;

г - сигнал на выходе генератора 1

д - сигнал на выходе регистра 3;

е - сигнал на выходе элемента ИЛИ 14;

ж - сигнал на выходе регистра 13;

3 - сигнал на выходе элемента И 4;

ж - сигнал на выходе регистра 1;

к - сигнал на выходе элемента ИЛИ 15;

л сигнал на выходе элементам 16

м сигнал на выходе счетчика 12;

н - сигнал на выходе счетчика 5;

о - сигнал на выходе дешифратора 10.

Устройство работает следующим образом.

При вк,гаочении устройства происходит установка в О первого 5 и второго 12 счетчиков, а генератор 17 импульсов начинает выдавать непрерывную последовательность прямоугольных импульсов, период следования которых выбирается исходя из максимально допустимой длительности импульса помехи . .. ,

O

5

0

5

0

5

Т ч мп макс помех .(О ген. 2

Если на входе сит)хронизации 19 присутствует уровень логического О, то первый счетчик 5 поддерживается в нулевом состоянии сигналом с уровнем логической 1, по- ступающим чераз элемент ИЛИ 9 на- вход первого счетчика 5 с третьего элемента И 6, выделяющего нулевые состояния счетчика 5, второй счетчик 12 поддерживается в нулевом состоянии сигналом с уровнем логического О, поступающего с выхода элемента И 16, который формируется от сигнала логического О, поступающего с выхода элемента И 4, являющегося реакцией этого элемента на нулевой сигнал, поступающий с входа 19 синхронизации. При подаче на вход 20 сигнала разрешения приема первый синхроимпульс, пришедший на вход 19 с уровнем логической единицы 1, пройдя через элемент И 2,. одновременно поступает на информационный вход регистра 3 и первый вход второго элемента ИЛИ 14, на втором входе которого этот же синхроимпульс появляется с задержкой, обусловленной прохождением его через регистр 3 под действием импульсов генератора 17 на синхро- входе, длительность задержки выбирается из условия

2t

ИМИ- помех.макс

- , синхронизации,

(2) определяется

априорно известного, и из выражения

-гаЭ ген.имп.

где п - номер выхода регистра (, 2,3...).

Под действием входных-сигналов на выходе элемента ИЛИ 14 формируется сигНсШ логической t, поступающий одновременно на информационный вход регистра 13 и на вход элемента И 4, на выходе которого сигнал логической 1 появляется только после того, как на его втором входе появится сигнал логической поступающий с выхода регистра 13 задержки прохождеия сигнала, который выбирается из словия

Ч«3

кмп .скк)фоиизачи «i

(3)

и вычисляется как f,t Т,.и.п«д,„б, хК (где ,2,3,4,.,.).

Если во время действия логической 1 по входу 19 синхронизации, появляется помеха типа дробление импульса длительностью С„„г,.мак..по««.

-(, 3, то пройдя вход элемента ИЛИ 14, на втором входе которого присутствует незадержанный сигнал, помеха, сформированная в другой момент времени, перекрывается уровнем логической 1 задержанного сигнала и на выход элемента ИЛИ 14 помеха типа дробление импульса не проходит, но эти элементы не защищают сдвиговый регистр 3, второй элемент ИЛИ 14 от помехи типа ложный импульс ,

Для защиты от помехи ложный импульс служит каскад из регистра 13 и элемента И 4, на входах которого присутствуют одновременно сигнал с выхода элемента ИЛИ 14 и задержанный на регистре 13 тот же сигнал, таким образом запрещается прохождение ложного импульса через первый цемент И 4 и на выходе формируется отфильтрованный сигнал с уровнем логической 1.

Выбор длительности задержек в регистрах 13,3 и включения их, как указано, позволяет устранить кратковременные импуль сные помехи типа дробление импульса и ложный импульс длительностью t по входу 19

имп.помеди

синхронизации. Отфильтрованный .от помех сигнал с выхода элемента И 4 с уровнем логической 1 поступает на первый вход третьего элемента И 6, под действием которого на его выходе формируется сигнал с уровнем логического О и, пройдя через первый элемент ИЛИ 9,, поступает на вход счетчика 5, разрешая просчитать импульс синхронизации, пришедший на информационный вход счетчика 5, который устанавливает на первом выходе счетчика 5 уровень логической 1,

Третий элемент И 6 остается в нулевом состоянии по окончании синхроимпульса благодаря сигналу, поступающему с первого выхода счетчика 5 на соответствующий вход элемента И 6. Последующие синхроимпульсы, приходящие на вход счетчика 5, приводят к появлению единичных сигналов на следующих выходах счетчика 5. Сигналы с выхода счетчика 5 поступают одновременно на соответствующие входы дешифратора 10, элементов И 6 и 8. Прохождение сигналов по входу 18 преобразователя осуществляется следующим образом.

Кодовые импульсы, которые приходят на вход 18 одновременно с синхроимпульсами, поступают на информационный вход регистра 1 и на вход элемента ИЛИ 15, на другом входе которого этот же кодовый импульс появляется

5

с задержкой tJ,. .„ п.

обусловленной прохождением его через регистр 1, в результате чего на выходе элемента ИЛИ 15 формируется сигнал логической 1,, который далее поступает на вход элемента И 16, на другом входе которого в это время - присутствует разрешающий сигнал логической 1, поступающий с выхода элемента И 4. На выходе элемента И 16

5 формируется разрешающий сигнал с уровнем логической 1, который, поступая на вход установки счетчика 12, разрешает счет импульсов генератора 17, поступающих на вход синхрониQ зации счетчика 12. На выходе счетчика 12 появляется сигнал логической 1, задержка которого относительно импульса разрешения счета выбирается исходя из максимальной длительности импульсной помехи типа ложный импульс и импульса синхронизации из условия

t t i t

имп.помехи исхкс ja3 имп сцкирочи50.1x44

(4)

0 и определяется исходя из следующего

соотношения:

. ген. импульсов J

где К - разряд счетчика.

Сигнал с выхода счетчика 12 посту пает на вход дешифратора 10, который разрешает формирование сигнала логической 1 на том выходе дешифрато-- ра Ю, которому соответствует кодовая комбинация на его адресных

входах. С выхода дешифратора 10 импульс логической 1, воздействуя на соответствующий вход pei-истра, устанавливает в соответствующем разряде этого регистра уровень логичес- кой 1. Если на входе 18 присутствует помеха типа дробление импульса, то она не проходит далее элемента ИЛИ 15.

Если на входе 18 преобразователя появляется помеха типа ложный импульс в момент, когда должен проходить сигнал логического О, то проходя последовательно регистр 1, элемент ИЛИ 15 и элемент И 16, этот сигнал поступает на вход установки в О счетчика 12, который начинает считать импульсы генератора 17, и если длительность ложного импульса меньше расчетной согласно выражению (4), то счетчик 12 сбрасывается в нулевое состояние и на его выходе не успевает сформироваться разрешающий сигнал 1, т.е. помеха типа ложный импульс не проходит на выход деши- фратора 10 и, следовательно, в регистр 11 и не искажает передаваемой информации.

При совместной работе преобразо- вателя по входу 18 и входу 19 синхронизации каждому новому единичному кодовому импульсу соответствует номер разряда этого кодового импульса, при этом сигналы с выходов дешифратора 10 устанавливают в соответствующих разрядах регистра 11 единичный код, а те разряды регистра, на входы которых импульсы не прошли,, остаются в нулевом состоянии.

После прохождения всей серии кодовых импульсов в регистре 11 хранения информации запоминается последовательный код переданной кодограммы. С приходом К-го синхроимпульса, со- ответствующего последнему разряду принимаемого двоичного кода, первый счетчик 5 заполняется. На входах элемента 8 присутствуют сигналы, поступающие с выходов счетчика 5, а после окончания К-го синхроимпульса появляется О 1гнал с уровнем логической 1 на первом входе элемента И 8, который поступает с выхода элемента НЕ 7 и открывает элемент И 8 и на его вы- ходе появляется логическая 1, которая через элемент ИЛИ 9 устанавливает первый счетчик 5 в нулевое состояние, и преобразователь последовательногс) кода в параллельный возвращается в исходное состояние.

Формула изобретения

Преобразователь последовательного кода в параллельный, содержащий первый регистр, первый элемент И, выход

которого соединен с информационным входом второго регистра, второй элемент И, выход которого соединен с информационным входом первого счетчика импульсов, с пернБ1м входом третьего элемента И, и через элемент НЕ - с первым входом четвертого элемента И, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ,, выход которого соедине с установочным входом первого счетчика импульсов,, выходы которого соеди- нены с соответствующими адресными входами дешифратора и с соответствующими, вторыми входами третьего и четвертого элементов И,- выходы дешифратора соединены с соответствующими входами третьего регистра, информационный вход первого регистра является информационным входом устройства, первый и второй входы первого элемента И являются соответственно входом синхронизации и управляющим входом устройства, о тл и ч ающий ся- тем, что, с целью повышения помехоустойчивости преобразователя за счет устранения помех типа ложньй импульс и дробление импульса, в него вве; 1;ены второй счетчик импульсов, четвертый регистр, второй и третий элементы ИЛИ, пятый элемент И и генератор импульсов, выход которого соединен с входами синхронизации второго счетчика импульсов, и первого, второго и четвертого регистров., выход второго регистра соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым, входом второго элемента И и с Информационным ВХОДО1- четвертого регистра, выход которого соединен с вторым входом второго элемента И,, выход первого регистра соединен с первым входом третьего элемента ИЖ, выход которого соединен с первым входом пятого элемента И, выход которого соединен с установочным входом второго счетчика импульсов, выход которого соединен с установочным входохм дешифратора, второй вход третьего элемента ШШ подключен к информационному входу устройства, второй вход пятого элемента И подключен к выходу второго элемента И, второй вход второго элемента ИЛИ подключен к выходу первого элемента И.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для синхронизации сигналов | 1977 |

|

SU669347A1 |

| Преобразователь последовательного кода в параллельный | 1975 |

|

SU571805A1 |

| Устройство для контроля синхронизации | 1983 |

|

SU1200268A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Преобразователь параллельного кода в последовательный | 1980 |

|

SU898419A1 |

| ДЕШИФРАТОР КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 2021 |

|

RU2754348C1 |

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1517135A1 |

| Устройство для определения экстремумов | 1981 |

|

SU991412A1 |

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и мо- :жет быть использовано для преобразования последовательного хода в параллельный. Изобретение позволяет без перенастройки и поиска источников ложных сигналов устранить влияние помех типа ложный импуль«. и дробле ние шчпульса, чем достигается повышение помехоустойчивости преобразователя. Устройство содержит четыре регистра 1,3,11 и 13 пять злемен- тов И 2,4, 6, 8 и 16, три злемента ИЛИ Э, 14 и 15, злемент НЕ 7, два счетчика 5 и 12 импульсов, дешифратор 10 и генератор 17 импульсов. 2 ил. 9 fc

| Преобразователь последовательногоКОдА B пАРАллЕльНый | 1979 |

|

SU822175A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь последовательного кода в параллельный | 1975 |

|

SU571805A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-15—Публикация

1985-06-05—Подача