1

Изобретение относится к автоматик и может быть использовано в системах автоматического управления и контроля.

Известно программно-переменное командное устройство, содержащее генератор импульсов с делителем частоты, счетчик времени, элементы И и триггеры, у которых нулевой вход каждого предыдущего соединен соответственно с нулевым выходом каждого последующего, образуя цепочку 1.

Это устройство характеризуется отсутствием возможности выдавать команду любой длительности, сложностью смены программ из-за съема большого количества- механически закрепленных для обеспечения надежного контактирования блоков коммутации одной программы и установки с механическим закреплением такого же количества блоков коммутации программы, отсутствием возможности многократно выдавать команды по одному г1дресу при выполнении програмтлы. . Это программно-временное командное устройство не позволяет организовать проверку сложного объекта, когда необходимо многократно и независимо по каждому адресу вьадавать

команды различной длительности в большое количество адресов (например, несколько сотен).

Наиболее близким техническим решением к изобретению является устройство для программного управления, содержащее два генератора импульсов, счетчик импульсов, распределитель импульсов, блок задания программ,

блоки сравнения кодов времени, блоки сравнения адресов и блок командных триггеров. Это устройство позволяет выдавать многократно команды любой длительности по независимым адресам 2 .

Недостатком этого устройства является невозможность отработки неограниченного числа вариантов программ, того, что в блоке

знания программ с каждой ячейки снимается один программный код времени. На каждую команду требуется две ячейки (одна - для включения команды, другая - для ее выключения),

причем каждая ячейка используется только в свое время по программе. Кроме того, устройство характеризуется сложностью процесса смены программы. Если ячейки блока задания

программ некоммутируемые (типа ячеек

ЗУ), то для смены программы необхо.дима перепрошивка ЗУ, а если коммутируемые (типа коммутируемых диодных матриц), то при смене программы необходимо перекоммутировать (переставить) диоды каждой Многоразрядной, например, 24-х разрядной ячейки для программы длИ тельностью несколько часов с точностью выдачи команд 0,1 сек.

Цель изобретения - расширение функциональных возможностей за счет обеспечения отработки неограниченного числа вариантов программ.

Поставленная цель достигается тем, что в устройство для програмглного управления, содержащее последовательно соединенные генератор импульсов, делитель частоты, первый элемент И, счетчик текущего времени и блок сравнения, второй вход кото-, рого соединен с выходом первого триггера и вторым входом первого элемента И, а также вторые элементы И, выходы которых через первые дешифраторы соединены со входами вторых триггеров, введены последовательно соединенные блок считывания информации, формирователь импульсов, счетчик строк, второй дешифратор, первый элемент ИЛИ и третий элемент И, последовательно - соединенные третий триггер, второй элемент ИЛИ, четвертый элемент И, счетчик тактов, третий дешифратор, четвертый триггер и пятый элемент И и последовательно соединенные сумматор, шестой элемент И и третий элемент ИЛИ, а также элемент задержки, четвертый элемент ИЛИ, седьмой восьмой, девятый и десятый элементы И, пятый и шестой триггеры и регист сдвига, первыми входами соединенный со вторыми выходами блока считывания информации и первыми входами сумматора, второй вход которого подключен к выходу седьмого элемент И, первым входом соединенного с выходом третьего триггера, а вторым входом - со вторым входом третьего элемента И и вторым выходом третьег дешифратора, третий выход которого подключен к первым входам пятого триггера и восьмого элемента И, вторым входом соединенного со вторым выходом второго дешифратора, первым входом блока считывания информации и вторым входом шестого элемента И, третий вход которого подключен ко вторым входам четвертого и пятого триггеров, выход пятого триггера соединен через девятый элемент И со вторыми входами блока считывания информации и регистра сдвнга, а через последовательно соединенные элемент задержки и десятый элемент И - с третьим входом регистра сдвига, четвертым входом подключенного к выходу третьего элемента И, регис

сдвига первыми выходами соединен с третьими входами блока сравнения, вторыми выходами - с первым входом вторых элементов И, вторые входы которых соединены с выходом пятого элемента И, вторым входом подключенного ко второму входу девятого элемента И, выходу шестого триггера и второму входу второго элемента ИЛИ, второй вход десятого элемента И соединен с выходом четвертого элемента ИЛИ и вторым входом первого элемента ИЛИ, третий вход десятого элемента И - с выходом четвертого элемента И, выход блока сравнения - с первым входом шестого триггера, второй вход которого подключен к выходу счетчика тактов и первому входу третьего триггера, Вторым входом соединенного с выходом формирователя импульсов, второй вход четвертого элемента И - с выходом генератора импульсов, выход третьего элемента ИЛИ - с первым входом первого триггера, входы четвертого элемента ИЛИ с третьими выхода1йи второго дешифратора, а второй вход счетчика строк с выходом восьмого элемента И,

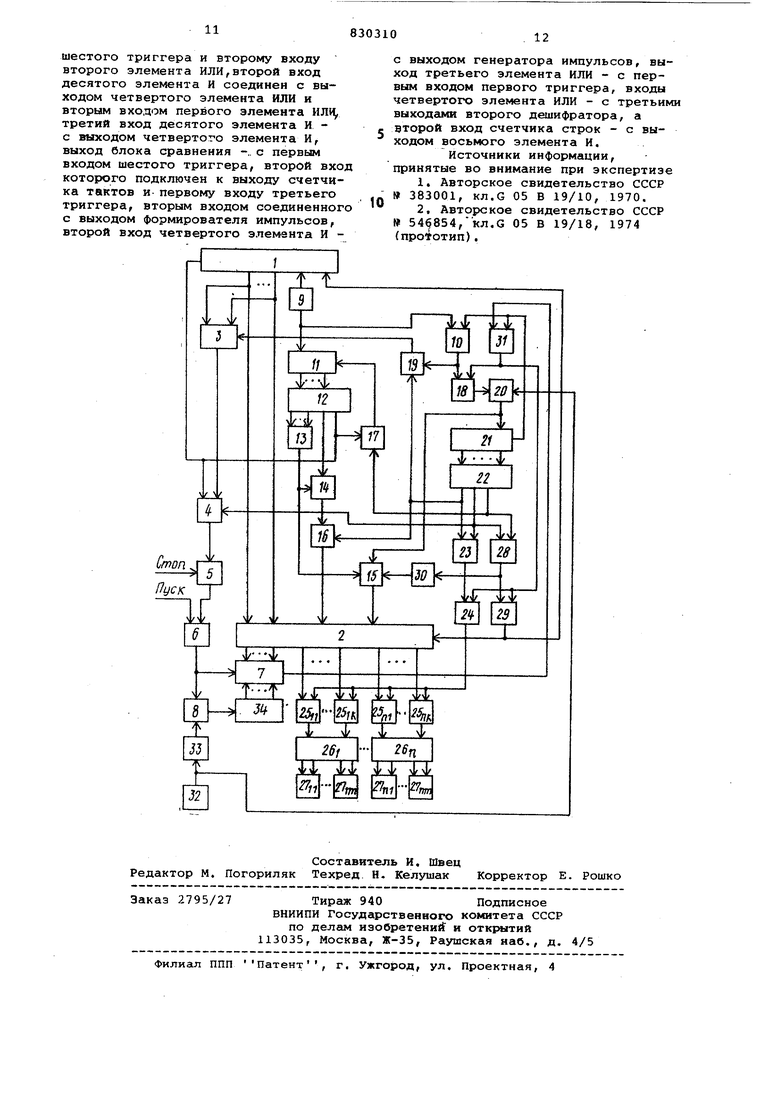

На чертеже представлена схема устройства.

Устройство для nporpaivMHoro управления содержит блок 1 считывания информации, соединенный с регистром 2 сдвига и через сумматор 3, шестой элемент И 4, третий элемент ИЛИ 5, первый управляющий триггер 6 с блоком 7 сравнения и первым элементом И 8, формирователь 9 импульсов, соединенный входом с блоком 1 считывания информации, а выходом - с третьим управляЕяяйм триггером 10 и счетчиком 11 cтpoк выходы которого соединены со входами второго дешифратора 12, третьи выхода которого соединены через четвертый элемент ИЛИ 13 с первьш элементом ИЛИ 14 и десятым элементом И 15, первый выход соединен через первый элемент ИЛИ 14 и третий элемент И 16 с регистром 2 сдвига, другой выход соединен с блоком 1 считывания информации, восьмым элементом И 17 и шестым элементом И 4, второй элемент ИЛИ 18, первый вход которого соединен с третьим управляюцщм триггером 10 и седьмым элементом И 19, а выход через четвертЕвй элемент И 20 соединен со счетчиком 21 тактов сдвига и десятым элементом И 15, третий деадифц атор 22, соединенный входами со счетчиком 21 тактов сдвига, а другим выходом соединен с четвертым элементом И 16, через седьмой элемент И 19 с cyMviaтором 3 и через четвертый управляющий триггер 23, пятый элемент И 24, вторые элементы И 25 и 25„, , первые дешифраторы 26( и 26f) адреса с вторыми триггерами 27 и 27, первым .выходом соединен с шестым элементом

.И 4, четвертым управляющим триггеро 23 и пятым управляющим триггером 28 выход которого соединен.с девятым элементом И 29 и через линию задержки 30 и десятый элемент И 15 с регистром 2 сдвига, одни выходы которго соединены с блоком 7 сравнения, а другие - со вторыми элементами И 25 и 25,, , шестой управляющий триггер 31, соединенный одним входо с блоком 7 сравнения, другим входом - с третьим управляющим триггером 10 и счетчиком 21 тактов сдвига генератор 32 импульсов, соединенный с четвертым элементом И 20 и через делитель 33 частоты, первый элемент И 8 со счетчиком 34 текущего времен (п - количество дешифраторов адреса определяемое числом одновременно включаемых команд; к - количество элементов И перед каждым дешифратором адреса, определяемое разрядностью кода адреса (к 2) ; m 2 Iвозможное количество командных триггеров на выходе каждого дешифратора адреса) Реальное число командных триггеров, дешифраторов адреса и элементов И перед ними определяется требуемым числом адресов, по которым выдаются команды.

Устройство для программного управления работает следующим образом

Перед началом работы в блок 1 считывания информации заправляется П|5ограммоноситель, например перфолента, на которой для каждой команды своим кадром, состоящим из нескольких, например 1, строк, размещена закодированная информация о времени выдачи команды, адресе вьвдачи ее и контрольная, После включения устройство приводится в исходное состояние, при котором блок 1 считывания информащии, регистр 2 сдвига, сумматор 3, счетчик

IIстрок, счетчик 21 тактов сдвига, счетчик 34 текущего времени и управляющие триггеры 6, 10, 23, 28, 31 обнулены. По сигналу ПУСК на второй вход управляющего триггера 6 с него выдается сигнал одновременно на разрешающий второй вход блока 7 сравнения и второй вход элемента И 8. Так как сравниваемые коды обнуленных регистра 2 сдвига и счетчика 34 текущего времени одинаковы, то в блоке 7 сравнения сразу же выраба.тывается импульс на первый вход управляющего триггера 31, выходной сигнал с которого поступает на вторые входы элемента И 24, элемента И 29 и через второй вход элемента ИЛИ 18 на первый вход элемента И 20, разрешая прохождение импульсов по его второму входу на счетчик 21 тактов сдвига с генератора 32 импульсов, с которого импульсы через делитель 33 частоты и первый вход элемента И 8 поступают также на

счетчик 34 текущего времени, начиная отсчет времени программы, Сигнгшы с первого и третьего выходов дешифратора 22, поступающие соответственно на второй и первый входы с управляющего триггера 28, формируют на его выходе сигнал, который через первый вход элемента И 29 поступает на запуск блока 1 считывания информации. Сигналы с первого, второго и третьего выходов дешифратора 22

to в запускающем цикле работы счетчика 21 тактов сдвига не проходят через запертые в исходном состоянии элементы И 4, 16, 17, 19. Сигнал с выхода управляющего триггера 23, сфор5 мированный из поступающих соответственно на его первый и второй входы сигналов со второго и первого выходов дешифратора 22, поступает через первый вход элемента И 24 на вторые

20 входы элементов И 25 и 25„ , разрешая съем кода с адресных вторых выходов регистра 2 сдвига, который находится пока в исходном состоянии. Сигнал переполнения с другого выхода

25 счетчика 21 тактов сдвига устанавливает по второму входу управляющий триггер 31 в нулевое состояние, заканчивая цикл запуска программы. Со вторых выходов запущенного блока 1 считывания информации построчно

d поступает кадр информации первой команды на первые входы сумматора 3 и регистра 2 сдвига, Паргшлельный код информации каждой строки кадра сопровождается синхроимпульсом, по5ступающим на формирователь 9 импульсов, в котором по переднему фронту синхроимпульса вырабатывается короткий импульс. По первому синхроимпульсу счетчик 11 строк устанавливается

0 ,в первое состояние и с третьего выхода дешифратора 12 через элемент ИЛИ 13 поступает сигнал на второй вход элемента И 15 и через второй вход элемента ИЛИ 14 на первый вход

j элемента И 16, По тому же первому

синхроимпульсу управляющий триггер 10 устанавливается в единичное состояние и выходной сигнал с него поступает на первый вход элемента И 19

л И через первый вход элемента ИЛИ 18 на первый вход элемента И 20, разрешая прохождение тактовых импульсов на счетчик 21 тактов сдвига. Сигнал со второго выхода дешифратора 22 через второй вход элемента И 19

поступает на второй вход сумматора 3 для приема и сложения в нем параллельного кода информации первой строки, а через второй вход элемента И 16 поступает на четвертый вход регистра

0 2 сдвига для приема, по его входам, на приемные разряды той же информации первой строки, Сигнал с выхода управляющего триггера 23, устанавливаемого в единичное состояние по тому же сигнсшу со второго выхода

дешифратора 22 не проходит через запертый элемент И 24, Сигнал с первого выхода второго дешифратора 22 обнуляет управляющий триггер 23 и устанавливает в единичное состояни управляющий триггер 28р сигнал с выхода которого через запертый элемент И 29 не проходит, а поступает через линию задержки 30 на первый вход элемента И 15, разрешая поступление тактовых-импульсов по третьему входу регистра 2 сдвига для сдвига информа ции из его приемных разрядов. Число импульсов сдвига определяется разрядностью принимаемого параллельного кода информации и одинаково для каждой строки. Сигнал с третьего выхода дешифратора 22 обнуляет управляющий триггер 28, прекращая поступление тактовых импульсов сдвига через третий вход элемента И 15 в регистр 2 сдвига, а через закрытый элемент И 17 не проходит. Сигнал переполнения с другого выхода счетчика 21 тактов сдвига обнуляет управляющий триггер 10 и поступление тактовых импульсов прекращается. На этом цикл операций в устройстве по приему информации первой строки кадра заканчивается. Этот цикл повторяется (1-2) раз, когда принимается информация (i-2) строк кадра в сумматор 3 и регистр 2 сДвига, с последующим сдвигом информации из приемных разрядов-в регистре 2 сдвига. Информация () строки кадра является последней для регистра 2 сдвига, поэтому сдвиг после ее приема осуществлять не надо, для чего по (i-1) синхроимпульсу сигнал на выходе элемента ИЛИ 13 отсутствует, а на первый вход элемента И 16 подается сигнал через первый вход элемента ИЛИ 14 с первого выхода дешифратора 12, Последняя (i-я) строка в кадре содержит только контрольную информацию, дополняющую до -обнуления код, выработанный в сумматоре 3 в результате сложения информации (1-1) строки, В связи с этим информация i-ой строки принимается только в сумматор 3, что и обусловливает отличия в работе устройства в i-oM цикле приема информ&ции от работы в первых (±-2) циклах. По 1-му синхроимпульсу со второго выхода дешифратора 12 поступает сигнал на вторые входы элементов И4и17ина первый вход блока 1 считывания информации для прекращения считывания информации.. Элементы И 15, 16, 24 и 29 по 1-ому синхроимпульсу остаются запертыми из-за отсутствия сигналов соответственно с выходов элемента ИЛИ 13, элемента ИЛИ 14 и обнуленного управляющего триггера 31, Сигнал со второго выхода дешифратора 22 поступае как и ранее в (i-l) циклах, через

второй вход открытого элемента И 19 на второй вход сумматора 3 для приема и сложения параллельного кода информации , В случае приема правильной информации (i-l) строк содержимое сумматора 3, после сложения правильной информации 1-ой строки, равно нулю и сигнал с его выхода отсутствует на первом входе элемент И 4. Тогда сигнал с первого выхода дешифратора 22 не проходит через третий вход элемента И 4 и первый вход элемента ИЛИ 5 на обнуление управляющего триггера 6. в случае приема неправильной информации хотя бы в одной из i строк содержимое сумматора 3 не равно нулю и сигнгш с его выхода поступает на первый вход элемента И 4, Тогда сигнал с первого выхода второго дешифратора 22 проходит через третий вход элемента И 4 и первый вход элемента ИЛИ 5 на обнуление управляющего триггера 6, с выхода которого снимается сигнал, разрешающий сравнени параллельных кодов в блоке 7 сравнения и прохождение импульсов через элемент И 8 на счетчик 34 текущего времени, остановку счета которого фиксирует оператор. Сигналом с третьего выхода дешифратора 22 через первый вход элемента И 17 обнуляется счетчик 11 строк. Сигналом переполнения счетчика.21 тактов сдвига, с его другого выхода, обнуляется управляющий триггер 10 и прекращается прохождение тактовых импульсов;через элемент И 20, На этом заканчивается прием с программоносителя кадра информации об одновременно выдавг емых командах, С первых выходов регистра 2 сдвига информация о времени выдачи команды по.ступает на вход блока 7 сравнения, а со вторых выходов регистра 2 сдвига информация об адресе выдачи команды поступает на первые входы элеме нтов И и .При наличии разрешающего сигнала с управляющего триггера 6, в момент рабегущего

венства кодов.

выходов счетчика 34 текущего времени и программного - с первых выходов регистра 2 сдвига, с выхода блока 7 сравнения поступает импульс на первый вход управляющего триггера 31, выходной сигнал с которого по вторым входам подготавливает элементы И 24 и 29, а через второй вход элемента ИЛИ 18 поступает на первый вход элемента И 20, разрешая прохождение тактовых импульсов на счетчик 21 тактов сдвига. Сигнал со второго выхода дешифратора 22 устанавливает в единичное состояние управляющий триггер 23, сигнал с выхода которого через первый вход элемента И 24 поступает на вторые входы элементов И 25 и 25, . по первым их входам прохождение информации со вторых выходов регистра 2 сдвига на дешифраторы 26 и адреса для включения или выключения сигналами с них соответствующих вторых триггеров 27 и 2 Так выдается первая группа одновременных команд, информация с которых заложена в первом кадре. Сигналом с первого выхода дешифратора 22 обн ляется управляющий триггер 23 и устанавливается в единичное состояние управляющий триггер 28, с выход которого сигнал поступает через элемент И 29 на второй вЗсод регистр 2 сдвига для обнуления и на второй вход блока 1 считывания информации для приема второго кадра информации о второй группе одновременно выдава мых команд. Сигнал с третьего выход дешифратора 22 обнуляет управляющий триггер 28. Сигнал переполнения с другого выхода счетчика 21 тактов сдвига обнуляет управлякнций триггер 31 и устройство готово к приему информации и синхроимпульсов второго кадра, приняв который устройство ожидает сравнения программного код времени с пер1вых выходов регистра 2 сдвига с бегущим . кодом со счетчика 34 текущего времени. Так после дЬвательно отрабатывается вся программа. Оператор по внешнему входу СТОП на второй вход элемента ИЛИ 5 может остановить программу. Использование устройства позволя значительно расширить функциональные возможности за счет обеспечения отработки устройством, без всяких переналадок, неограниченного числа вариантов nporpaj-iM. В известном устройстве блок задания программы состоит из ячеек, каждая из которых соответствует одной команде, а значит и весь набор ячеек блока задани программы соответствует одной програ ме, использовать подвижный программоноситель, изготовление и контроль которого осуществляется автоматическ на комплекте любой ЭВМ, а в известном контроль изготовления программы осуществляется визуально, легко корректировать программоноситель путем вклейки (вставки) дополнительного программоносителя с необходимым количеством информации, а в известно изменение программы ограничено конструкцией, удобно и быстро менять подвижный программоноситель, наприме смена перфоленты занимает 1 мин, а смена программы, например из 100 команд, в известном устройстве займет несколько часов из-за необходимости перекоммутации (перестановки), например 24-х разрядной, ячейки при продолжительности nporpaMivoj в несколько часов и с точностью выдачи команды 0,1 сек, а также обеспечить экономию за счет сокращения аппаратурных затрат. Формула изобретения Устройство для программного управления, содержащее последовательно соединенные генератор импульсов, делитель частоты, первый элемент И, счетчик текущего времени и блок сравнения, второй вход которого соединен с выходом первого триггера и вторым входом первого элемента И, а также вторые элементы И, выходы которых через первые дешифраторы соединены со входами вторых триггеров, отличаю щееся тем, что, с целью расширения функциональных возможностей устройства, в него последовательно соединенные блок считывания ин ормации, формирователь импул ьсов, счетчик строк, второй дешифратор, первый элемент ИЛИ и третий элемент И, последовательно соединенные третий триггер, второй элемент ИЛИ, четвертый элемент И, счетчик тактов, третий дешифратор, четвертый триггер и пятый элемент И и последовательно соединенные сумматор, шестой элемент И и третий элемент ИЛИ, а также элемент задержки, четвертый элемент ИЛИ, седьмой, восьмой, девятый и десятый элементы И, пятый и шестой триггеры и регистр сдвига, первыми входами соединенный со вторыми выходами блока считывания информации и первыми входами сумматора, второй вход которого подключен к выходу седьмого элемента И, первым входом соединенного с выходом третьего триггера, а вторым входом со вторым входом третьего элемента И и вторым высходом третьего дешифратора, третий выход которого подключен к первым входам пятого триггера и восьмого элемента И, вторым входом соединенного со вторым выходом второго дешифратора, пэрвым входом блока считывания информации и вторым входом шестого элемента и, третий вход которого подключен ко вторым входам четвертого и пятого,триггеров. выход пятого триггера соединен через девятый элемент И со вторыми входами блока считывания информации и регистра сдвига, а через последовательно соединенные элемент задержки и десятый элемзнт И - с третьим входом регистра сдвига, четвертым входом подключенного к выходу третьего элемента И, регистр сдвига первыми выходами соединен с третьими входами блока сравнение, вторыми выходами с первым входом вторых элементов И, торые входы которых соединены с выходом пятого элемента И, вторым ходом подключенного ко второму ходу девятого элемента И, выходу

шестого триггера и второму входу второго элемента ИЛИ,второй вход десятого элемента И соединен с выходом четвертого элемента ИЛИ и вторым входом первого элемента ИЛ( третий вход десятого элемента И с выходом четвертого элемента И, выход блока сравнения -.. с первым входом шестого триггера, второй вход которого подключен к выходу счетчика тактов и первому входу третьего триггера, вторым входом соединенного с выходом формирователя импульсов, второй вход четвертого элемента И с выходом генератора нмпульсов, выход третьего элемента ИЛИ - с первым входом первого триггера, входы четвертого элемента ИЛИ - с третьим выходс1ми второго дешифратора, а второй вход счетчика строк - с выходом восьмого элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 383001, кл.С 05 В 19/10, 1970.

2,Авторское свидетельство СССР 54§854,кл,С 05 В 19/18, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для лазерной обработки деталей | 1989 |

|

SU1682096A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

Авторы

Даты

1981-05-15—Публикация

1979-07-24—Подача