(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

тирующим входом второго операционного усилителя, выход которого соедннеи с выходом устройства, с подложкой третьего МОП-траизисюра, с истоком первого дополнительного МОП-транзистора и через последовательно соединенные третий, четвертый и пятый дшюлнительные МОП-транзисторы с инвертирующим входом второго операционного усилителя и через шестой дополнительный МСЯ1-транзистор с шиной нулевого потенциала. Подложка третьего дополнительного МОП-транзистора соединена с шиной запирающего напряжения, исток второго дополнительного МОП-транзистора - с шиной нулевого потенциала. Подложки четвертого, пятого и шестого дополнительных МОП-транзисторов подключены к стоку четвертого и истоку пятого дополнительных МОП-транзисторов и к одной из обкладок второго конденсатора, другая обкладка которого соединена с шиной нулевого потеидиала.

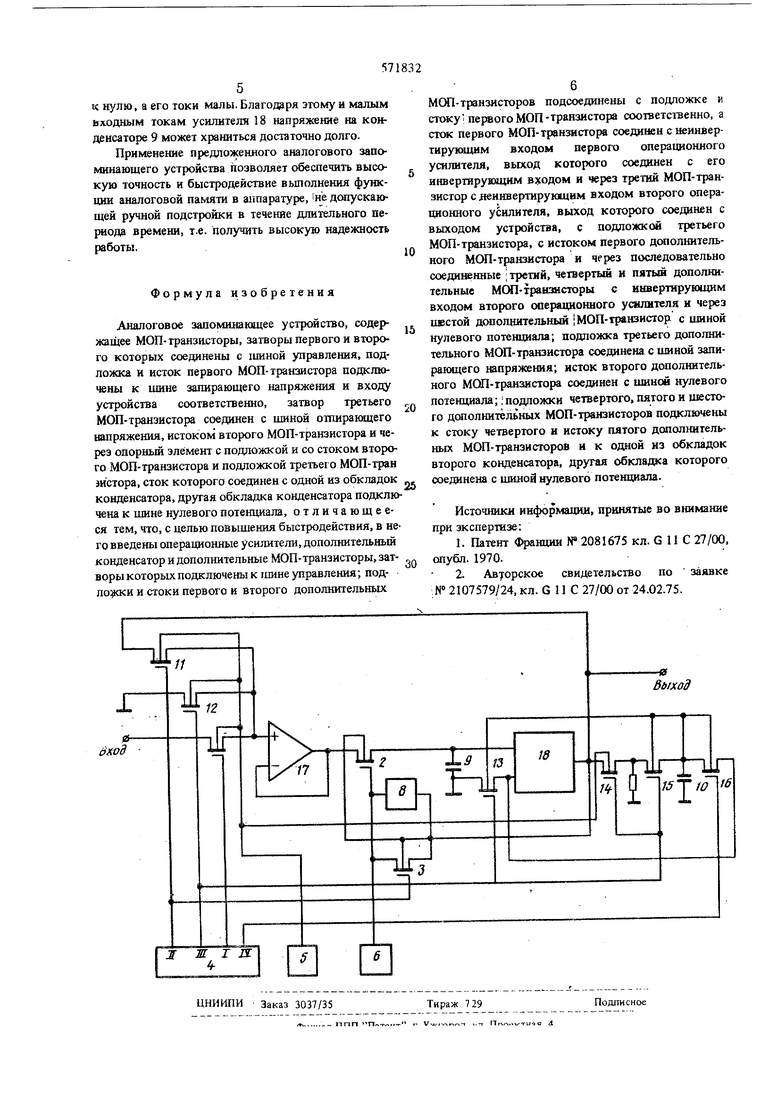

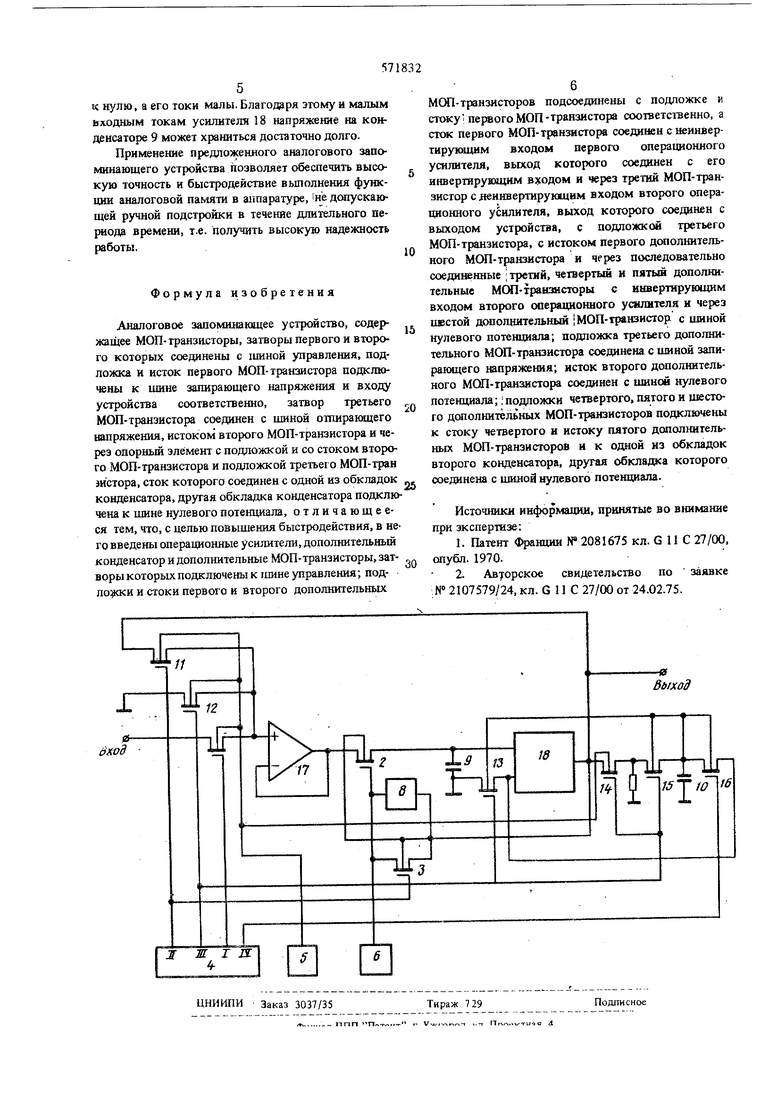

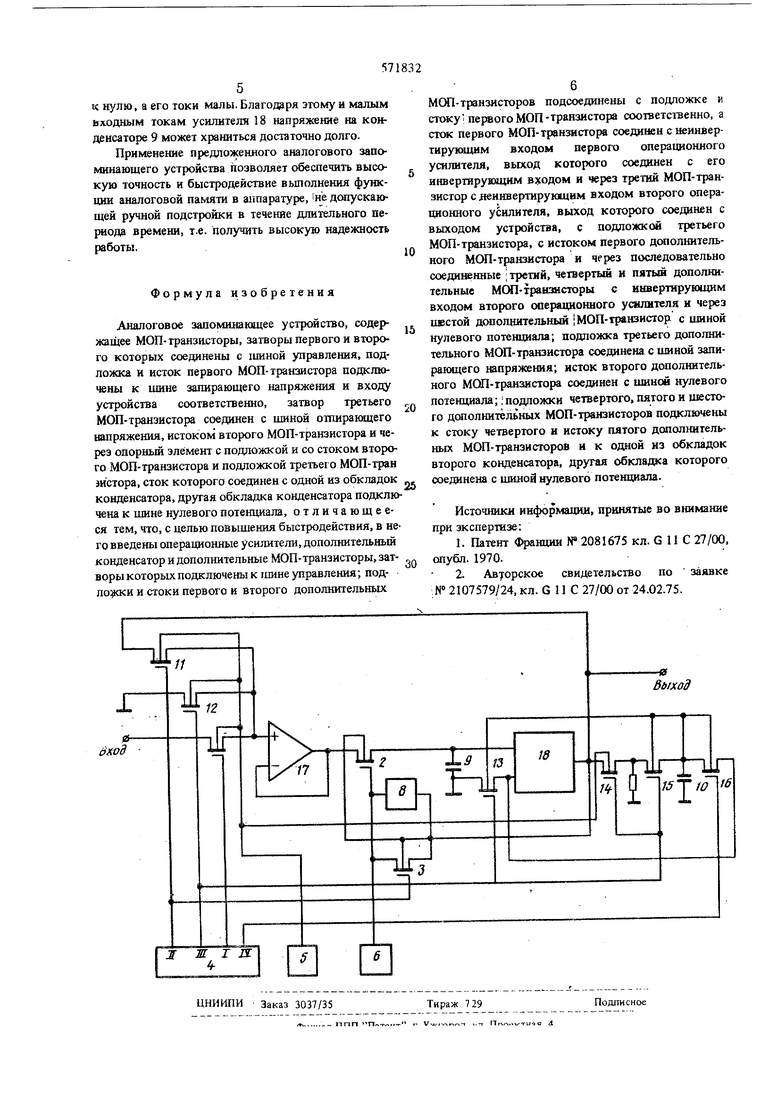

На чертеже представлена электрическая схема усфойства.

Оно содержит первьй 1, второй 2 и третий 3 МОП-транзисторы, шину управления 4, шину запиракндего напряжения 5, шину отпирающего напряжения 6, резистор 7, опорный злемент 8, первый и дополнительный конденсаторы 9 и 10, дополнительные первый 11, второй 12, третий 13, четвертьш 14, пятьш 15 и шестой 16 МОП-транзисторы и первый 17 и второй 18 операционные усилители.

Предложенное устройство работает следующим образом.

На Hi. BOM этапе в режиме автоматической подстройки устройства, которая проводится периодически (например, через каждые 64 цикла выборки и хранения входного сигнала) на отвод III шины 4 управления поступает отпирающее напряже1ше (для диапазона входных сигна; ов ±105 при использовании р-канальных МОП-транзисторов отпирающее напряжение выбрано равным примерно 20 и, а запирающее - +105). При этом МОП-транзисторы 11, 13, 14 и 15 открыты, а МОП-транзисторы 1, 3, 12 и 19 закрыты. Выходное напряжение усилителя 18 всегда равно разности напряжений на его входах, поэтому напряжение на затворе МОП-транзистора 2 равно напряжению на его выходе минус гшдение напряжения на опорном элементе 8.

Поскольку падение напряжения на опорном элементе 8 больше порогового напряжения МОП-транзистора 2, последний оказывается откры тым и конденсатор 9 заряжается до напряжения, . равного выходному напряжению усилителя 17, т.е. до потенциала земли. Конденсатор 10 также заря.жается до потенциала земли через открытые МОП-транзисторы 14 и 15.

На втором этапе в режиме автоматической подстройки напряжение на отводе II шины управления 4 становится отпирающим, поэтому отпирается МОП-транзистор 3, напряжение на опорном элемен, .,

При зтом из-за пролезания сигнала с затвора МОП-транзистора 2 через его внутренние емкости на конденсаторе 9 возникает и запоминается помеха, равная ошибке выборки. Величина этой помехи не зависит от уровня входного сигнала, но может медленно меняться со временем из-за старения элементов и изменения температуры и питающих напряжений. Конденсатор 10 также заряжается до напряжения, равного ошибке выборки через МОП-транзисторы 14 и 15. В конце второго этапа режима автоматической подстройки на отводах 1-111 шины управления 4 устанавливается запирающее напряжение, а на обводе IV отпирающее напряжение, поэтому напряжение, равное ошибке выборки, запоминается на конденсаторе 10 и через открьгтьй МОП-транзистор 16 попадает на первый вход усилителя 18. Теперь аналоговое запоминающее устройство готово к выборке и хранению входного сигнала. Емкость конденсатора 10 выбрана достаточно большой для того, чтобы ее разрядка не вносила заметной ошибки при выборке и хранении входного сигнала. Входное сопротивление усилителя 18 очень велико, а токи утечки транзисторов 13, 15 и 16 малы, так как напряжение между их подложками, входами и выходами не превосходит 0,2-0,35. Благодаря этому и больщой емкости конденсатора 10 напряжение ошибки выборки сохраняется на нем без заметных искажений в течение большого числа циклов выборки и хранения входного сигнала.

В режиме йь борки на отводы I и IV шины управления 4 поступают отпирающие напряжения, а на второй и третий - запирающие, no3TONfy МОП-транзисторы I и 16 открыты. Открыт также и МОП-транзистор 2, как это рассматривалось выше, а все остальные МОП-транзисторы закрыты. При этом конденсатор 9 быстро заряжается через открытый МОП-транзистор 2 до уровня входного сигнала. В этом режиме увеличение (уменьшение) напряжения на входе МОП - транзистора 1 приводат; к автоматическому увеличению (уменьшению) напряжения на затворе МОП-транзистора 2, так что разность между напряжениями с выхода МОП-транзистора 2 и его затвора остается постоянной независимо от уровня входного сигнала и примерно равной падению напряжения на опорном элементе 8.

При переходе к режиму хранения напряжение на отводе Г шины,управления 4 становится загшраюUWM, а на отводе 11 - отпирающим. Па отводе III сохраняется запирающее напряжение а на отводе IV отпирающее, поэтому отпираются МОП - транзисторы 3 и 12 и запираются МОП-транзисторы 1 и 2. При этом на конденсаторе 8 запоминается входной сигнал плюс напряжение, соответствующее ошибке выборки. Напряжение на выходе усилителя 18 равно разности напряжений на его входах, т.е. входному сигналу. На вход усилителя 17 через открытый МОП-транзистор 12 подается напряжение с выхода усилителя 18 и поэтому разность напряже

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1975 |

|

SU547836A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU545008A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU666584A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕКЛЮЧЕНИЯ ЗНАКОПЕРЕМЕННЫХ АНАЛОГОВЫХ СИГНАЛОВ | 1973 |

|

SU385287A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU890440A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858110A1 |

Авторы

Даты

1977-09-05—Публикация

1975-08-15—Подача