(54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ИНТЕГРАЛЬНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

I

Изобретение относится, к вычислительной технике, в частности к микроэлектронике, и может быть использовано в производстве интегральных МОП-схем. Известен усилитель считывания для динамических запоминающих устройств (ЗУ), состоящий из двух инверторов и двух ключешлх транзисторов, причем вход первого .инвертора подключен к истокам первого и второго ключевых транзисторов, сток первого ключевого транзистора подключен к выходу первого инвертора, объединенного с входом второго инвертора, а сток второго ключевого транзистора подключен к ылходу второго инвертора, а затворл ключевых транзисторов подклю -ены к шинам управляющих сигналов Cl .

Однако при таком построенииусилителя не обеспечивается компенсация помехи от включения транзистора выборки однотранзисторной ячейки памяти, что снижает эффективную чувствительность усилителя, потребляется значительная

мощность в статическом режиме и ограничивается быстродействие.

Наиболее близким к предлагаемому техническим рещением является усилитель считывания для интегрального ЗУ, содержащий два усилительных транзистора с общим истоком, соединенных тртггерной связью, стоки которых соединень соответственно с первой и второй сигнальными щинами, а общий исток соедиtoнен с первой щиной управления, два нагрузочных транзистора, истоки которых соединены с соответствующими сигнальными шинами, а стоки - с второй шиной управления 2 .

IS

Однако в интервале времени между опрокидыванием триггера и его отключением всегда существует цепь сквозного потребления через один из усилительных и один нагрузочный транзистор,

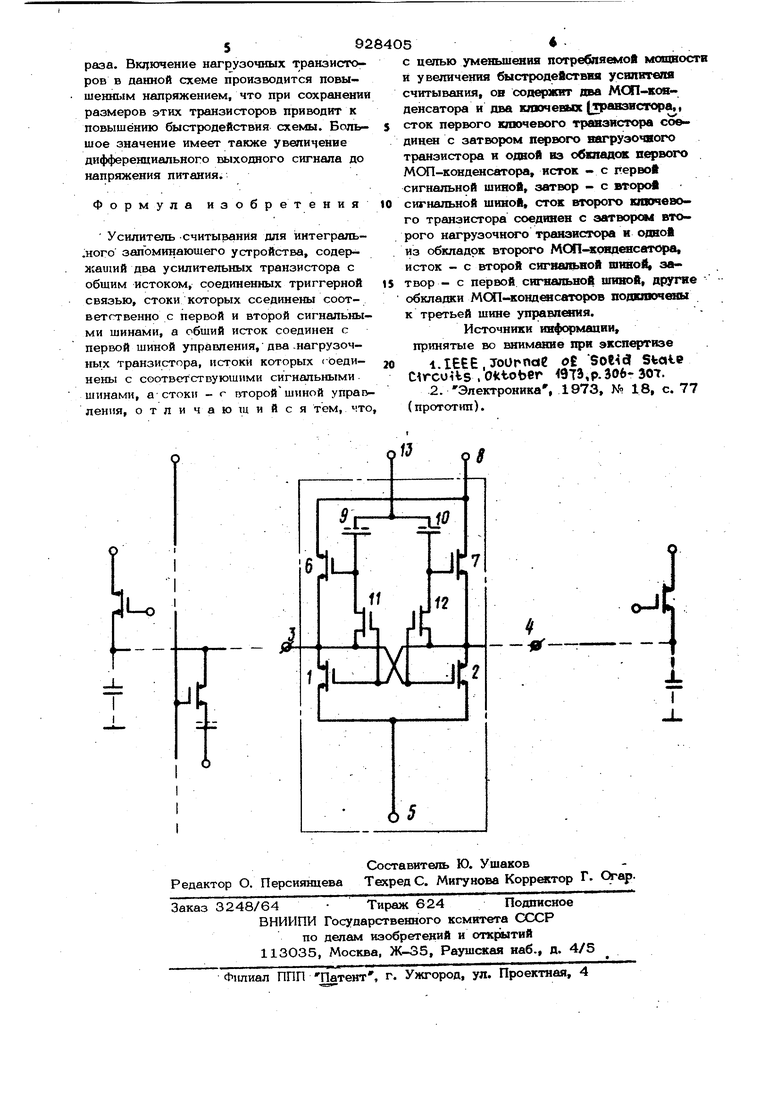

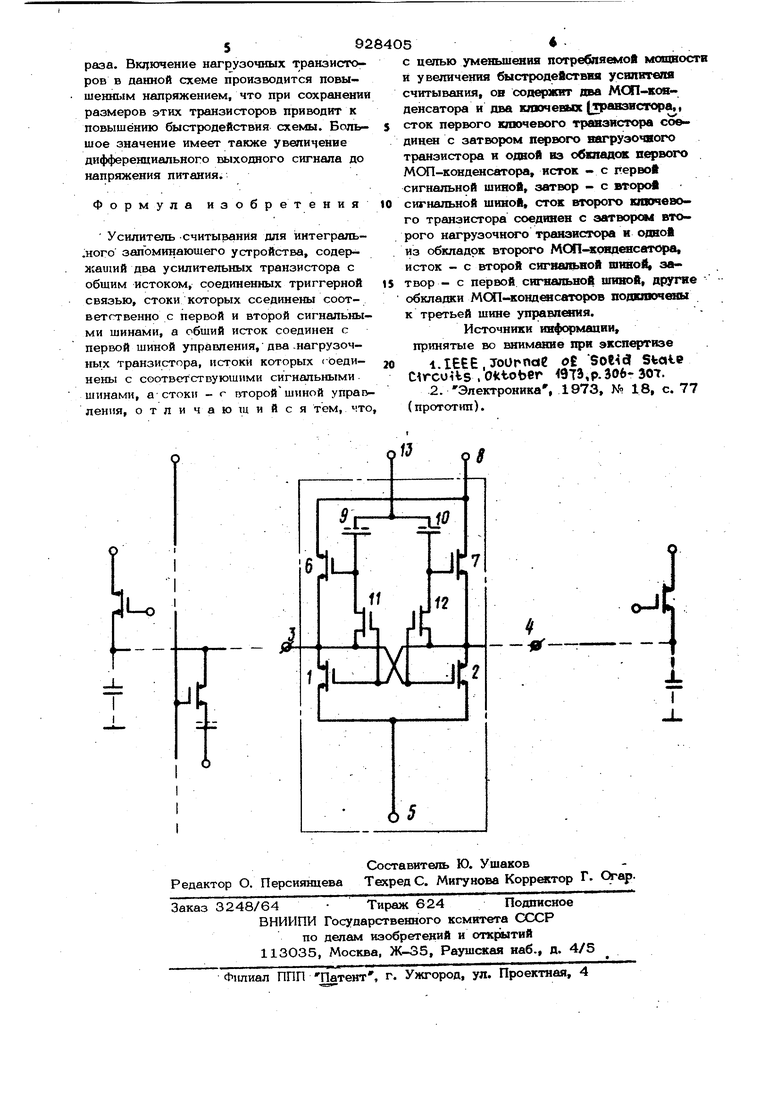

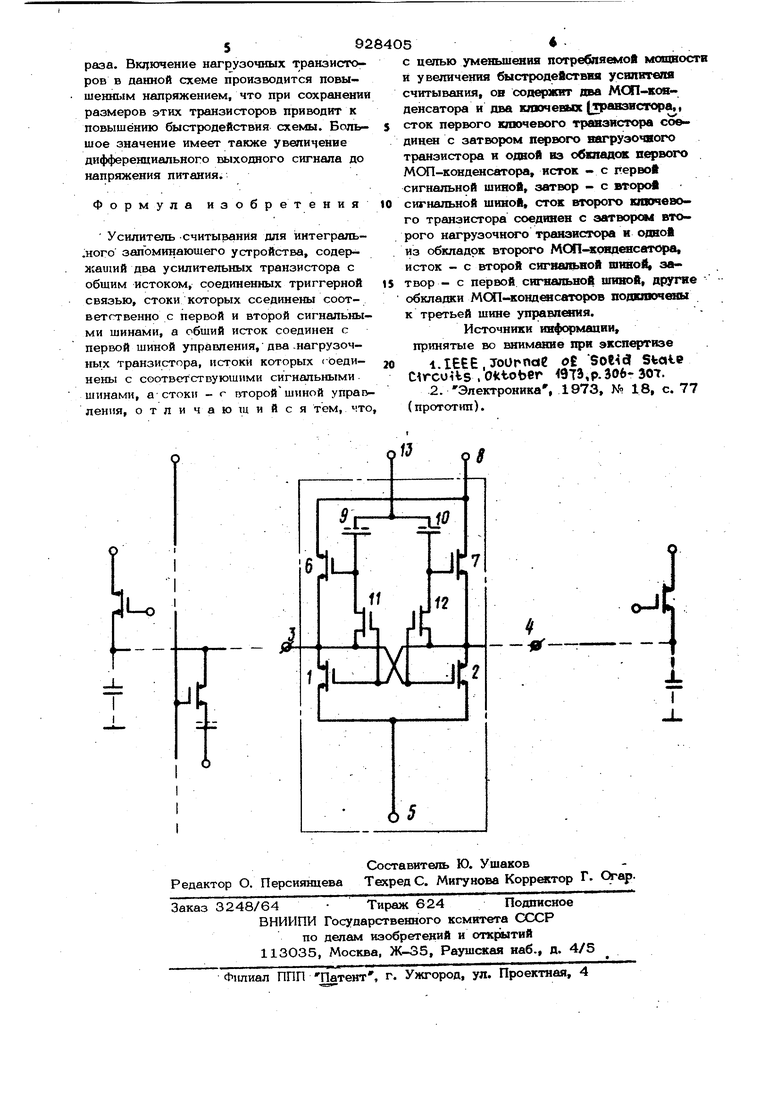

20 усилитель потребляет энергию от источника питания и после окончания процесса опрокидывания, что ведет к увеличению потребляемой мощности и снижает erf быстродействие за счет заряда паразитной емкости схемы. Шль изобретения - уменьшение потреб ляемой мощности и увеличение быстродействия усилителя считывания. Поставленная цепь достигается тем, что усилитель содержит два МСЯ1- сонден сатора и два ключевых транзистора, сток первого ключевого транзистора соединен с затвором первого нагрузочноготранзис тора и одной из обкладок первого МОПконденсатора, исток - с первой.сигнальной шиной, затвор - с второй сигнальной шиной, сток второго ключевого транзис тора соединен с затвором второго нагрузочного транзистора и одной из обкладок второго МОП-конденсатора, исток - с второй сигнальной шиной, затвор - с пер вой сигнальной шиной, другие обкладки МСв1-конденсаторов сйуслючень1 к третьей шине управления. На чертеже представлена схема усилителя считывания. Усилитель считывания содержит два усилительных транзистора 1 и 2 с общим истоком, соединенных триггерной связью, стоки которых соединены соответственно с первой и второй сигнальными шинами 3 и 4, а общий исток соединен с первой шиной управления 5, два нагрузочных транзистора 6 и 7, истоки которых соединены с соответствующими шинами 3 и 4, а стоки - с второй шиной управления 8, два МОП-конденсатора 9 и 1О и два клю:еы 1х транзистора Ни 12, сток транзистора 11 соединен с затвором транзистора 6 и одной из обкладок МСШ-конденсатора 9, , исток ,- с шиной 3, затвор - с шиной 4, сток тран зистора 12 соединен с затвором транзистора 7 и одной из обкладок МОП-кон денсатора 10, исток - с шиной 4, затво с шиной 3, другие обкладки МОП-конден саторов 9 и 1О подключены к третьей шине управления 13. В исходном состоянии управлякнцая шина 8 подкточена к источнику питания (на чертеже не показан), а сигнальные шины 3 и 4 и управляющая шина 5 заряже ны до опорного напряжения, отключены от источника предзаряда (на чертеже не показан) и сохраняют свои потенциалы на паразитных емкостях. На шине 13 поддерживается низкое напряжение. Заряд, считанный из динамической ячейки памяти (на чертеже не показана) на паразитную емкость одной из сигнальных шин, вызывает изменение ее потенциала, в результате между шинами 3 и 4 возникает информационный разбаланс напряжений. После считывания сигнала из ячейки на паразитную емкость плеча подается отртщательный перепад напряжения на шину 5 и положительный перепад напряжения на шину 13. При этом напряжение на затворах нагрузочных транзисторов 6 и 7 достигает значения большего, чем напряжение питания, что обеспечивает работу этих транзисторов в крутой области характеристик. После подачи сигналов на управляющие шины 5 и 13 начинается процесс опрокидывания усилителя в устойчивое состояние, направление опрокидывания усилителя определяется знаком информационного разбаланса сигнальных шин. Как только величина разбаланса достигнет величины, большей порогового напряжения ключевых транзисторов 11 и 12, отпирается один из них, например 11 (затвор его будет находиться под. более высоким потенциалом), В результате МОП-конденсатор 9 разряжается через транзистор 11 на сигнальную шину, находящуюся под более низким потешдиалом, а нагрузочный транзистор 6 запирается. После окончания процесса опрокидывания усилитель приходит в следующее состояние: нагрузочный транзистор 7 открыт и, находясь в крутой области характеристики, поддерживает потенциал соответствующей сигнальной шины на высоком уровне, транзисторы 1и- 11 также открыты и подл.ерживают потенциал соответствующей сигнальной шины и затвора нагрузочного транзистора 6 на низком уровне. Транзисторы 6, 2и 12 выключены, так как напряжения затвор - исток этих транзисторов меньше порогового. Таким образом, состояние по окончании переходного процесса можно сравнить с состоянием триггера на МОПтранзисторах с дополняющими Т1тами проводимости, т.е. здесь также отсутствуют цепи статического потребления и дифференциальный выходной сигнал на сигнальных шинах равен напряжению питания. Это имеет большое значение для интегральных динамических ЗУ большой и сверхбольшой емкости, так как мощность, потребляемая известными усилителями считывания, составляет 7О-80 ь мощности потребления ЗУ. Применение предлагаемого усилителя позволит снизить мощность потреблений ЗУ в 2-3 раза. Включение нагрузочных транзисторов в данной схеме производится повышенным напряжением, что при сохранени размеров этих транзисторов приводит к повышению быстродействия схемы. Большое значение имеет также увепиненве дифференциального выходного сигнала до напряжения питания. Формула изобретения Усилитель считывания для интеграль.ного запоминающего устройства, содержащий два усилительных транзистора с общим истоком, соединенных триггерной связью, стоки которых соединены соответственно с первой и второй сигнальными шинами, а общий исток соединен с первой шиной управления, два .нагрузочных транзистора, истоки которых оединены с соответствующими сигнальными шинами, а стоки - г второйшиной упра ления, отличающийся тем, что с целью уменьшения потребляемой мопшоств и увеличения быстродействия усвлнтепа считывания, он содержит два М ЯП-кс«денсатора и два ключевых (транзистора,, сток первого ключевого транзистора сое динен с затвором первого нагрузочного транзистора и одной из обкладок первого МОП-конденсатора, исток - с первой сигнальной шиной, затвор - с второй сигнальной шиной, сток второго ключевого транзистора соединен с затвором вто рого нагрузочнсяо транзистора и одной из обкладок второго МОП-конденсатора, исток - с второй сигнальной шиноЙ| за- т вор - с первой сигнальной шиной, другие обкладки МОП-конденсаторов подключены к третьей шине управления.Источники информации, принятые во внимание при экспертизе 1.IEEE,JoOrncie о SoeicT State Circuits , Ofctober 9ТЗ,р.306-307. 2. Электроника, 1973, . 18, с. 77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

U

-- Д

т

Т .J

0-J

ЦТ

Авторы

Даты

1982-05-15—Публикация

1976-08-05—Подача