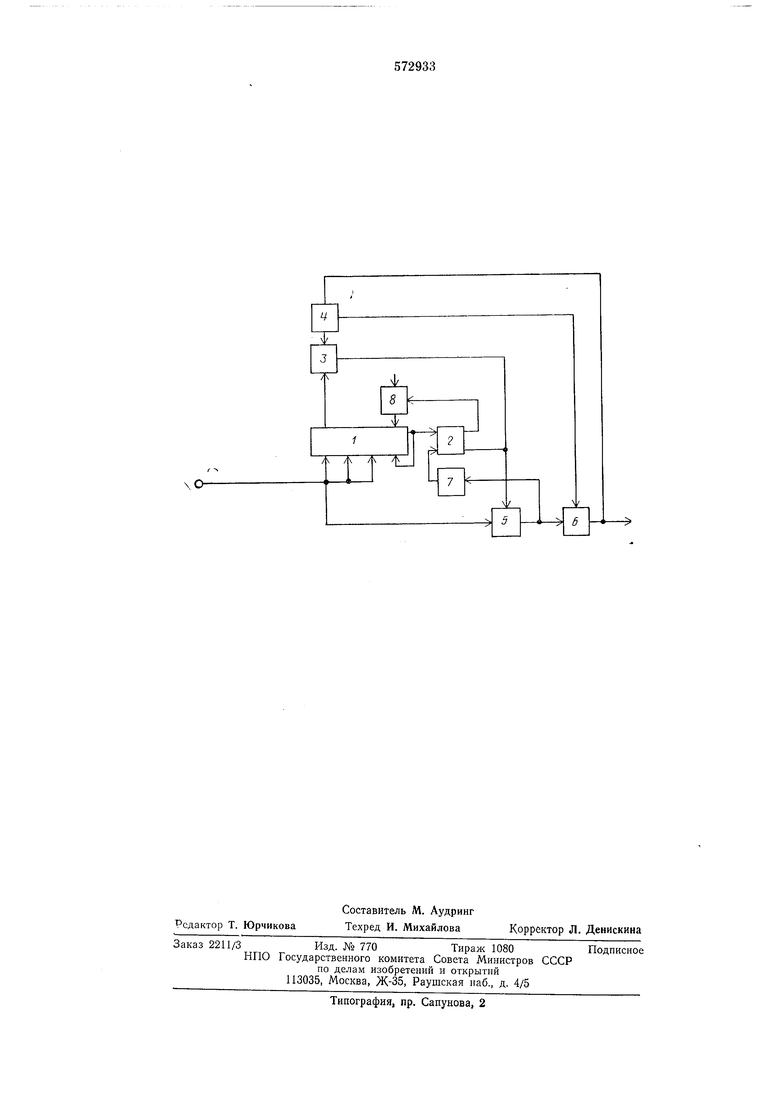

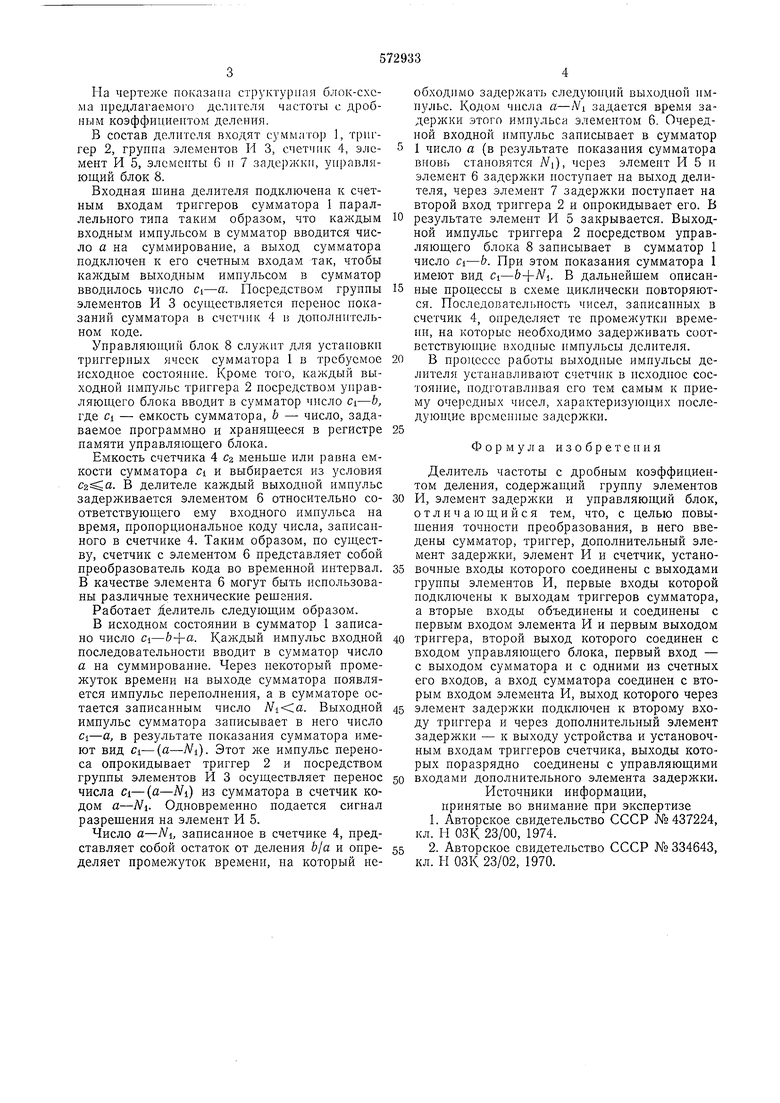

На чертеже показана структурная блок-схема предлагаемого де.иггеля частоты с дробным коэффициентом деления.

В состав делителя входят сумматор 1, триггер 2, групиа элементов И 3, счетчнк 4, элемент И 5, элементы 6 н 7 задержки, управляющий блок 8.

Входная шина делителя подключена к счетным входам триггеров сумматора 1 параллельного типа таким образом, что каждым входным импульсом в сумматор вводится число а на суммирование, а выход сумматора подключен к его счетным входам так, чтобы каждым выходным импзльсом в сумматор вводилось число Ci-а. Посредством группы элементов И 3 осуществляется перенос показаний сумматора в счетчик 4 li дополнительном коде.

Управляющий блок 8 служит для устаиовки триггерных ячеек сумматора 1 в требуемое исходное состояние. Кроме того, каждый выходной импульс триггера 2 посредством управляющего блока вводит в сумматор число Ci-b, где Ci - емкость сумматора, b - число, задаваемое программно и хранящееся в регистре памяти управляющего блока.

Емкость счетчика 4 Са меньше или равна емкости сумматора Ci и выбирается из условия . В делителе каждый выходной импульс задерживается элементом 6 относительно соответствующего ему входного импульса на время, пропорциональное коду числа, записанного в счетчике 4. Таким образом, по существу, счетчик с элементом 6 представляет собой преобразователь кода во временной интервал. В качестве элемента 6 могут быть исиользованы различные технические решения.

Работает Делитель следующим образом.

В исходном состоянии в сумматор 1 записано число Ci-b- -a. Каждый импульс входной последовательности вводит в сумматор число а на суммирование. Через некоторый промежуток времени на выходе сумматора появляется импульс переполнения, а в сумматоре остается записанным число Ni.a. Выходной импульс сумматора записывает в него число Ci-а, в результате показания сумматора имеют вид Ci-(а-Ni). Этот же импульс переноса опрокидывает триггер 2 и посредством группы элементов И 3 осуществляет перенос числа Ci-(а-Ni) из сумматора в счетчик кодом а-Ni. Одновременно подается сигнал разрешения на элемент И 5.

Число а-Ni, записанное в счетчике 4, представляет собой остаток от деления Ь/а и определяет промел ;уток времени, на который необходимо задер кать следуюни1Й выходной импульс. Кодом числа а-/Vi задается время задержки этого импульса элементом 6. Очередиой входной импульс записывает в сумматор 1 число а (в результате показания сумматора вновь становятся NI), через элемент И 5 и элемент 6 задержки поступает на выход делителя, через элемент 7 задержки поступает на второй вход триггера 2 и опрокидывает его. В

результате элемент И 5 закрывается. Выходной импульс триггера 2 посредством управляющего блока 8 записывает в сумматор 1 число Ci-b. При этом показания сумматора 1 имеют вид d-b-f jVi. В дальнейшем описанные процессы в схеме циклически повторяются. Последовательность чисел, записанных в счетчик 4, определяет те промежутки времени, на которые необходимо задерживать соответствуюнще входные импульсы делителя.

В процессе работы выходные импульсы делителя устанавливают счетчик в псходпое состояние, подготавливая его тем самым к приему очередиых чисел, характеризующих последующие временные задержки.

Формула изобретения

Делитель частоты с дробным коэффициентом деления, содержащий группу элементов

И, элемент задержки и унравляющий блок, отличающийся тем, что, с целью повышения точности преобразования, в него введены сумматор, триггер, дополнительный элемент задержки, элемент И и счетчик, установочные входы которого соедннены с выходами группы элементов И, нервые входы которой подключены к выходам триггеров сумматора, а вторые входы объединены и соединены с первым входом элемента И и первым выходом

триггера, второй выход которого соединен с входом унравляющего блока, первый вход - с выходом сумматора и с одними из счетных его входов, а вход сумматора соединен с вторым входом элемента И, выход которого через

элемент задержки подключен к второму входу триггера и через донолнительный элемент задержки - к выходу устройства и установочным входам триггеров счетчика, выходы которых норазрядно соединены с унравляющими

входами дополнительного элемента задержки.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №437224, кл. П ОЗК 23/00, 1974.

2. Авторское свидетельство СССР № 334643, кл. Н ОЗК 23/02, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным коэффициентом деления | 1986 |

|

SU1347184A1 |

| Умножитель частоты следования импульсов | 1976 |

|

SU570064A1 |

| ЦИФРОВОЙ АВТОМАТИЧЕСКИЙ АНАЛИЗАТОР ЧАСТОТНЫХ | 1969 |

|

SU257579A1 |

| Вычислительное устройство | 1972 |

|

SU439803A1 |

| Система для распределения печатной продукции по пунктам назначения | 1987 |

|

SU1618715A1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Устройство для измерения частоты сигналов | 1979 |

|

SU789863A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Универсальный измеритель соотношения линейных скоростей | 1972 |

|

SU451009A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМДЕЛЕНИЯ | 1972 |

|

SU334643A1 |

Авторы

Даты

1977-09-15—Публикация

1976-03-15—Подача