1

Изобретепио относится к цифровой вычислительной технике.

Иэвестб} умножитель частотъ следовгьния HMTiynbcoB низкого и инфракраспо1Ю частотных диапазонов с промежуточным вреь яимпульсным преобразователем, содержащий блок выделения периода и управлепия, запоминающий регистр, суммаа-ор, генератор образцовой частоты и вентили переноса l

Наиболее близким решением к изобретению является умнож-итель, который содержит последовательно включенные генератор эталошюй частоты, делитель частоты, первый элемент И, регистр, первук) группу элементов И, сумматор и элемент ИЛИ, подсоединен 1ый свободным входом к соответствующему выходу блока управления, два других выхода которого соединены соответственно с управляющим входом делителя частоты- и потенциальным входом первого элемента И, а вход является входом умножителя 2. Недостатком этих умножителей является их низкая точность, что обусловлено значительным уровнем паразитной время-импульсной модулжщии

БРлходных частот, порядка сотен и тысяч герц, вызвгипюй умножением эталонной час- ТО1Ъ1 в дробное число .

Целью изобротеш1я является повышение точности умножителя.

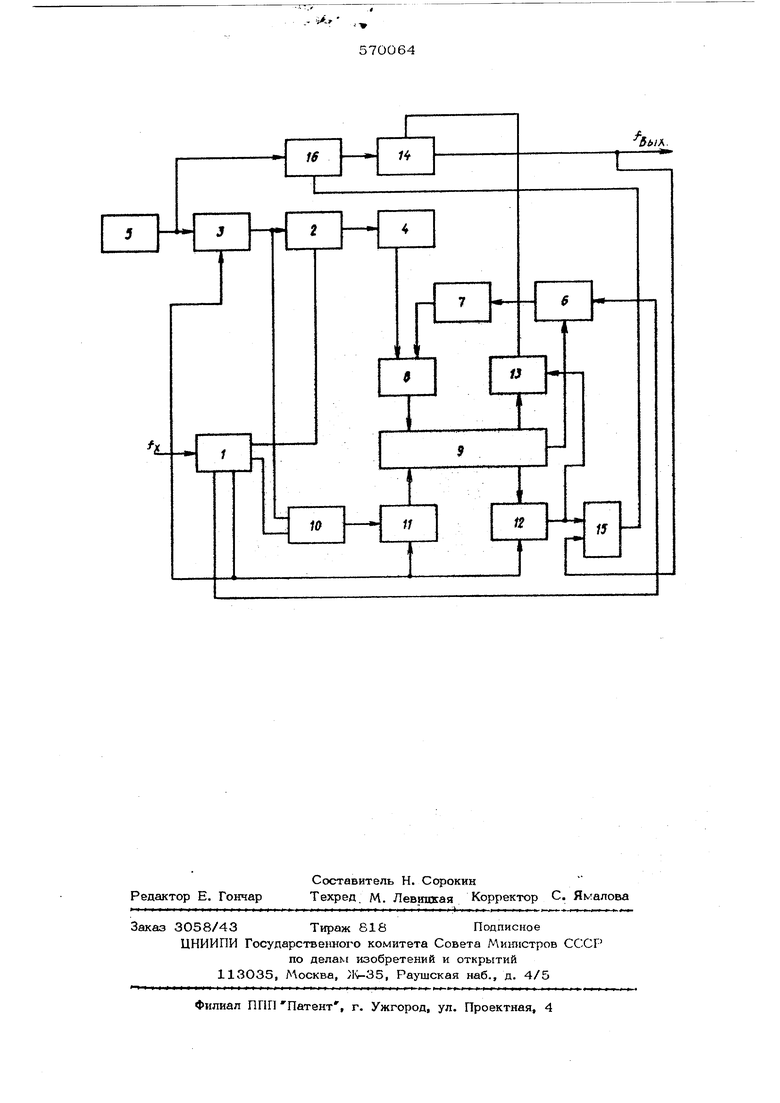

Достигается это тем, что умножитель содержит Второй и третий элементы И, линию Зсщержки, вторую и третью группы элементов И, счетчик, триггер и блок сравнения, первые входы которого соединены с первыми входами элементов И второй груп.пы и с сответствующим выходом блока управления, вторые входы - с выходами разрядов сумматора, а выход подключен к первому входу триггера и к первым входам элементов И третьей группы. Выходы элементов И второй группы подключены к входагл соответствующих разрядов сумматора, а их вторые входы - к выходу вторО1х элемента И, поте1щиалы1ый вход которого соединен с соответствующим выходом блока управления а импульсный вход подключен к выходу делителя частоты, вторые входы элементов И третьей группы подсоединены к выходам соответствующих разрдцов сумматора, а их выходы подключены к установочным вхо лак счетчика, счетный вход которого под- соешнюн через третий элемент И к генератору эталонной частоты, а выход является выходом умножителя и соединен с вт рым входом триггера, подсоединенного выхо дом к поте1щиальному входу третьего эл&мента И, вход линии задержки соединен с выходом элемента ИЛИ, а ее выход с сво- бодньми входами .элементов И первой группы. На чертеже дана- структурная схема ум ножителя частоты следования импульсов. Умножитель содержит блок управления 1, элемент И 2, делитель частоты 3, реги 4, генератор эталонной частоты 5, элемен ИЛИ 6, линию задержки 7, группу 8 элементов И, сумматор 9, элемент И 10, гру пу 11 элементов И, блок сравнения 12, группу 13 элементов И, счетчик 14, триггер 15 и элемент И 16. Умножитель работает следующим образом. Блок управления 1 задает коэффициен умножения К входной частоты f путем подачи разрешающего потешщала на те из элементов группы 11 элементов И, через которые каждым выходным импупьсом элемента И 10 в сумматор 9 введется число К на сумми)Ьование. Число К является также коэффициентом деления делителя частоты 3. Кроме того код числа К подается на блок сравнения 12. В процессе работы блок сраБлення 12 срав1швает число К с дополш/тельным кодом чисел, образующихся в суъ шторе 9. Импульс на выходе блока 12 формщ1уется в момент времени, когда в сумматоре 9 будет записано число с - д , где с - емкость су.матора 9, Д ; К. В случае д К импульс на выходе блока 12 отсутствует. Посредством группы 8 элементов И осуществляется перенос числа, хранящегося в регистре 4, в 9; посредством группы 13 элементов И - перенос показаНИИ сумматора Э в счетчик 14. В исходном состоянии элементы И 2, 1 16 закрыты запирающими потенциалами, по даваемыми с блока управления 1 и триггер 15, соответственно, а показания регистра сумматора 9 и счетчика 14-нулевые. Блоком управлештя 1 элемент И 2 откр вается на один период Т входното ситнала За это время с выхода делителя 3 в репю 4 поступит N 5J -jf Tj импульсов, где f - частота генератора 5. Если запись числа N j( в регистр 4 осзтцествляется в дополнител1-.1юм коде, то покг зания регист ра 4 к концу периода Т будут .(с - } где с екгкость регистра 4. По око1гчании периода входногю смпшла элемент И 2 закрывается (в дальнейшем блок управления 1 не реагирует на входшли; ик1пульсы частоты f Ощювременно с блока управления 1 на элемент ИЛМ 6 выдается импульл;, который, пройдя через линию задержки 7, посредством группы 8 элементов И 8 осуществляет пеоенос числа (с - N)( j из регистра 4 в сумматор 9. Начиная с второго периода входного сшчиьла, блоком управления 1 открывается элемент И 1О, С момента каждый выход- , ной импульс делителя 3 посредством группы 11 элементов И параллельным кодом вводит в cyiw-матор 9 число К, равное коэффициенту умножения. Поскольку совокупность блоков 4, 6, 7, 8, 9 эквивалентна сул матору параллельного типа емкостью t при поступлении на вход группы 11 элементов И числа импульсов Н . на выходе сумматора 9 будет сфор:мировано ровно К-импульсов переполне1 ия и его показания вновь станут равными (с - Nj ), В дальнейшем описанные процессы в этой части схемы будут циклически повторяпгься, а на каждые Nj входных импульсов группы 11 элементов И на выходе сумматора 9 будет форм1фоваться К импульсов, что соответствует умножению частоты iJJ в К раз, Б процессе работы умножителя каждый выходной и uryльc сумматора 9 посредством группы 8 элементов И осуществляет запись числа (с - N , ) в сумматор 9, В результате показания сумматора 9 после каждого его очередного переполнения и записи числа (с - W ) будут {С ) где А - число, оставшееся в сумматоое 9 переполнения, i - 1,2,3,........ф. - переполнения сумматора 9, Поскольку Aj К Д где Д| - остаток от деления - передпоступпениемна вход группы 11 элементов И импульса, соответствующего переполнению сумматора 9, в последнем будет записано число (С -ij). Так как К 5 д. в этот момент на выходе блока сравнения 12 формируется импульс, который посредством группы 13 элементов И записывает в счетчик 14 число (с -Л}) и опрокидывает триггер 15. В результате открывается элемент И 16. С этого момента импульсы частоты с выхода генератора 5 начинают поступать в счетчик 14 на суммирование. С поступлением на его вход д . импульсов па входе счетчика 14 появится выходной импульс устройства, который, опрокидывая триггер 15, закрывает элемент И 16. В дальнейшем описанные процессы в сх ме циклически повторяются. Нетрудно видеть, что выходные импульсы умножителя следуют с периодом, опр&депяемым соотношением .MT ЛВД I К J о 1 к j при атом первое слагаемое правой части последнего соотношения вырабатывается сумматором У, а второе - счетчиком 14. Формула изобретения Умножитель частоты следования импуль сов, содержащий посладовательнс включенные генератор эталонной частоты делитель частоты, первый элемент И, регистр, первую группу элементов И, сумматор и элемент ИЛИ, подсоединенный свободным входом к соответствующему выходу блока управления, два других выхода которого соединены соответственно с управляющим входом делителя частоты и потенциальным входом первого элемента И, а вход является входом згмножителя, отлича ющийся тем, что, с целью повышени точности y нoжитeля, он содержит второй и третий элементы И, линию задержка, вторую и третью группы элементов И, счет чик, триггер и блок сравнения, первые вхо которого соединены с первыми входами элементов И второй гругты и с ссотвс;1ч:тв ющим выходом блока угфавле1П1я, вто{)ые входы - с выходами разрядов сумматора, а выход подключен к первому входу Tpurrti a и к первым входам элементов И третьей группы, выходы элементов И второй подключены ко входам соответствующих разрядов сумматоров, а их в1Х)рые входы к выходу второго элемента И, потенциальный вход которого соединен с соответствующим выходом блока управления, а импульсный вход подклЮЧен к выходу делителя частоты, вторые входы элементов И третьей группы подсоединены к выходам соотвгугстБук щих {1азрядов сумматора, а их выходы подключены к установочным входам счетчика, счетный вход которого подсоединен через третий элемент И к генератору эта- лонной частоты, а выход является выходом умножителя и соединен с вторым входом триггера, подсоединенного выходом к потенциальному входу третьего элемента И, вход линии задержки с выходом элемента ИЛИ, а ее выход со свободными входагли элементов И первой группы. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 32О814, Кл. Q, 06 f 5/00, 1969. 2.Авторское свидетельтсво СССР № 321819, Кл.4 06 f 23/1О, 1969.

.

570064

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Генератор случайного потока импульсов | 1991 |

|

SU1793534A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2025895C1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Умножитель частоты | 1981 |

|

SU1058021A1 |

Авторы

Даты

1977-08-25—Публикация

1976-03-23—Подача