1

Изобретение предназначено для построения синхронных (динамических) устройств вычислительной техники, в частности микровлектроиных.

Известен синхронный логический элемент (СЛЭ), представляющий собой триггер с непосредственными связями на двух многоэмиттерных транзисторах, причем свободные от трйггерных связей эмиттерь одного из транзисторов испопьзуютсй как входные цепи СЛЭ. Для обеспечения установки в определенное состояние при отсутствии на входе сигналов с низким уровнем напряжения один из свободнь1х от трйггерных связей эмиттеров второго транзистора триггера соединен через резистор с общей шиной. Тактирование осуществляетси с помощью транзисторного ключа .l3

Недостатками этого элемента являются использование в схеме резисторов и необходимость создания изолированных областей для размещения резисторов и транзисторов при изготовлении элемента в виде микросх&мы. Все это приводит к увеличению площади, занимаемой-элементом на поверхности

кристалла, к снижению быстродействия вслбоствие влияния значительных емкостей, резисторов и изолирующих структур.

Цель изобретения - уменьшение мощиостк потребляемой элементом от источника питания.

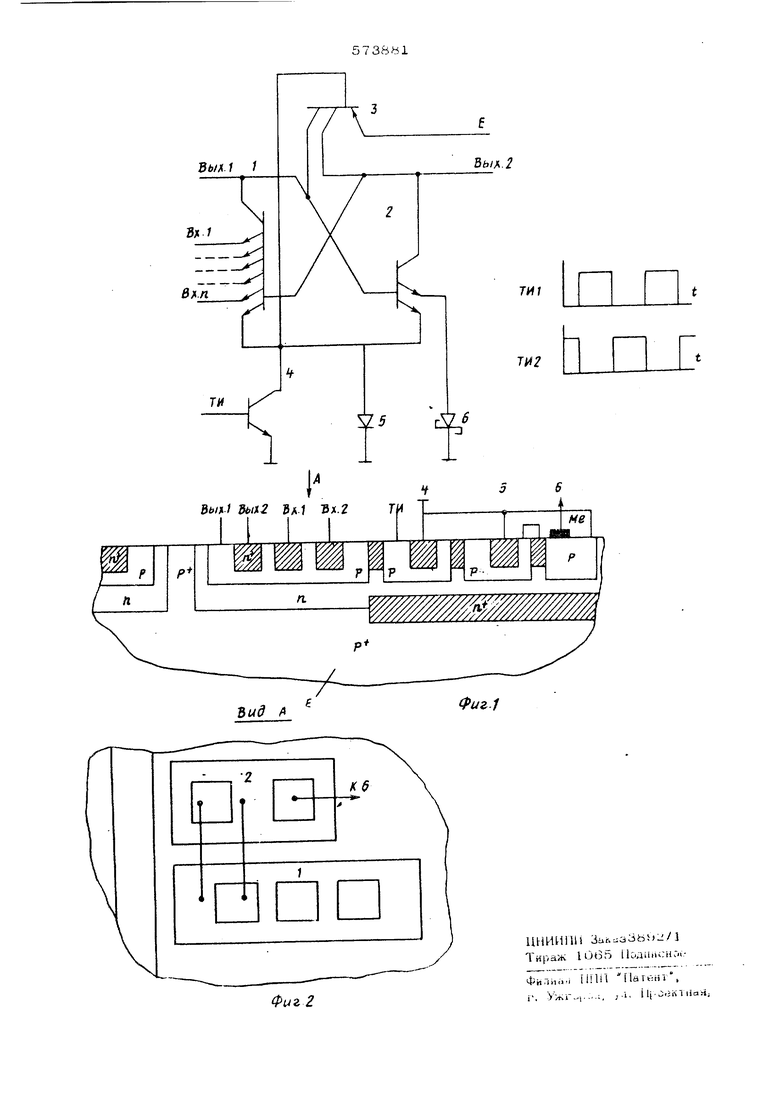

Для этого в синхронный лагическЕЙ jane мент введены двухкбллекторный транзистор, фиксирующий диод н диод с малым прямым падением напряжения (например, диод Шоттки), причем эмиттер-двухкоплекториого транзистора соединен с источником питаняя« база - с, объединенными эмиттерами миог эмиттерйвых транзисторов, коллвктс ы - с соответствующими базами многоэмиттврцых транзисторов, анод фиксирующего диода сое динен с объединенными эмиттерами миогоэмиттерных транзисторов, анод диода с прямым падением напряжения соединен с одним из свободных эмиттеров второго многоэмиттерного транзистора, а катоды ди« дов соединены с общей шиной,На фиг. 1 дана приииипвальиая впектряческая схема элемента; иа фвг« 2 - ТОПШО гия элемента. СиНАрон 1ый логический элемент содержит два перекрестно соединенные MHOJ09MHTTepкые транзисторы 1 и 2, oofjaayiouuie трштер токоэадаюший транзистор 3, ключевой Tpatfзистор 4, фиксируКэщий диод 5 ( р ) и Д11ОД 6 с падением напряжения Источник питающего напряжения включается между эмиттером транзистора 3 и общей шиной. Тактовые импульсы подаются на базу транзистора 4,Входные логические сиг налы подаются на свободные от триггерных связей эмиттера транзистора 1, а выходные снимаются с коллекторов транзисторов 1 и Зиемент может работать в режиме нения (транзистор 4 насыщен при подаче им пульса. Т( ) и в режиме установки (транзно тор 4 закрыт), В режиме хранения, потенциала на входных эмиттерах элемента; соединенного с ана логичными элементами второй фазы тактовы HNmyabcob, могут изменяться от tl до Е (U напряжение на диоде 5 при закрытом транзисторе 4). Так как потенциал объединенных эмиттеров транзисторов i и 2 равен Uu а-г,, . изменение логических состой .. пЛС НИИ элементов второй фазы ТИ ые изменяет состояние рассматриваемого, элементаа так катчнАс ГИ КэтчнАс Р - П « переходы входных эмиттеров заперты ( НАС пряжение насыщения транзистора 4), В режиме установки потенциал объединен .ных эмиттеров равен 11,,. а потенциалы входных эмиттеров могут изменяться от K.atg. Е« Если хотя бы один из входных эмиттеров имеет потенциал 1/ д ,,д , то р - ед переход этого эмиттера открыт и базовый ток отводится от транзистора 1 на ободую шину транзистор i выключается, транзистор 2 включается,,, Если все входные эмиттеры имеют поте№ циал Е, то транзистор 1 включается, а Tpai зистор 2 выключается, так как базовый ток отводится от транзистора 2 через диод 6 на общую шину. Условие работоспособности элемента запишетгся в виде UK.STW. Из приведенного выше ясно, что элемент реализует логическую функцию , Из приведенной на фиг. 2 топологии СЛЭ buaiii), что схема элемента позволяет вылолEiHTb ьсе элементы одной фазы ТИ в общей изоли| о шиной to/iaCTH, причем подложка яв лается мшч-ером транзистора 3s обслулсиаклцего элементы обеих фаз. Ключевой тра1 истор 4, диод 5, база транзистора 3 - обие для элементов одной фазы ТИ, Коллекоры транзистора 3 являются базами тра исторов 1 и 2. База транзистора 3 является э.миттером транзисторов 1 и 2 и колектором транзистора 4, Отсутствие резисторов, совмещение фун1йций нескольких компонентов в одной полупроводниковой области обеспечивает высокую ст епень инте рации при изготовлении апемента| Б составе И, дает выигрыш в быстродействии при равной с известным э«&ментом потребляемой мощности-, Лри1у1енение предлагаемого синхронного логического элемента СЛЗ для создания и тегральных цифровых устройств позволит увеличить степень интеграции элементов на кристаллев увеличить быстродействие и умеиьшить потребляемую элементом мощность, Формула изобретения Синхронный логический элемент, содержащий два многоэмиттерных транзистора, коллекторы которых перекрестно соединены с базами, один из эмиттеров каждого многоэмиттерного транзистора соединен с коллектором биполярного транзистора, эмиттер ко торого соединен с общей щнной, а база - с тактовым входом элемента, свободные эмиттеры первого многоэмиттерного транзистора соединены с входными шинами элемента, отличающийся тем, Что, с целью уменьшения потребляемой мощности, в Hiero введены .двухколле, транзистор, фиксирующий диод с малым прямым падением напряжения (например, диод Шоттки), причем эмиттер, двухколлекторного транзистора соединен с источником питания8 база - собъединенными эмиттера.ми многоэмит1ерных транзисторов, коллекторы - с соответствующими базами многоэмиттерных транзисторов, анод фиксирующего диода соединен с объединенными эмиттерами многоэмиттерных транзисторов, анод диода с малым прямым падением напряжения соединен с одним из свободных эмиттеров второго многоэмиттерного транзистора, а катоды диодов соединены с общей шиной. Источники информации, принятые во вни-« мание при экспертизе: 1е Микроапектроника, од,ред. Л, А, Васеикоьа, вып. 6, М, Советское радио, 1975, с, и,о.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Логическое устройство | 1984 |

|

SU1213521A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Быстродействующий микромощный логический элемент и-или/и-или-не | 1977 |

|

SU624369A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Микромощный логический элементи-или/и-или-HE | 1979 |

|

SU832725A1 |

| Логический элемент | 1982 |

|

SU1058061A1 |

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

Авторы

Даты

1977-09-25—Публикация

1976-04-02—Подача