(54) УСТРОЙСТВО ИЗМЕРЕНИЯ ИСКАЖЕНИЙ СТАРТСТОПНЫХ СИГНАЛОВ

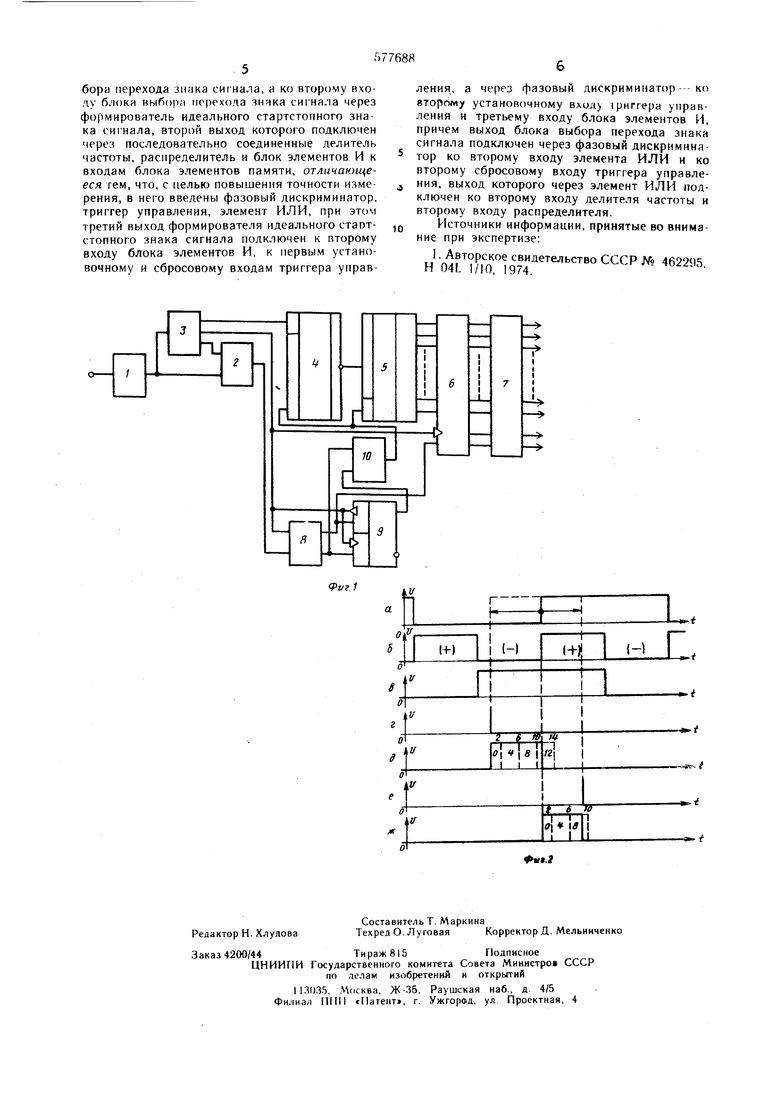

дам блока 7 элементов памяти, фазовый дискриминатор 8, триггер 9 управления, элсмен1 ИЛИ 10, при этом третий выход формирователя

3идеального.стартстопного знака сигиала подключен к второму входу блока элементов И 6, к первым установочному и сбросовому входам триггера 9 управления и через фазовый дискриминатор 8 ко второму установочному входу триггера 9 управления н третьему входу блока элементов И 6, причем выход блока 2 выбора перехода знака сигнала подключен через фазовый дискрнмннатор 8 к второму входу элемента ИЛИ 10 и ко второму сбросовому входу триггера 9 управления, рчход которого через элемент ИЛИ 10 подключен ко второму входу делителя

4частоты и ко второму входу распределителя 5.

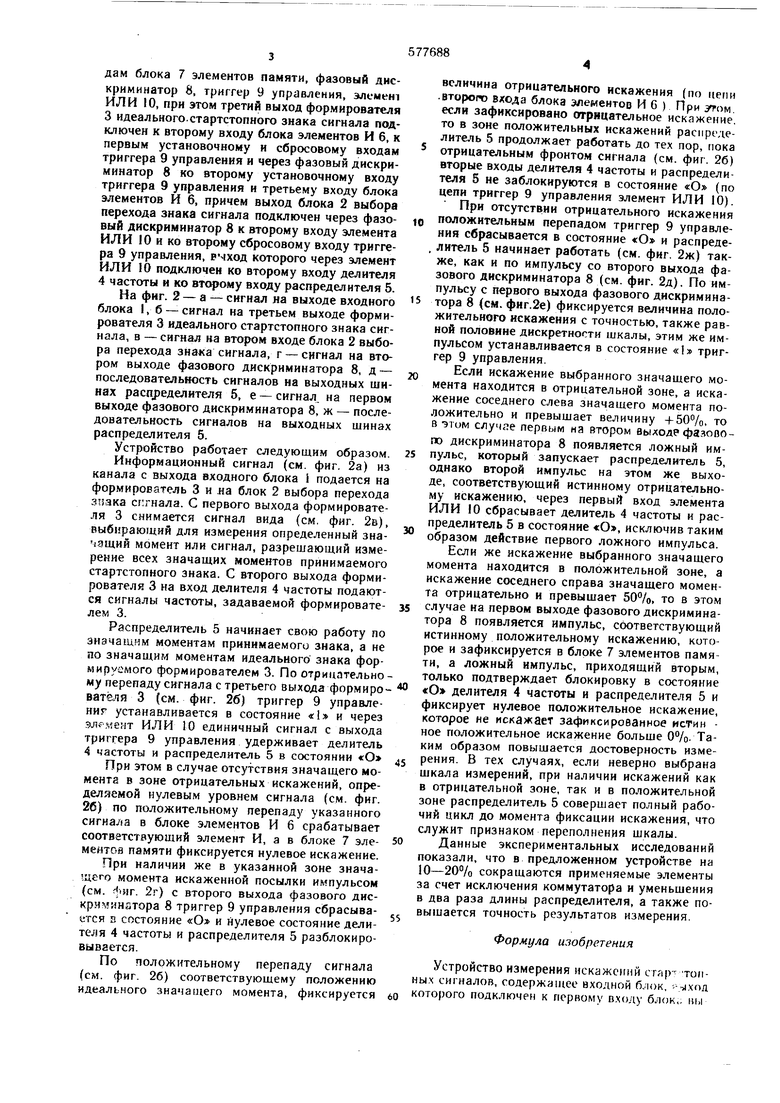

На фиг. 2 - а - сигнал на выходе входного блока I, б -сигнал на третьем выходе формирователя 3 идеального стартстопного знака сигнала, в - сигнал на втором входе блока 2 выбора перехода знака сигнала, г - сигнал на втором выходе фазового дискриминатора 8, д - последовательность сигналов на выходных шинах распределителя 5, е сигнал, на первом выходе фазового дискриминатора 8, ж - последовательность сигналов на выходных шинах распределителя 5.

Устройство работает следуюшнм образом.

Информационный сигнал (см. фиг. 2а) из канала с выхода входного блока 1 подается на формирователь 3 и ла блок 2 выбора перехода сигнала. С первого выхода формирователя 3 снимается сигнал вида (см. фиг. 2Б), выбирающий для измерения определенный знагащий момент или сигнал, разрешающий измерение всех значащих моментов принимаемого стартстопного знака. С второго выхода формирователя 3 на вход делителя 4 частоты подаются сигналы частоты, задаваемой формирователем 3.

Распределитель 5 начинает свою работу по значащим моментам принимаемого знака, а не по значащим моментам идеального знака формируемого формирователем 3. По отрицательному перепаду сигнала с третьего выхода формирователя 3 (см. фиг. 26) триггер 9 управление устанавливается в состояние «1 и через э.п,меат ИЛИ 10 единичный сигнал с выхода триггера 9 управления удерживает делитель 4 частоты и распределитель 5 в состоянии «О

При этом в случае отсутствия значащего момента в зоне отрицательных искажений, определяемой нулевым уровнем сигнала (см. фнг. 26) по положительному перепаду указанного сигнала в блоке элементов И 6 срабатывает соответствующий элемент И, а в блоке 7 элементоа памяти фиксируется нулевое искажение.

При наличии же в указанной зоне значащего момента искаженной посылки импульсом (см. фиг. 2г) с второго выхода фазового дискриминатора 8 триггер 9 управления сбрасывается 3 состояние «О и йулевое состояние делителя 4 частоты н распределителя 5 разблокнровывается.

По положительному перепаду сигнала (см. фиг. 26) соответствующему положению идеального значащего момента, фиксируется

величина отрицательного искажения (по кепи .второго входа блока элементов Мб) При если зафиксировано отрицательное искажение. то в зоне положительных искажений распределитель 5 продолжает работать до тех пор, пока отрицательным фронтом сигнала (см. фиг. 26) вторые входы делителя 4 частоты и распределителя 5 не заблокнруются в состояние «О (по цепи триггер 9 управления элемент ИЛИ 10). При отсутствии отрицательного искажения

положительным перепадом триггер 9 управления сбрасывается в состоянне «О и распреде. литель 5 начинает работать (см. фиг. 2ж) также, как и по импульсу со второго выхода фазового дискриминатора 8 (см. фиг. 2д). По импульсу с первого выхода фазового днскриминатора 8 (см. фнг.2е) фиксируется величина положительного искажения с точностью, также равной половине дискретности шкалы, этим же импульсом устанавливается в состояние « триггер 9 управления.

Если искажение выбранного значащего момента находится в отрицательной зоне, а искажение соседнего слева значащего момента положительно и превышает величину -1-50%, то в -этим случае первым на втором выходе фазовопо дискриминатора 8 появляется ложный нмпульс, который запускает распределитель 5, однако второй импульс на этом же выходе, соответствующий истинному отрицательному искажению, через первый вход элемента ИЛИ 10 сбрасывает делитель 4 частоты и распределитель 5 в состояние «О, исключив таким образом действие первого ложного импульса. Если же искажение выбранного значащего момента находится в положительной зоне, а нскажение соседнего справа значащего момента отрицательно и превышает 50°/о, то в этом

случае на первом выходе фазового дискриминатора 8 появляется импульс, соответствующий истинному положительному искажению, которое и зафиксируется в блоке 7 элементов памяти, а ложный импульс, приходящий вторым, только подтверждает блокировку в состояние

«О делителя 4 частоты и распределителя 5 и фиксирует нулевое положительное искажение, которое не искажает зафиксированное истин ное положительное искажение больще 0%. Таким образом повыщается достоверность измерения. В тех случаях, если неверно выбрана шкала измерений, при наличии искажений как в отрицательной зоне, так и в положительной зоне распределитель 5 совершает полный рабочий цикл до момента фиксации искажения, что служит признаком переполнения шкалы.

Данные экспериментальных исследований показали, что в предложенном устройстве на 10-20% сокращаются применяемые элементы за счет исключения коммутатора и уменьшения в два раза длины распределителя, а также повышается точность результатов измерения.

Формула изобретения

Устройство измерения искажений стя|) топны.х сигналов, содержащее входной б./иж, -ыхпд Q которого подключен к первому входу блок.; HI.I

бора перехода знака сигнала, а ко второму входу блока Bhifiopn перехола знака сигнала через формирователь идеального стартстопного знака сигнала, второй выход которого подключен через последовательно соединенные делитель частоты, распределитель и блок элементов И к входам блока элементов памяти, отличающееся тем, что, с целью повышения точности измерения, в него введены фазовый дискриминатор, триггер управления, элемент ИЛИ, при этом третий выход формирователя идеального стаотстопного знака сигнала подключен к второму входу блока элементов И, к первым установочному и сбросовому входам триггера управления,, а через фазовый дискриминатор---ко второму установочному входу триггера управления и третьему входу блока элементов И, причем выход блока выбора перехода знака сигнала подключен через фазовый дискриминатор ко второму входу элемента ИЛИ и ко второму сбросовому входу триггера управления, выход которого через элемент ИЛИ подключен ко второму входу делителя частоты и второму входу распределителя.

Источники информации, принятые во внимание при экспертизе:

I. Авторское свидетельство СССР № 4622Ч5 Н 04L 1/10, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель краевых искажений дискретных сигналов | 1977 |

|

SU636814A1 |

| Устройство для искажения стартстопногоТАКСТА | 1979 |

|

SU843276A1 |

| Регенератор приемника стартстопных телеграфных сигналов | 1976 |

|

SU641671A1 |

| Устройство синхронизации | 1981 |

|

SU1159173A1 |

| Устройство для измерения исправляющей способности телеграфных приемников | 1978 |

|

SU696623A1 |

| Устройство для синхронизации двоичных сигналов в каналах с постоянными преобладаниями | 1981 |

|

SU1125760A2 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Измеритель краевых искажений | 1977 |

|

SU687615A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство для фазирования электронного стартстопного регенератора | 1982 |

|

SU1073896A1 |

Авторы

Даты

1977-10-25—Публикация

1976-03-30—Подача