1

Изобретение относится к передаче дискретных сообщений и может быть иопопьзовано для обеспечения- тактовой синхронизации приемной части аппаратуры. Известно устройство поэлементного, фазирования, содержащее задающий .генератор, блок управления, входной блок, управляющий делитель и формирователь дополнительных корректирующих импульсов 1.,0

Недостатками данного устройства являются низкая точность, низкая помехоустойчивость и малое быстродействие фазирования.

Известно также устройство тактовой 5 синхронизации, содержащее посдедовательгГ; но соединенные первый реверсивный , первый триггер, первый элемент И, . блок управления, управляемый делитель, делитель частоты, первый элемент задер-20 яоси, интеграторы и первый дешифратор, выходы которого через управляемый д& питепь подсоединены к второму входу блока управления, последовательно сое- .

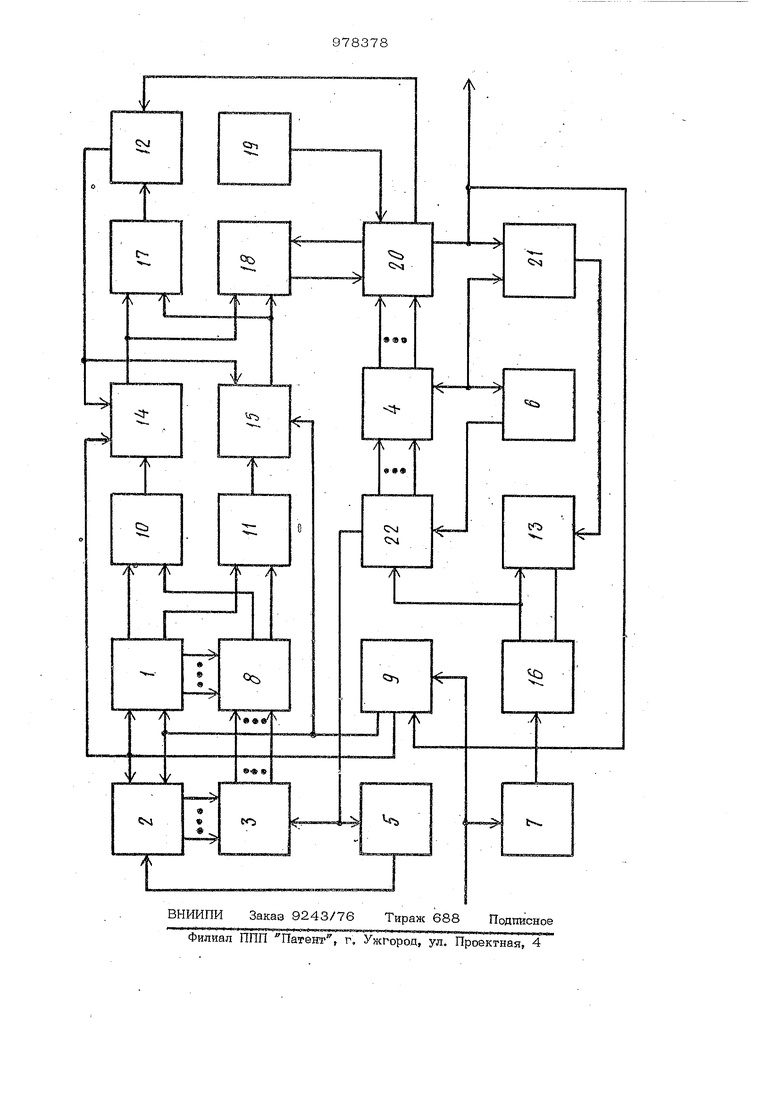

диненные второй дешифратор, коммутатор, второй триггер и второй элемент И, выход которого подсоединен к третьему , входу блока управления, последовательно соединенный второй элемент задержки, второй реверсивный счетчик и второй дешифратор, второй вход которого объединен с входом второго элзиюнта задержки, задающий генератор, выход которого через другой вход управгасемого делите-. ля подсоединен к первому входу фазового аискримннатора,второй вхоп которого объецинен с входом формирователя перецнего фронта .импульса, и является входом уст ройства, при атом первый выход фазово- . го дискриминатора подсоединен к объедвненным вторым входам второго реверсявного счетчика, а второй выход фазового дискриминатора подсоединен к третьему входу второго реверсивного счетчика и объединенным вторым, входам первого реверсивного счетчика и второго элемента И, причем второй выход первого реверсивного счетчика подсоединен к второму входу второго триггера, а к второму входу первого триггера подкгаочен второй выход коммутатора, к соответствующем которого подключена. соответствующие выходы первого реве1 сивного счетчика j 2. . Недостатками данного устройства являются тюкая точность синхронизации и высокая сложность реализации, обусловленные высоким уровнем помех в канале СВЯЗ.И... . Цель изобретения - повышение точной ти синхронизации при упрощении устройства лутем -1скшочения части дешифраторов и управляемых делителей. Для достижения поставленной цели в устройство тактовой синхронизации, содер кащее последовательно соединению первый реверсивный счетчшс, первый триг гер, первый элемент И, блок управления, управляемый делитель, делитель частоты, первый элемент задержки, интеграторы и первый дешифратор, выходы которого через управляемый делитель подсоединены к второму входу блока управления, последовательно соединенные второй дешифратор, коммутатор, второй триггер и второй эле мент И, выход которого подсоединен к третьему входу блока управления, последовательно соединенные второй элемент задержки, второй реверсивный счетчик и второй дешифратор, второй вход которого объединен с входом второго элемента задержки, зайающий генератор, выход которого через другой вход управляемого делителя подсоединен к первому входу фазового дискриминатора, второй вход кото рого объединен с входом формирователя переднего фронта импульса и является вхоаом устройства,при этом первый выход ;фазового дискриминатора подсоединен к объединенным вторым, входам второго ре- версивного счетчика и- первого элемента И и первому входу первого реверсивного счетчика, а второй выхоа фазового дискриминатора подсоединен к третьему входувторого реверсивного счетчика и объединенным вторым входам первого реверсивного счетчика и второго элеме та И, тричем второй выход первого ревер сивного счетчика подсоединен к второму входу второго триггера, а к второму вхо ду первого триггера подключен второй выход коммутатора, к соответствующим входам которого подключены соответстщющие выходы первого реверсивного счет чика, введены последовательно соединенн третий элемент И и третий триггер, по- следовательно соединенные элемент ИЛИ и четвертый триггер, к второму входу которого подключён третий выход управляемого делителя, а выход подсоединен к третьим входам первого и второго элементов И соответственно, выходы которых подсоединены к первому и второму входам элемента ИЛИ, при этом выход формиро-вателя переднего фронта импульса через последовательно соединенные третий элемент И и интегратор подсоединен к входу второго элемента задержки, а второй выход делителя частоты через третий триг гер подсоединен к второму входу третьего И. На чертеже представлена электрическая структурная блок-схема устройства тактовой синхронизации. ХС- Ройство тактовой синхронизации содержит первый и второй реверсйвньш счетчики 1 и 2, первый и второй дешифраторы 3 и 4, первый и второй элементы задержки 5 и 6, формирователь передн&го фронта импульса 7, коммутатор 8, фазовый дискриминатор 9, первый, второй, тпетий и четвертый триггеры 1О-13, первый, второй и третий элементы И 14-. 16, элемент ИЛИ 17, блок 18 управлеи ния, задающий генератор 19, управляемый делитель 20, делитель 21 и интегратор 22. Управляемый делитель 2О может быть реализован в виде набора счетиых триг- . геров и коммутатора. В зависимости от того, на каком из третьих входов упра&ляемого делителя 20 имеется уровень напряжения логической единицы, коммута тор управляемого делителя 20 включает блок 18 управления (первый выход и второй вход управляемого делителя 20) между выходом и входом соответствующих последовательно включенных, счетных триггеров управляемого делителя 2О, т.е. изменяет шаг дискретизации подстройки частоты. На втором выходе упраашемого делителя 20 формируется с частотой телеграфирования тактовый меандр, а на третьем выходе - следующие с той же частотой импульсвые сигналы. В качестве делителя 21 может быть использован типовой счетчик, имеющий импульсные выходы. Период следования сигналов на первом выходе депитепя 21 определяет время, в течение которого производится аналда структуры привима мых сообщешй, на втором выходе делвтеля 21 формируются импульсы с частотой, вдвое меньшей частоты телеграфирования. В качестве интегратора 22 может быть использован типовой счетчик.имеющий импульсный вход, вход сброса, потенциальные выходы каждого разряда (являющиеся первыми выходами интегратора) и импуль сный выход одного из промежуточных раз рядов счетчика (являющийся вторым выходом интегратора). Устройство работает следующим образом. Последовательность импульсов высокой частоты поступает с выхода задающего генератора 19 на первый вход управляем го делителя 2О, на вторам и третьем вы ходах которого формируются послеаователь- кости тактовых импульсов (на втором вы ходе формируется тактовый меандр, а на третьем - узкие импульсы), следуемых с частотой, близкой к..скорости дискретной мопуляции 1 скорости телеграфирования принимаемь1х сообщений, поступающих на вход формирователя 7 переднего фронта импульса и фазового дискриминатора 9. Фазовый дискриминатор 9 осуществляет сравнение фазы принимаемых элементов сообщения с фазой тактовых импульсов и при их несовпадении на одном из его выходов формируется корректирующий импульс (добавления или вычитания),поступающий на соответствующие входы (суммирующие или вычитающие) реверсив ных счетчиков 1 и 2. Реверсивный счетчик 1, осуществляя частичную защиту от ложной подстройки частоты при случайных искажениях принимаемых элементов сообщения, производит усреднение входны величин. Если число импульсов, поступающих на один из входов (например, суммирующий) реверсивного счетчика 1, превысит число импульсов, поступивших на его второй вход (вычитающий), на величину, равную коэффициенту пересчета реверсивного счетчика 1, на одном из выходов его последних разрядов (в данном случае на втором выходе, т.е. на выходе последнего разряда добавления) формируется импульс, устанавливающий соответствующий триггер (в данном случае триггер 1О) в единичное состояние, подготавливающий к работе соответствующий элемент И (в данном случае элемент И 14) по первому входу. Сброс триггера 1О в нулевое состояние для.защиты от случайных искажений принимаемых элементов сообщения производится через коммутатор 8 сигналом с выхода промежуточного разряда вычитания реЬерсивного счетчика 1, т.е. частично усреднейным сигналом. Аналогичным образом, установка в единичное состояние триггера ll производится максимально усредненным сигналом с третьего выхода (выхода последнего разряда вычитания) реверсивного сче-рчика 1, а его сброс в нулевое состояние частично усредненным сигналом, с второго выхода коммутатора 8 (т.е. сигналом с выхода промежуточного разряда добавления реверсивного счетчика 1). Для обеопечения быстродействия и точности фазп|рования в условиях сильных помех коэ4 фидиент частичного усреднешш сбросовых сигналов сделан переменным, т.е. комму татор 8 осуществляет коммутацию сбросовых входов триггеров Ю и 11 с выходами определенных разрядов вычитания и добавления реверсивного счетчика 1 в зависимости от того, на каком из перм вых входов коммутатора 8 (выходов д&щифратора 3) сформирован уровень на-, пряжения логической единицы. Сигнал на -определенном выходе дещифратора 3 формируется в зависимости от кйда числа, записанного в реверсивный счетчик 2, т.е. в зависимости от соотношения чиола импульсов добавления и вычитания (т.е. от ре жима, работы устройства), поступивщих с выходов фазового дискриминатора 9 за промежуток времени двумя импульсами на вторсмл выходе и тегратора 22, что позволяет згчесть-структуру принимаемых сообщений и повысить точность и быстродействие устройства (интегратор 22 заряжается передними фронтами принимаемых элементов сообщения). Ввод информации в дешифратор 3 провз водится сигналом с второго выхода интегратора 22. Этот же сигнал, задержанный в элементе 5 задержки на время, приблвн зительно равное длительности импульса, осуществляет сброс реверсивного счетчика 2 в нулевое состояние. Емкость ревв1 сивного счетчика 2 вь1бирается достаточной для того, чтобы за время между сбросовыми импульсами не произошло его переполнение., №лпульсы, следующие с частотой тепе графирования, с третьего выхода управляемого делителя 20 периодически устанавливают триггер 12 в единичное состо- я.ние, единичный уровень напряжения с выхода которого подготавливает к работе по ретьим входам элементы И 14 и 15. Как следует вз приведенного выше роцесса управления триггерами 1О и 11, ни могут одвовременно находиться в остоянии логического нуля, в единичном же состоянии может находиться только один из триггеров (триггер 10 или триггер 11). В случае, если триггер 10 и 12 оба находятся в единичном состоянии, то первый же корректирующий импульс добавления {с4)ормироваНный на первом выходе фазового дискриминатора 9 без усреднения проходит через элемент И на суммирующий вход блока 18 уп равления. Одновременно с этим импульс с вьгхода элемента И 14 через элемент ИЛИ 17 постуг 1ет на сбросовый вход триггера 12, п реводя его в нулевое состояние и запрещая (по третьему входу) прохождение импульсов через элемент И 14. Вследствие того, что установка в единичное состояние триггера 12 производится с частотой телеграфирования, за время, равное длительности одного элемента сообщения, на вход блока 18 уиравления не может пройти более одного корректирующего импульса {истинного ил лож1« го)1 что повышает помехоустойчивость устройства и точность фазирования (т.к. истинные корректирующие импульсы формируются только пофронтам принимаемого элемента сообщения). Аналогичным образом триггер 12i управляя элементом И 15, уменьшает число ложных корректирующих импульсов и 1читания проходящих на исключающий вход блока/ 1§ управления. . Сигналы с выходов элементов И 14 и И 15 пбступают на суммирующий и исключающий входы блока 18 управления, вследствие чего изменяется количество импульсов высокой частоты (поступающих с выхода задающего генератора 19) подвергаемых делению в управляемом делителе 20, и осуществляется подстройка частоты и-фазы следования тактовых импульсов на выходе устройства. Шаг подстройки (дискретизация) частоты и фазы тактовых импульсов, т.е. величина смещения тактового импульса на выходе устройства от его основного положения, приходящаяся ва один добавленный или исключенный импупьс, подвергаемый делению в управляемом делиt теле 20, устанавливается в зависимости от того, на каком из выходов дешифратора 4 имеется уровензь напряжения логи ческой единицы. Уровень напряжения логической единицы на определенном выходе дещифратора 4 устанавливается в заврсимости от показаний интегратора 22. Ввод показаний интегратора 22 в дещиф ратор 4 производится через промежуток времени, равный периоду следования импульсов на первом выходе делителя 21 и определяющий число элементов. принимаемого сообщения; анализ которого характеризует среднюю частоту чередования единичных и нулейь1х посылок и их групп в принимаемом сообщении, т.е. их статистическую характеристику.. Емкость интегратора 22 выбирается достаточной для того, чтобы за время между сбросовыми импульсами, поступающими с первого выхода делителя 21 через элемент 6 задержки, не произощло его переполнение. На информационный вход интегратора 22 через эле мент И16 С выхода формирователя 7 переднего . фронта импульса поступают импульсы, соответствующие по времени моментам перехода на входе устройства нулевых посылок принимаемого сообщения в единичные. Прохождением передних фронтов пр.. нимаемых элементов сообщения через . элемент И 16 (поступающих на его второй вход) управляет триггер 13, единичный уровень напряжения с выхода, которого (поступающий на первый вход эл&мента И 16) открывает элемент И 16 по первому входу. Уста новка триггера 13 в единичное состояние производится сигналами с второго выхода делителя 21, частота следования которых вдвое ниже частоты телеграфирования (дискретной модуляции) принимаемых элементов сообщения. Сброс триггера 13 в нулевое состояние осуществляется сигналом с выхода элемента И 16. Вследствие этого значительно умейьщается вероятность прохождения на информационный вход интегратора 22 пожных импульсов, обу... словленных дроблениями в .канале связи принимаемых элементов сообщения. Чем чаще чередуются единичные и , нулевые элементы или их группы в составе принимаемых сообщений, тем выше показания интегратора 22 и. тем меньше шаг подстройки частоты управляемого делителя 2О, устанавливаемый дешифратором 4 (путем включения блока 18 управления между соответствующими разрядами управляемого делителя 20). Аналогичным образом, чем чаще чередуются единичные к нулевые элементы сообщения йа входе устройства, тем меньше период следований сигнапоз ва втором выходе интегратора 22,(т.е. тем меньше промежуток вр«лени/ в течение которого реверсшавым счетчиком 2 определяется соотнршеше чксла кмпупьсов добавления и вычитания, формврузмык дискримиватором 9.

При наличии в канале связи ис1шжет1й принимаемых элементов сообщения, заключающихся в формировании ложных значащих моментов, на выходе формирователя переднего 4ронта импульсов наряду с

истинными (т.е. сформированными при переходе нулевого элемента принимаемого сообщения в, последующий единичный элемент) формируются и ощибочные (т.е. вызванные помехами) импульсы. Однако введение третьего элемента И и четвертого блокировочного триггера, устанавливаемого в едишиное состояние с вдвое меньшей частотой, чем частота телеграфирования, и сбрасываемого в нулевое состояние первым же передним фронтом принимаемого сообщения, приводит к значительному уменьщению писла ложных импульсов, осу ществляющих заряд интегратора. Вследствие этого при определении структуры (средней частоты чередования единичных и нулевых элементов сообщения или их групп) принимаемых сообщений допускается значительно меньшая ошибка, чем в известном устройстве.

Повышение точности синхронизации обеспечивается в устройстве введением защиты (элемент ИЛИ и третий триггер) от прохождения на суммирутощий и исключающий входы блока управления ложных обусловленных дроблетгями) корректирующих импульсов.

Технико-экономическая эффективность данного устройства состоит в повышении точности синхронизации при использова- ипи устройства в каналах связи с высоким уровнем помех и высоких требованиях к помехоустойчивости, точности и быстра действию восстановления тактовой синхронизации.Формула изобретения

Устройство тактовой синхронизации, содержащее последовательно соединенные первый реверсивный счетчик, первый триг гер, первый элемент И, блок управления, управляемый делитель, делитель частоты, первый элемент задержки, интегратор и первый дешифратор, выходы;которого через управляемый делитель подсоединены к второму входу блока управления, последовательно соединенные второй д&пшфратор, коммутатор, второй триггер и второй элемент И, выход которого подсоединен к третьему входу блока управления, последовательно соединенные второй элемент задержки, второй реверсивный счетчик и второй дешифратоц, второй вход которого объединен с входом второго элемента задержки, задающий х нератор, выход которого через другой вход управляемого делителя подсоединен к первому входу фазового -дискриминатора, второй вход которого объединен с входом формирователя переднего фронта импульса и является входом устройства, лри этом первый выход фазового дискри1минатора подсоединен к объединенным вторым входам второго реверсивного счетчика и первого элемента И и первому входу первого реверсивного счетчика, a второй выход фазового дискриминатора под соединен к третьему входу второго реверсивного счетчика и объединенным вторым входам первого реверсивного счетчика и второго элемента И, причем второй выход первого реверсивного счет чика подсоединен к второму входу второго триггера, а к второму входу первого триггера подключен второй выход коммутатора, к соответствующим входам которого подключены соответствующие выходы первого реверсивного счетчика, отличающееся тем, что, с целью повышения точности синхронизации при упрощении устройства путем исключения части дешифраторов и управляемых дел1ггелей, введены последовательно соединенные третий элемент И и третий , послеаовательно соеаиненные

элемент ИЛИ и четвертый триггер, к второму входу которого подключен трет тий выход управляемого делителя, а выход подсоединен к третьим входам nei вого и второго элементов И соответственно, выходы которых подсоединены к первому и второму входам элемента РШИ, при этом выход формирователя переднего фронта импульса через последовательно соединенньге третий элемент И и инт&гратор подсоединен к входу второго эл&мента задержки, а второй выход делителя частоты через третий триггер подсоединен к второму входу третьего элемента И.

Источники информации, принятые во внимание при экспертизе ;

1. Авторское свидетельство СССР 467490, кл. Н 04L. 7/02, 1972.

2. Авторское сввдетельство СССР о заявке № 292О489/18-О9,

л. Н 04 L 7-/02, 25.11.80 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Усредняющее устройство с блокировкой | 1981 |

|

SU978380A1 |

| Устройство для компенсации искажений типа "преобладание | 1987 |

|

SU1506581A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Фазовый дискриминатор | 1982 |

|

SU1027799A1 |

| Устройство для синхронизации приемника телеграфных сигналов | 1980 |

|

SU970715A1 |

Авторы

Даты

1982-11-30—Публикация

1981-05-04—Подача