Изобретение относится к запоминающим устройствам и может быть использрsaKCf в частности, для диагностики неисправностей блоков памяти, построенных в регистра сдвига.

Известно устройство для контроля блоков памяти, содержащее блок для формирования сигнала и неисправности), йяок управления и логические элементы :i|,

Однако на это устройство требуготсфг оолыане Аппаратурные затраты.

Наиболее близким по технической сути к изобретению является устройство для контроля блокбв памяти, содержащее блок управления, входы кото)рого подключены к эцхЬДам счетчика и, элемента И, первый вход которого сое;динен со входом устройства, и управ-, пяющие шины 2,

Однако в этом устройстве отсутствует возможность диагностирования неисправностей блоков памяти, собранных на базе триггеров, не имеюцшх сбросных и переключающихся входов, что су щественно сужает область применения устройства.

Современный уровень развития техники позволяет при разработке приборов и устройств промышленного назначения

2

применять элементы с большой степень интеграции. В качестве таких элементов июжно использовать, например, ин тегральную микросхему серии К1ИР144, которая при построении блока памяти в виде регистра сдвига позволяет сократит число корпусов в 21 раз (в одном корпусе элемента этой серии К.1ИР441 имеется 21 разряд) .

Несмотря на экономическую выгоду, применение таких элементов, из-за отсутствия Сбрасывающих и параллельных входов, а также ограниченного количества выходов (в одном корпусе элемента К1ИР441 - 3 выхода) , затрудня ет диагностику .Неисправностей аппаратуры и не позволяет применять для них известные диагностирующие устройства

Целью изобретения является расшире 1ие области применения устройства за счет возможности обнаружения неиспрабных разрядов блоков памяти, построенных на базе триггеров, не имеющих сбросных и переключающих входов, например, -многоразрядных регистров сдвига К1ИР144.

Для этого в устройстве введены элементы ИЛИ и дополнительный элемент И, выход которого подключен ко входу счетчика, один вход - в выхошу триггера и второму входу элемента, И, а другой вход дополнительного эле-UeHTa И и один из входов триггера cofe цинены с соответствуюаими управляющими шинами, другой вход триггера подключен к выходу элемента И, входы элементож ИЛИ соединены с соответствующими управляющими шинами, а их выходы - с выходами устройства.

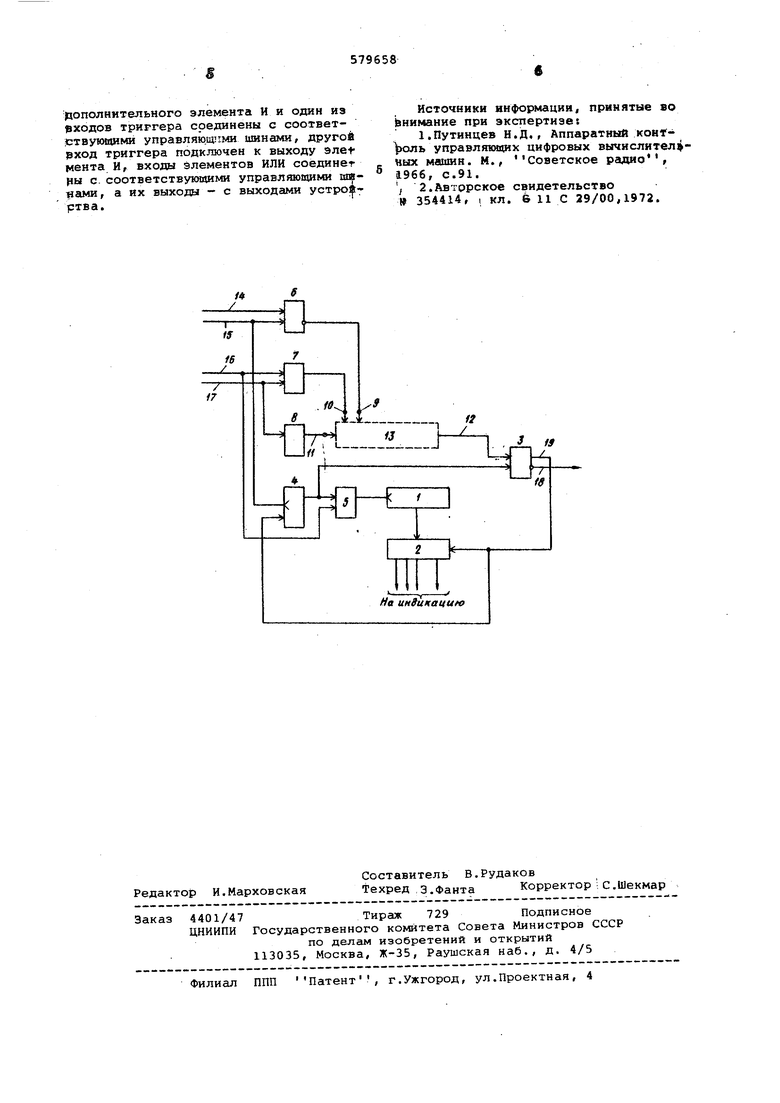

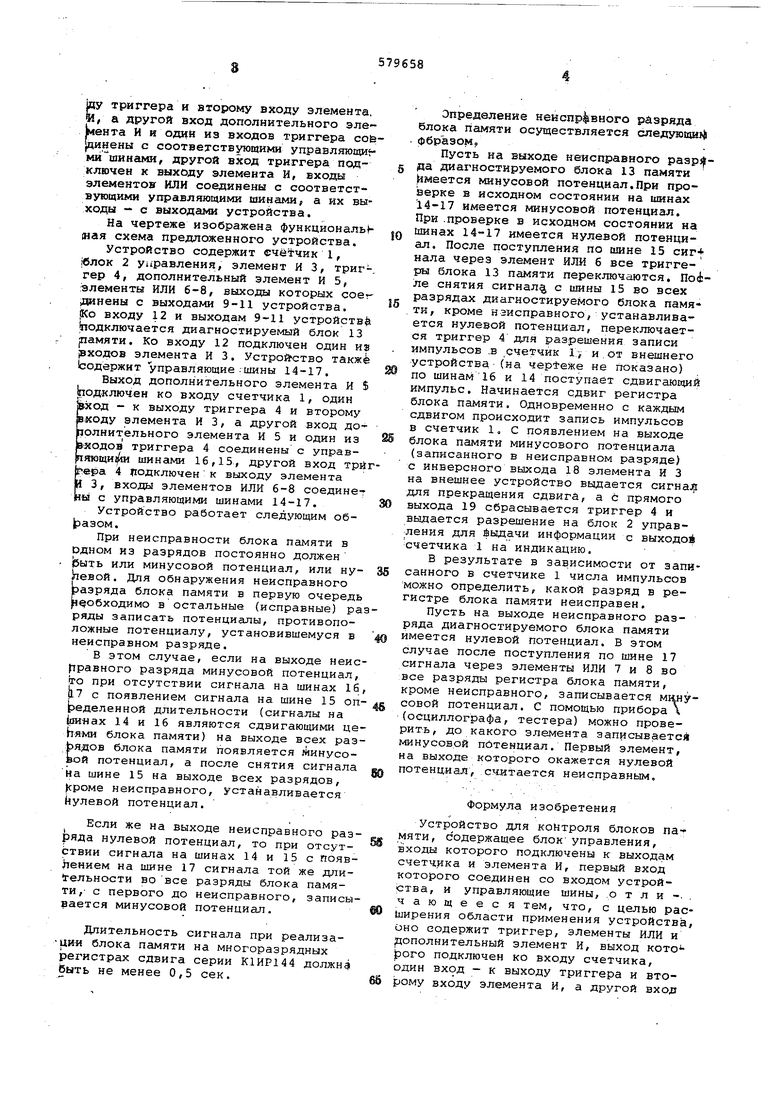

На чертеже изображена функциональЬ (ная схема предложенного устройства.

Устройство содержит счётчик 1, блок 2 управления, элемент И 3, тригЧ гер 4, дополнительный элемент И 5, элементы ИЛИ 6-8, выходы которых соег|Динены с выходами 9-11 устройства. jKo входу 12 и выходам 9-11 устройств подключается диагностируемый блок 13 рамяти. Ко входу 12 подключен один И8 |входов элемента И 3. Устройство также Ьодержит управляющие .-шины 14-17.

Выход дополнительного элемента И $ Ьод-ключен ко входу счетчика 1, один &ХОД - к выходу триггера 4 и второму входу элемента И 3, а другой вход до17олнительного элемента И 5 и один из в-ходов триггера 4 соединены с управчяющт т шинами 16,15, другой вход трйг рера 4 подключенк выходу элемента J 3, входы элементов ИЛИ 6-8 соединен ш с управляющими шинами 14-17.

Устройство работает следующим об)раэом.

При неисправности блока памяти в одном из разрядов постоянно должен Ьыть или минусовой потенциал, или нуЬевой. Для обнаружения неисправного разряда блока памяти в первую очередь обходимо в остальные (исправные) разряды записать потенциалы, противоположные потенциалу, установившемуся в неисправном разряде.

В этом случае, если на выходе неис 7равного разряда минусовой потенциал, то при отсутствии сигнала на шинах 16, 0.7 с появлением сигнала на шине 15 определенной длительности (сигналы на |аияах 14 и 16 являются сдвигающими цеЬями блока памяти) на выходе всех разЬядов блока памяти появляется Минусовой потенциал, а после снятия сигнала на шине 15 на выходе всех разрядов, (сроме неисправного, устанавливается йулевой потенциал.

Если же на выходе неисправного разряда нулевой потенциал, то при отсутствии сигнала на шинах 14 и 15 с появлением на шине 17 сигнала той же длительности во все разряды блока памяти,- с первого до неисправного, записырается минусовой потенциал.

Длительность сигнала при реализа11И-И блока памяти на многоразрядных регистрах сдвига серии К1ИР144 должн быть не менее 0,5 сек.

Определение неисправного разряда блока памяти осуществляется следующш . фбразом.

Пусть на выходе неисправного paapiffда диагностируемого блока 13 памяти Имеется минусовой потенциал,При проверке в исходном состоянии на шинах 14-17 имеется минусовой потенциал. При .проверке в исходном состоянии на шинах 14-17 имеется нулевой потенциал. После поступления по шине 15 сиг нала через элемент ИЛИ б все триггеры блока 13 памяти переключаются, noiле снятия сигналу с шины 15 во всех разрядах диагностируемого блока памяти, кроме иэнсправного, устанавливается нулевой потенциал, переключается триггер 4 для разрешения записи импульсов .в счетчик 1 и.от внешнего устройства(на чертеже не показано) по шинаМ16 и 14 поступает сдвигающий импульс. Начинается сдвиг регистра блока памяти. Одновременно с каждым сдвигом происходит запись импульсов в счетчик 1. С появлением на выходе блока памяти минусового потенциала (записанного в неисправном разряде) с инверсного выхода 18 элемента И 3 на внешнее устройство выдается сигна;|1 для прекращения сдвига, а с прямого выхода 19 сбрасывается триггер 4 и вьгдается разрешение на блок 2 управления для йыдачи информации с выходой Ъчетчика 1 на индикацию.

В результате в зависимости от записанного в счетчике 1 числа импульсов можно определить, какой разряд в регистре блока памяти неисправен.

Пусть на выходе неисправного разряда диагностируемого блока памяти имеется нулевой потенциал. В этом случае после поступления по шине 17 сигнала через элементы ИЛИ 7 и 8 во все разряды регистра блока памяти, кроме неисправного, записывается мкнусовой потенциал. С помощью прибора (осциллографа, тестера) можно проверить, до какого элемента записывается минусовой пбтенциал. Первый элемент, на выходе которого окажется нулевой потенциал,.считается неисправным,

Формула изобретения

Устройство для контроля блоков па-г мяти, содержащее блокуправления, входы которого подключены к выходам счетчика и элемента И, первый вход которого соединен со входом устройства, и управляющие шины, ,о т л и -. чающееся тем, что, с целью расширения области применения устройства Око содержит триггер, элементы ИЛИ и дополнительный элемент И, выход кото jporo подключен ко входу счетчика, один вход - к выходу триггера и второму входу элемента И, а другой вход

дополнительного элемента И и один из рходов триггера соединены с соответртвуюиими управляющ-чми шинами, другой эход триггера подключен к выходу элet мента И, входу элементов ИЛИ соединет цы с соответствующими управляющими , а их выходы - с выходами устро ртва.

Источники информации, принятые во внимание при экспертиза:

1.Путинцев Н.Д,, Аппаратный конг оль управляюпдах цифровых вычислителе ных машин. М., Советское радио , 1966, с.91.

, 2.Авторское свидетельство 354414, 1 кл. ё 11 С 29/00,1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления массы нефте-пРОдуКТОВ B РЕзЕРВуАРАХ | 1979 |

|

SU845159A1 |

| Интегрирующее устройство | 1975 |

|

SU553629A1 |

| Устройство контроля исправности счетчика | 1989 |

|

SU1667242A2 |

| Устройство для диагностики заболеваний | 1981 |

|

SU999064A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля передачи информации | 1981 |

|

SU1029207A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

Авторы

Даты

1977-11-05—Публикация

1975-11-19—Подача