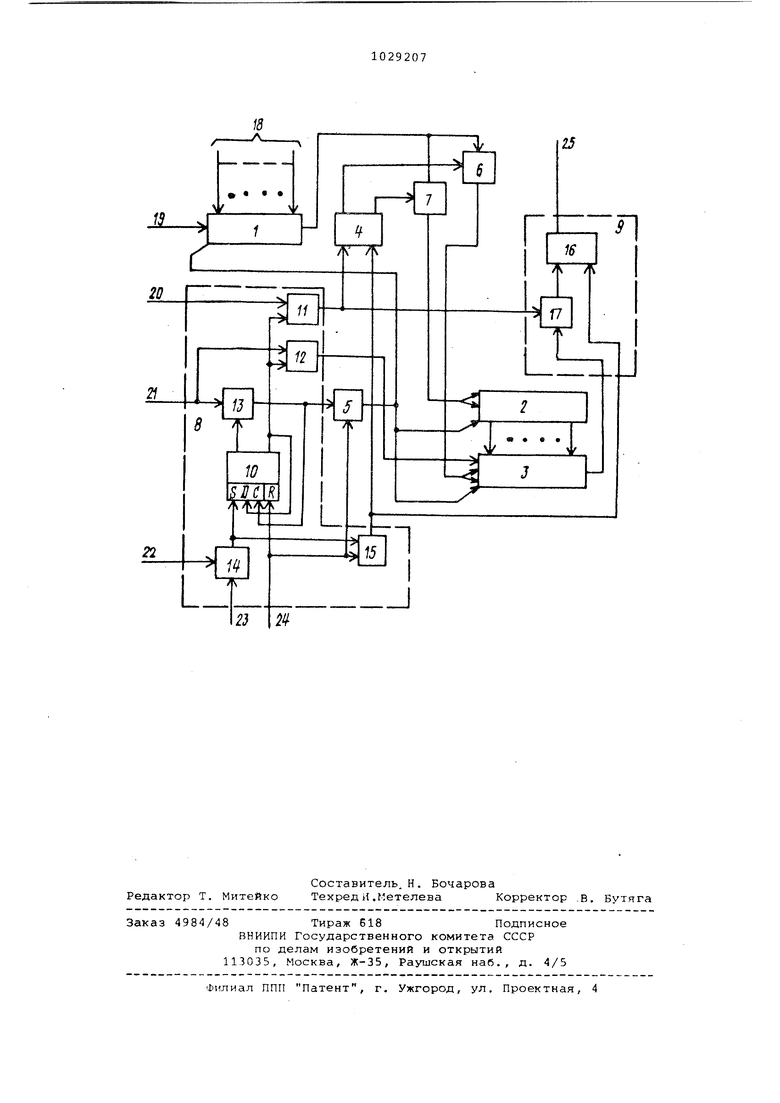

Изобретение относится к вычислительной технике, в частности для обнаружения ошибок и контроля запис и может быть использовано в устройствах отображения инфо1;)мации, в которых для создания режима регенерации символьной и графической информации необходимо постоянно с определенной частотой передавать двоичные коды информации между блоками устройства. Кроме того, изобретение может быть использовано в других устройствах, в которых производится передача массивов повторяющихся двоичных кодов, Известно устройство, осуществляющее контроль передачи информации суммированием всех информационных групп сообщения, как многоразрядных чисел , и сравнением контрольной с заранее известной .1. Недостатком такого устройства яв ляется то, что для его работы требуется несколько каналов связи. Наиболее близким техническим решением к предлагаемому является уст ройство для контроля передачи инфор мации, содержащее ячейку памяти, бл формирования сигнала ошибки, сумматор, триггер, сдвигающий двоичнодесятичный регистр, причем выходы ячейки памяти соединены с первой группой, входов одноразрядного двоич но-десятичного сумматора, выходы ко торого соединены с входами блока формирования сигнала ощибки и с входами младшего разряда сдвигающего двоично-десятичного регистра, выходы старшего разряда сдвигающего двоично-десятичного регистра соединены с второй группой входов одноразрядного десятично-двоичного сумматора, управляющий вход устройства и вход тактовых сигналов устройства соединены с соответствующими входами ячейки памяти и сдвигающего двоично-десятичного регистра 2. В связи с устройство контролирует двоично-десятичные коды и имеет только четыре информационных входа, оно не позволяет производить контроль двоичных кодов, содержащих более четырех разрядов, в результат чего область применения устройства ограничена. Кроме того, для работы устройства необходимо иметь контрол ную сумму, сформированную на передающем конце канала связи, что приводит к возможности искажения конт рольной суммы при передаче ее по к налу связи. Целью изобретения является расш рение области применения и повышение достоверности передаваемой информации. Указанная цель достигается тем, что в устройство для контроля пере дачи информации, содержащее блок памяти, первые и второй входы которого соединены информационными и управляющим входами устройства соответственно, блок формирования сигнала ошибки, выходкоторого соединен с выходом устройства, переключающий элемент и сумматор, введены узел блокировки, реверсивный счетчик,элементы И и ИЛИ, выход блока памяти соединен с объединенными первыми входами элементов И, выходы первого и второго элементов И соединены с первыми входами соответственно реверсивного счетчика и сумматора, выходы которого соединены с вторыми входами реверсивного счетчика, выход которого соединен с первым входом елока формирования сигнала ошибки, гервый - пятый входы .узла блокировки соединены с соответствующими управляющими входами устройства,пер11ЫЙ выход узла блокировки соединен с вторым входом блока формирования с:игнала ошибки и первым входом пере :лючающего элемента, выходы которого соединены с вторыми входами первого и второго элементов И, второй выход узла блокировки соединен с вторым 1 ходом переключающего элемента и третьим входом блока формирования с;игнала ошибки, третий выход узла блокировки соединен с третьим входом реверсивного счетчика, четвертый и пятый выходы узла блокировки соединены с входами элемента ИЛИ,выход которого соединен с третьим входом блока памяти, вторьм входом сумматора и четвертым входом реверсивного счетчика. Кроме того, узел блокировки содержит триггер, элементы И и ИЛИ, 1ЭЫХОД первого элемента ИЛИ соединен с первыми входами второго элемента 1-1ЛИ и триггера, первый выход кото1ЭОГО соединен с первым входом первого элемента И, выход которого сое,динен с вторым входом триггера, второй выход триггера соединен с первыми входами второго и третьего элементов И и третьим входом триггера, второй вход второго элемента И, объединенные вторые входы первого -i третьего элементов И, первый и второй входы первого элемента ИЛИ, объединенные четвертый вход триггера и второй вход второго элемента ИЛИ, подключены соответственно к первому - пятому входам узла блокировки, выходы второго элемента И, второго элемента ИЛИ, третьего элемента И, первого элемента И и первого элемента ИЛИ соединены соответственно с первым - пятым выходами узла блокировки. Блок формирования сигнала ошибки выполнен на триггере и элементе И, выход которого соединен с первым входом триггера, входы элемента И И второй вход триггера соединены со ветственно с первым - третьим входа ми блока формирования сигнала ошибки, выход триггера соединен с выходом блока формирования сигнала ошиб Введение указанных элементов и связей позволяет устройству осущест вить контроль при передаче повторяю щихся массивов информации, что особенно важно для устройств отображения при работе в режиме регенерации путем суммирования в счетчике всех логических 1, содержащихся в первом массиве информации, и сравнения полученной cyivsnH с количеством логи ческих 1, поступающих в последующих массивах информации. В устройстве предусмотрена блоки ровка контроля при замене в массиве информации одного или нескольких байтов (при вводе с пульта ввода данных) или при замене всего массива информации. Поэтому устройство позволяет принимать и контролироват не только двоично-десятичный код, а любые двоичные коды, изображаемые О и 1, что расширяет функци нальные возможности устройства по сравнению с прототипом. Кроме того, контольная сумма в предлагаемом устройстве вырабатывае ся на приемном конце канала связи, что исключает ее искажение при пере даче по каналам связи, На чертеже изображена функционал ная схема предлагаемого устройства. Устройство для контроля передачи информации содержит блок 1 памяти, представляющий собой п-разрядный двоичный сдвигающий регистр, ш-разрядный сумматор 2 (представляющий собой двоичньлй счетчик) , т-разрядны двоичный реверсивный счетчик 3, пер ключающий элемент 4 (на триггере), элемент ИЛИ 5, элементы И б и 7,узе 8 блокировки, блок 9 формирования сигнала ошибки. Узел 8 блокировки состоит из три гера 10, элементов И 11, 12 и 13 и элементов ИЛИ 14 и 15. Элемент ИЛИ 14 BKJrao4eH в узел 8 блокировки для создания возможности блокирования работы устрюйства разными источника ми, например пультом ввода данных и устройством обмена (не показаны), Блок 9 формирования сигнала ошибки включает в себя триггер 16 и элемейт И 17. Устройство п-двоичных информационных входов 18, шесть входов управления 19 - 24 и один выход 25 для вывода сигнала ошибки. Устройство работает следугадим образом. По сигналу Начало работы, пода ваемому на управляющий вход 24, устанавливаются в О блок 1 памяти сумматор 2, реверсивный счетчик 3 и триггеры 4, 10 и 16. После этого в блок 1 памяти по входам 18 поступает двоичный код информации,которыйсд вигается из блока 1 памяти при поступлении импульсов сдвига на управлякяций вход 19. С выхода блока 1 памяти последовательный двоичный код поступает на вход элемента И 7, открытого по второму входу триггером 4, а с выхода элемента И 7 ксзд поступает на вход счетчика 2, где происходит суммирование всех логических 1 информационного слова. Аналогичная операция происходит при записи в блок 1 памяти всех информационных слов и в результате в счетчике 2 оказывается записанной сумма логических 1, срдержащихся во всем массиве информа- ции. По окончании массива информации в узел 8 блокировки по входу 20 поступает сигнал Конец массива, который проходит через элемент И 11, открытый по второму входу разрешением с триггера 10, и устанавливает в 1 триггер 4. На единичный вход триггера 16 сигнал с выхода элемента И 11 не проходит, так как элемент И 17 закрыт по второму входу отрицательным потенциалом с выхода Обратный перенос реверсивного счетчика 3. Далее в узел 8 по входу 21 поступает сигнал Запись, который проходит через элемент И 12, открытый по второму входу триггером 10 и производит запись в реверсивный счетчик 3 информации, поступающей по установочтзам рходам на счетчика 2, Начинается повторная передача массива информации (отображение нового кадра информации в устройствах отображения), т.е. в блок 1 памяти опять записываются информационные слова и последовательно сдвигаются на выход. Но теперь двоичный код с выхода блока 1 памяти проходит через элемент И 6, открытый сигналом триггера 4 и поступает на вход обратного счета реверсивного счетчика 3. Если весь тракт прохождения кодов работает правильно, то число 1, записанное в реверсивный счетчик 3 при повторной передаче массива информации, должно быть равно числу единиц, записанных при передаче первого массива. При выполнении этого условия в реверсивном счетчике 3 установится нулевой код, при котором на выходе Обратный перенос реверсивного счет,чика 3 появляется отрицательный потенциал, поступающий на вход элемента И 17. При этом сигнал Конец массива , поступающий в узел 8 по входу 20 после окончания передачи массива, через элемент И 17 не проходит,так как по второму входу элемент . И 17 заперт отрицательным потенциалом с выхода Обратный перенос реверсивного счетчика 3 и триггер 16 не устанавливается в 1, т.е. не вырабатывается сигнал Неисправность.

Аналогично работа устройства происходит и при передаче последующих массивов информации при равенстве числа 1, записанных в реверсивный счетчик 3 и принятых при передаче очередного массива информации.

Если же число 1, записанное в реверсивном счетчике 3, не совпадает с числом 1, принятым в очередном массиве информации, то по окончании приема массива реверсивный счетчик 3 не будет находиться в нулевом состоянии и соответственно на его выходе Обратный перенос появится положительный потенциал. В результате этого импульс Конец массива пройдет через элемент И 11, открытый по второму входу триггером 10 и опросив элемент И 17, открытый по второму входу положительным потенциалом с выхода реверсивного счетчика 3, установит в 1 триггер 16, который вьщаст на выход 25 Неисправность.

При частичной замене информации в передаваемом массиве или при замене массива информации очередной передаваемр й массив, а следовательно и количество логических в нем, отличаются от количества 1, записанных в реверсивном счетчике 3 и устройство выдает сигнал Неисправность. Для того, чтобы избежать это , в устройство введен узел 8 блокировки.

Работа узла 8 блокировки в составе устройства происходит следующи образом.

При изменении какого-либо информционного слова в массиве информации

в устройство по входу 22 n.ociynatJT сигнал Замена 1, который проходит чгфез элемент ИЛИ 14 и поступает на S-вход триггера 10, устанавливая его в 1, а также устанавливает в О триггеры 4 и 16. При этом закрывается элемент И 11, сигнал Конец масск;за не проходит на опрос элемента И 17 и триггер 16 не выдает сигнал Неисправность Затем в устройство ПС входу 21 поступает сигнал Запксь, который проходит через элемент И 13, открытый по второму входу триггером 10/ и через элемент ИЛИ 5 поступает на обнуление блока 1 па:мяти, счетчика-сул1матора 2 и реверсивного счетчика 3, а задний фрон сигнала устанавливает в О триггер 10, Далее начинается передача измененного массива информации и в счетчи 2 записывается новая сумма логических 1. При поступлении в устройство по входу 23 сигнала Замена 2 работа устройства происходит аналогично работе устройства по сигналу Замена 1.

Осуществление контроля многоразрядных двоичных кодов путем су / мировапия логических 1 в повторяющихся массивах информации позволяет пp ;мeнить предлагаемое устройство для: контроля цепи знакогенератор вид:;еоблок , использующихся в настоящее время устройств отображения, обеспечиваемая достоверность контроля не ниже 1 ошибки на 12x10 бит. Ведение контроля указанного канала одновременно с работой устройства отображения позволяет автоматически контролировать до 90% его блоков, что в конечном итоге повышает достоверность выдаваемой (отображаемой) информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1646055A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для ввода информации | 1980 |

|

SU947848A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для регистрации простоев оборудования | 1986 |

|

SU1374262A1 |

| Устройство для контроля раствора валков прокатного стана | 1983 |

|

SU1088832A1 |

| Устройство для программного регулирования температры | 1986 |

|

SU1374194A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ, содержащее блок памяти, первые и второй входы которого соединены с информационными и управляющим входами устройства соответственно, блок формирования сигнала ошибки, выход которого соединен с выходом устройства, переключающий элемент и сумматор, отличающееся тем, что, с целью расширения области применения и повышения достоверности передаваемой информации, в устройствовведены узел блокировки, реверсивный счетчик, элементы И и ИЛИ, выход блока памяти соединен с объединенными первыми входами элементов И, выходы первого и второго : лементов И соединены с первыми входами соответственно реверсивного счетчика и сумматора, выходы которого соединены с вторыми входами реверсивного счетчика, выход которого соединен с первым входом блока формирования сигнала ошибки, первый - пятый входы узла блокировки соединены с соответствующими управляющими входами устройства, первый выход узла блокировки соединен с вторым входом блока формирования сигнала ошибки и первым входом переключающего элемента, выходы которого соединены с вторыми входами перЁого и второго элементов И, второй выход узла блокировки соединен с вторым входом переключающего элемента и третьим входом блока формирования сигнала ошибки, третий выход узла блокировки соединен с третьим входом реверсивного счетчика, четвертый и пятый выходы узла блокировки соединены с входами эле мента ИЛИ, выход которого соединен с третьим входом блока памяти, вторьви входсж сумматора и четвертым входом реверсивного счетчика. 2. Устройство по п,1, отличающееся тем, что узел блокирювки содержит триггер, элементы И и ИЛИ, выход первого элемента ИЛИ. соединен с первыми входами второго элемента ИЛИ и триггера, первый выход которого соединен с первым входом первого элемента И, выход которого соединен с вторым входом триггера, второй выход триггера соединен с первыми входами второго и третьего элементов И и третьим jxoдом триггера, второй вход второго элемента И, объединенные вторые входы первого и третьего элементов И, первый и второй входы первого элемента ИЛИ, объединенные четвертый ю вход триггера и второй вход второго элемента ИЛИ подключены соответственно к первому - .пятому входам узла блокировки, выходы второго элемента И, второго элемента ИЛИ, третьего элемента И, первого элемента И и первого элемента ИЛИ сое- динены соответственно с первым пятым выходами узла блокировки. 3. Устройство по п.1, о т л и ч аю ад е е с я тем, что блок формирования сигнала ошибки выполнен на триггере и элементе И, выход которого соединен с первым входом триггера, входы элемента И и второй вход триггера соединены соответственно-с первым - третьим входами блока формирования сигнала ошибки, выход триггера соединен с выходом блока формирования сигнала ошибки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контрольное устройство приема информации | 1972 |

|

SU469130A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для контроля передачи информации в двоично-десятичном коде между блоками цифровой вычислительной машины | 1975 |

|

SU581471A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-07-15—Публикация

1981-10-15—Подача