Изобретение относится к вычислительной технике и может быть использовано в структурах систем обработки данных ЭВМ общего и специального назначения ,

Цель изобретения - упрощение устройства, заключающееся в сокращении оборудования, затрагиваемого на хранение диагностических констант, а также получение функционально полной проверки.

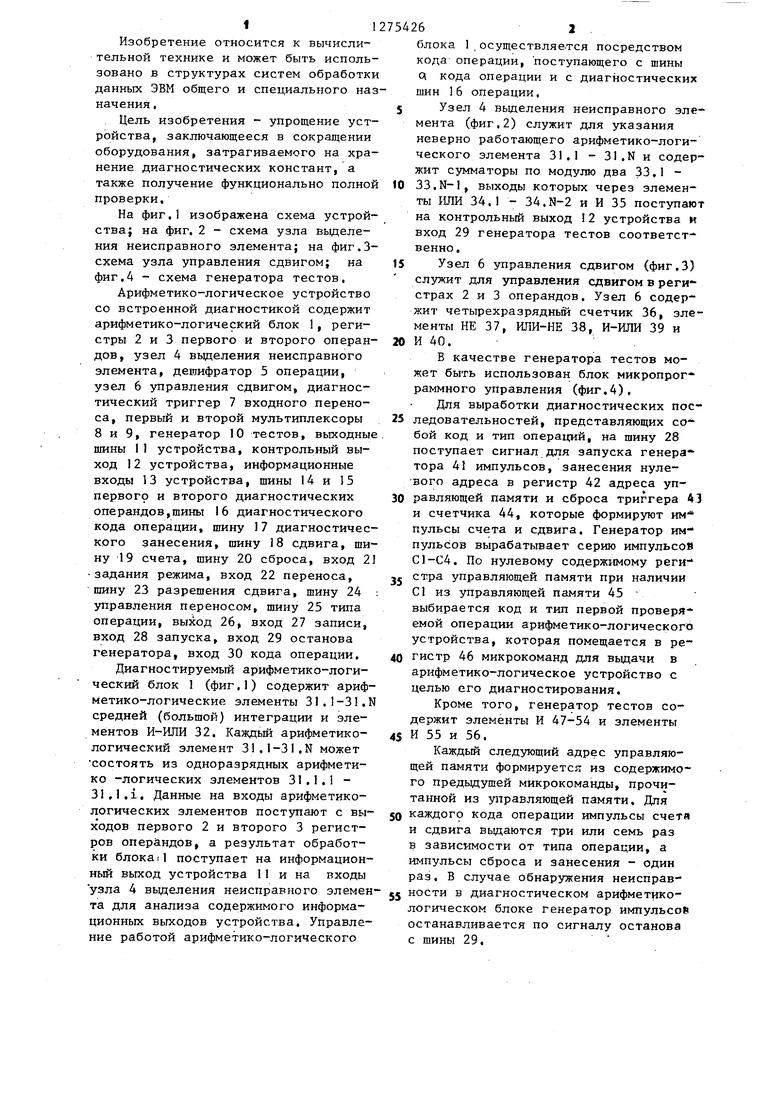

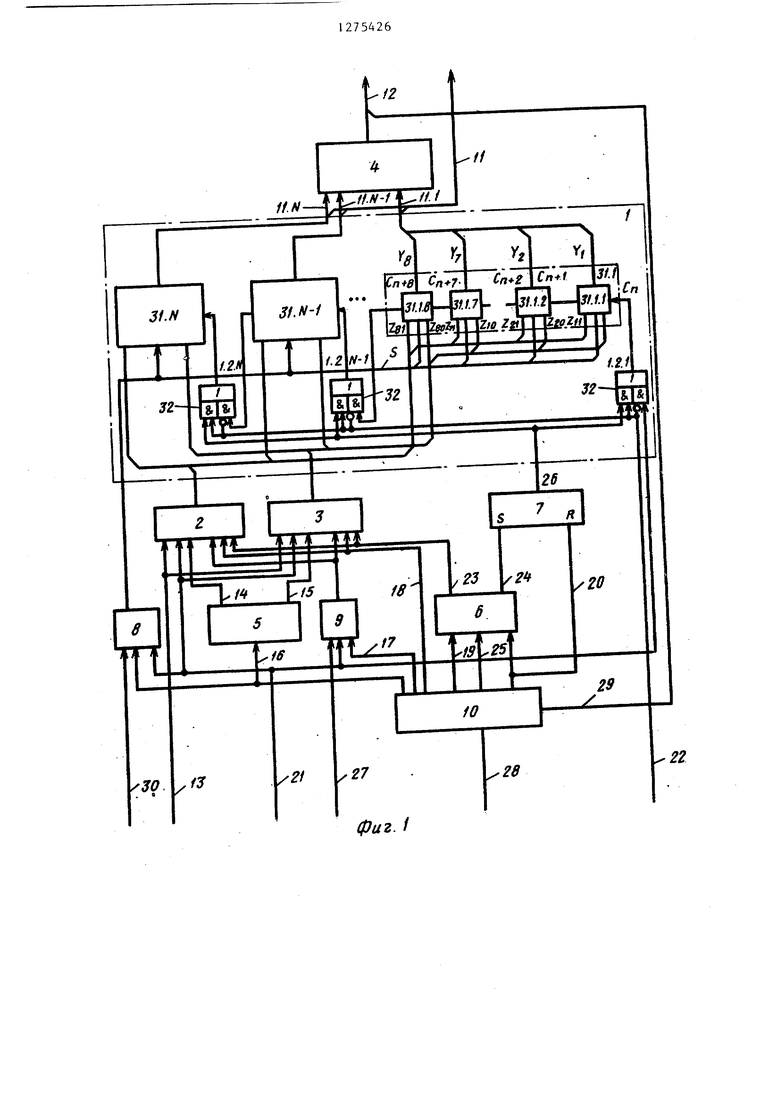

На фиг.1 изображена схема устройства; на фиг. 2 - схема узла выделения неисправного злемента; на фиг.Зсхема узла управления сдвигом; на фиг.4 - схема генератора тестов,

Арифметико-логическое устройство со встроенной диагностикой содержит арифметико-логический блок 1, регистры 2 и 3 первого и второго операндов, узел 4 вьщеления неисправного элемента, дешифратор 5 операции, узел 6 управления сдвигом, диагностический триггер 7 входного переноса, первый и второй мультиплексоры 8 и 9, генератор 10 тестов, выходные шины I1 устройства, контрольный выход 12 устройства, информационные входы 13 устройства, шины 14 и 15 первого и второго диагностических oneрандов,шины 16 диагностического кода операции, шину 17 диагностического занесения, шину 18 сдвига, шину 19 счета, шину 20 сброса, вход 2 задания режима, вход 22 переноса, шину 23 разрешения сдвига, шину 24 управления переносом, шину 25 типа операции, выход 26, вход 27 записи, вход 28 запуска, вход 29 останова генератора, вход 30 кода операции.

Диагностируемый арифметико-логический блок 1 (фиг.1) содержит арифметико-логические элементы 31.1-3I.N средней (большой) интеграции и элементов И-ИЛИ 32. Каждый арифметикологический элемент 31.1-31.N может состоять из одноразрядных арифметико -логических элементов 31.1.1 31.1.1. Данные на входы арифметикологических элементов поступают с выходов первого 2 и второго 3 регистров опера.ндов, а результат обработки блокаil поступает на информационный выход устройства 11 и на входы узла 4 выделения неисправного элемента для анализа содержимого информационных выходов устройства. Управление работой арифметико-логического

блока 1 осуществляе-тся посредством кода операции, поступающего с шины с кода операции и с диагностических шин 16 операции.

Узел 4 выделения неисправного элемента (фиг,2) служит для указания неверно работающего арифметико-логического элемента 31.1 - 31.N и содержит сумматоры по модулю два 33.1 33,N-1, выходы которых через элементы ИЛИ 34.1 - 34.N-2 и И 35 поступают на контрольньй выход 12 устройства м вход 29 генератора тестов соответственно.

Узел 6 управления сдвигом (фиг.З) служит для управления сдвигом в регистрах 2 и 3 операндов. Узел 6 содер жит четырехразрядньш счетчик 36, элементы НЕ 37, ИЛИ-НЕ 38, И-ИЛИ 39 и

И 40.

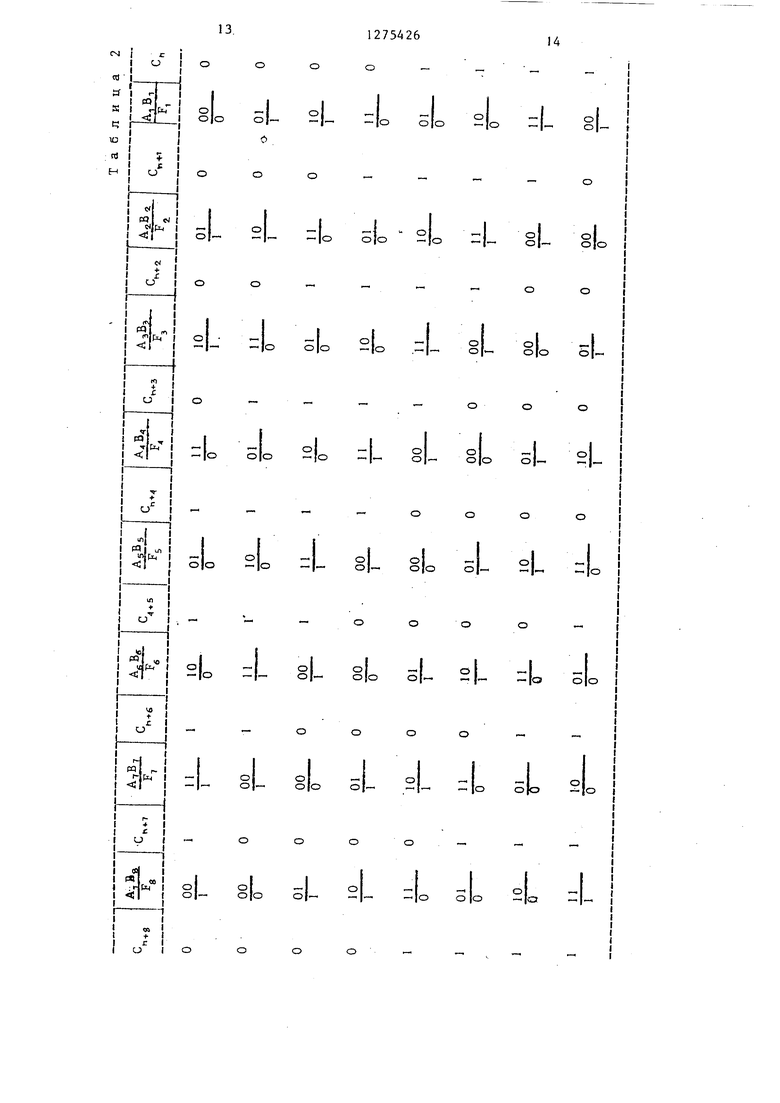

В качестве генератора тестов может быть использован блок микропрограммного управления (фиг.4).

Для выработки диагностических последовательностей, представляющих код и тип операций, на шину 28 поступает сигнал для запуска генера тора 41 импульсов, занесения нулевого адреса в регистр 42 адреса управляющей памяти и сброса триггера 43 и счетчика 44, которые формируют им пульсы счета и сдвига. Генератор импульсов вырабатывает серию импульсов С1-С4. По нулевому содержимому реги

стра управляющей памяти при наличии С1 из управляющей памяти 45 выбирается код и тип первой проверя емой операции арифметико-логического устройства, которая помещается в регистр 46 микрокоманд для выдачи в арифметико-логическое устройство с целью его диагностирования.

Кроме того, генератор тестов содержит элементы И 47-54 и элементы

И 55 и 56.

Каждый следующий адрес управляющей памяти формируется из содержимого предыдущей микрокоманды, прочитанной из управляющей памяти. Для

каждог9 кода операции импульсы счет и сдвига выдаются три или семь раз в зависимости от типа операции, а импульсы сброса и занесения - один раз. В случае обнаружения неисправности в диагностическом арифметикологическом блоке генератор импульсов останавливается по сигналу останова с шины 29.

Полный диагностический тест для

проверки любой схемы должен содержать максимально 2 диагностических последовательностей, где п - количество входов схемы. Для полной проверки арифметико-логического элемента, приведенного на фиг,1, необходимо задать диагностических последовательностей для каждой арифметической операции, так как элемент имеет три информационных входа для приема двух одноразрядных операндов и переноса из предыдущего разряда и

J

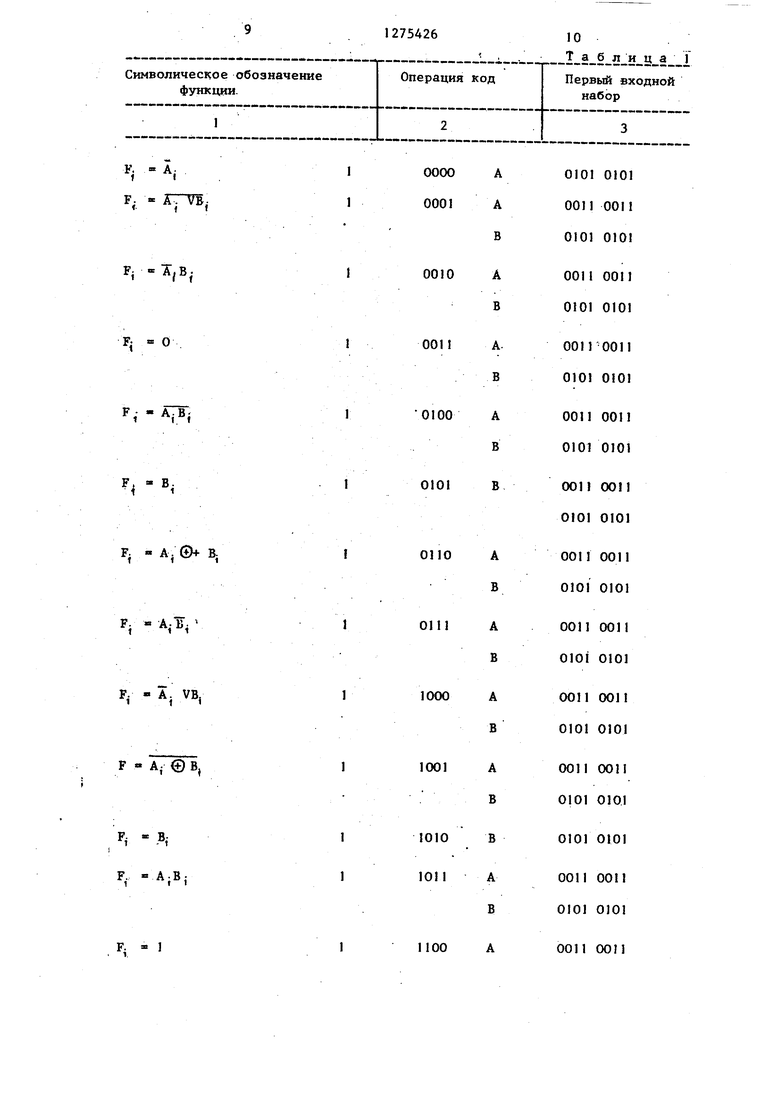

диагностические последовательности для каждой логической операции, так как значение переноса для них безразлично. Элемент также имеет пять управляющих входов, которые позволяют задать 16 арифметических и 16 логических операций. Следовательно, необходимо задать 16x8+16x4 192 диагностические последовательности для полной проверки°элемента и хранить их в генераторе тестов. Для арифметических операций первоначально занесенная последовательность, а затем 7 раз сдвинутая дает 8 различных последовательностей, аналогично для логических операций получаем 4 различные последовательности для каждой операции. Первоначальная последовательность генерируется в дешифраторе 5 из кода и типа операции согласно табл. 1 .

Устройство работает следующим образом.

Каждый арифметико-логический элемент 31 . 1-31 ,N блока 1 (фиг.О может быть представленВ виде одноразряд-. ных арифметико-логических элементов, на входы которых поступают информационные разряды 7. .д и Z из регистров 2 и 3 операндов. Входной перенос Х; подключается к выходному-переносу X;., предьщущего элемента через элементы И-ИЛИ 32,1 - 32,N, а выходы

YJ арифметико-логических элементов

подключены к информационному выходу 11 устройства. Операция (сложение, вычитание, логическая операция И и т.д.), которую должен вьшолнить арифметико-логический элемент 31,1 (31,N) поступает на вход Vj с шин 16 операции ,

Полный контролирующий тест для одноразрядного арифметико-логического элемента 31,1,1 при выполнении

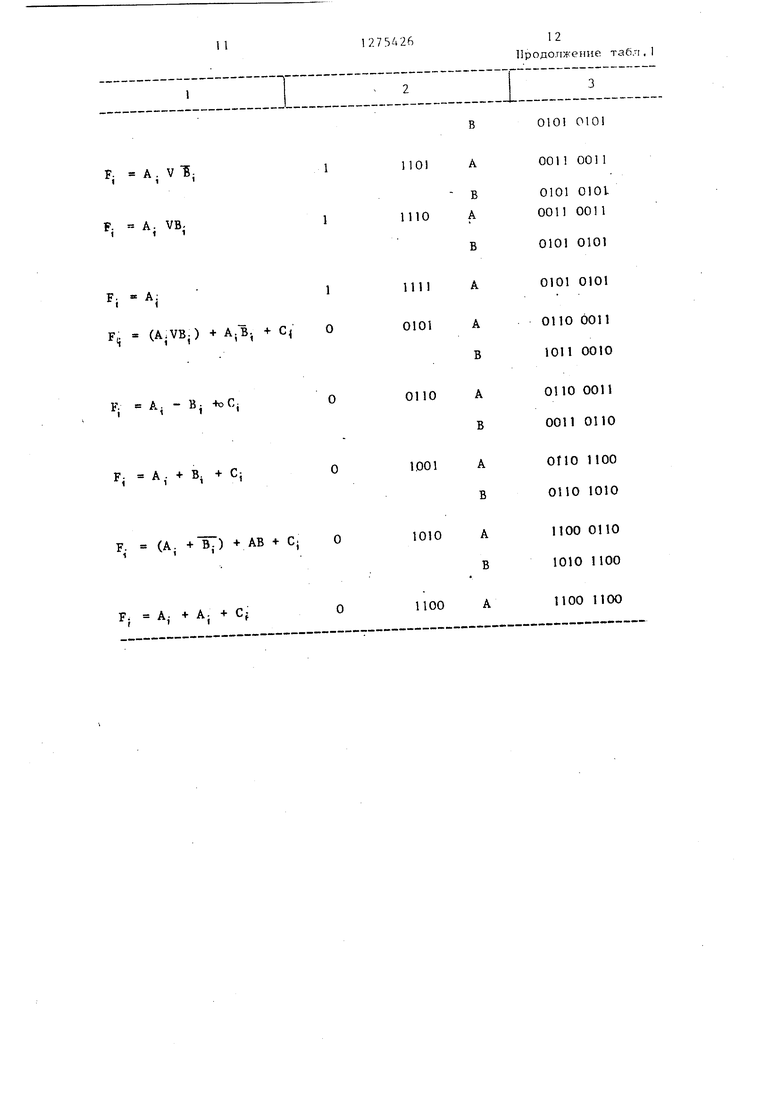

функции сложения представляет собой последовательность длины L 2 8, В этом случае производится перебор всех возможных значений входов (Z , Z. , X.) и .следовательно, этот тест является полным. Если арифметико-логический блок разбить на байты (восемь информационных разрядов), то независимо от количества арифметикологических элементов в блоке 1 количество тестов для всего диагностируемого блока остается постоянным и равным восьми, Б табл,2 приведен полный контролирующий тест для одного байта,

Исходн.ая константа (Zg-, ; Z j;

7 7 У 7 7 -.7 7 61t 60 Bl 60 i 40

Z,o. 2,1 V Z,o ) посJl 30 21

Z

тупает на входы каждого байта блока 1 с выходов регистров 2 и 3 операндов , а входной перенос С поступает с выхода диагностического триггера 7 через элементы И-ИПИ 321. Входная информация в режиме диагностики сдви гается восемь раз в регистрах 2 и 3 операндов. Следовательно, независимо от количества байтов н диагностируемом режиме каждый элемент 31,1,1 арифметико-логического блока 1 подвергается полному контролирующему тесту.

Рассмотрим операцию логического сложения Z. V Z. ,

Полный контролирующий тест для одноразрядного элемента представляет собой тест длиной L 2 4,

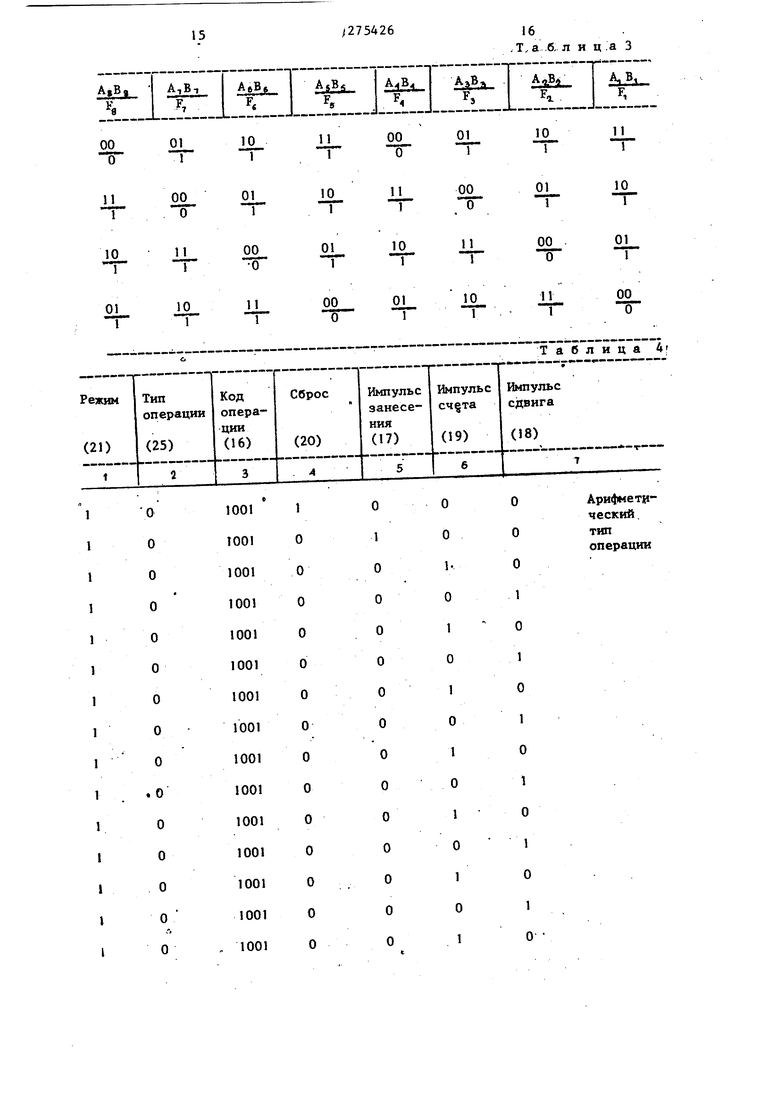

Таким образом, независимо от количества арифметико-логических элементов в арифметико-логическом блоке 1 количество тестов остается постоянным и равным четырем, так как при каждом циклическом сдвиге исходной информации в регистрах операндов 2 и 3 производится полный входных наборов, В табл,3 приведен полньй контролирующий тест для одного байта.

Аналогичным образом можно рассмотреть каждую функцию, вьтолкяемую диагностируемым блоком 1, и привести константы для этих функций,

Арифметико-логическое устройство с встроенной диагностикой работает в двух режимах: рабочем и диагностическом,

В рабочем режиме на вход 21 режима присутствует низкий потенциал, запрещающий выдачу диагностических

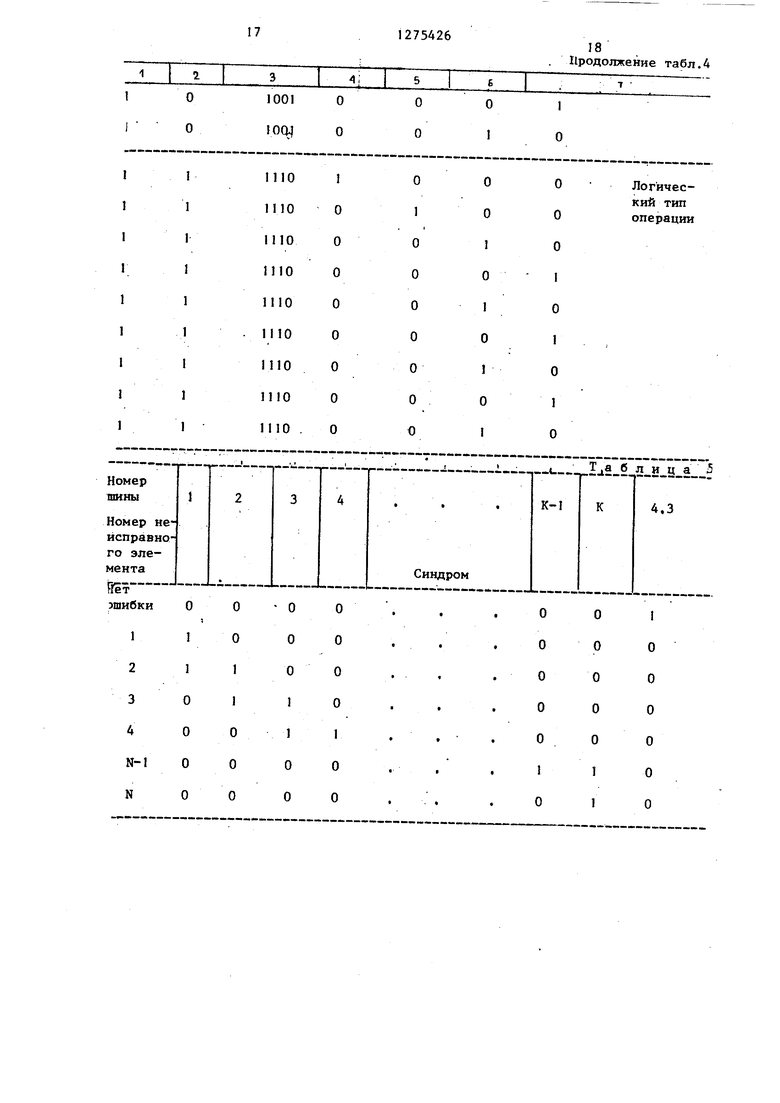

информационных и управляющих сигналов на входы арифметико-логического устройства и разрешающий вьщачу кода операций с входа а кода операции и занесение операндов с входа 13 oneрандов по сигналу на входе 27 зане сения в регистры 2 первого и 3 второго операндов. Сигнал переноса в рабочем режиме поступает в устройство с входа 22, Арифметико-логическое устройство выполняет операцию, указанную кодом операции, и результат выдает на выходы 11 устройства, В рабочемрежиме работа устройства может контролироваться различными способами (дублирование, предсказание контрольного разряда результата) При обнаружении неисправности схемамы контроля работа устройства останавливается и запускается диагностический режим определения места неисправности, С этой целью не входе 21 режима устанавливается высокий потенциал, и на входе 28 запуска поступает сигнал для запуска генератора 10 тестов, На выходе генератора 10 тестов формируются диагностические последовательности сигналов, представленные в табл,4,

На шину 20 сброса выдается импуль сброса для гашения счетчика 36 сдвигов в узле 6 зшравления сдвигом и триггера 7 диагностического переноса На шине 16 диагностического кода операции поступает код операции, а на шину 25 типа операции потенциал, определяющий а1: ифметическую или логическую операции. Для арифметической операции узел 6 управления сдвигом вьшолняет семь сдвигов, после третьего сдвига сигнал переноса меняет свое значение из О в 1,

Для логической операции выполняются три сдвига и значение переноса безразлично. Диагностические операнды формируются в дешифраторе 5 операции из кода операции согласно описанному вьше методу построения тесгов, Диагностические операнды из дешифратора 5 заносятся через шины 14 и 15 первого и второго диагностических операндов на вход арифметико-логического блока по сигналу на шине 17 диагностического занесения в регистры 2 и 3 соответственно.Устройство выполняет указанную операцию над каждым байтом информации и результат постзтает в

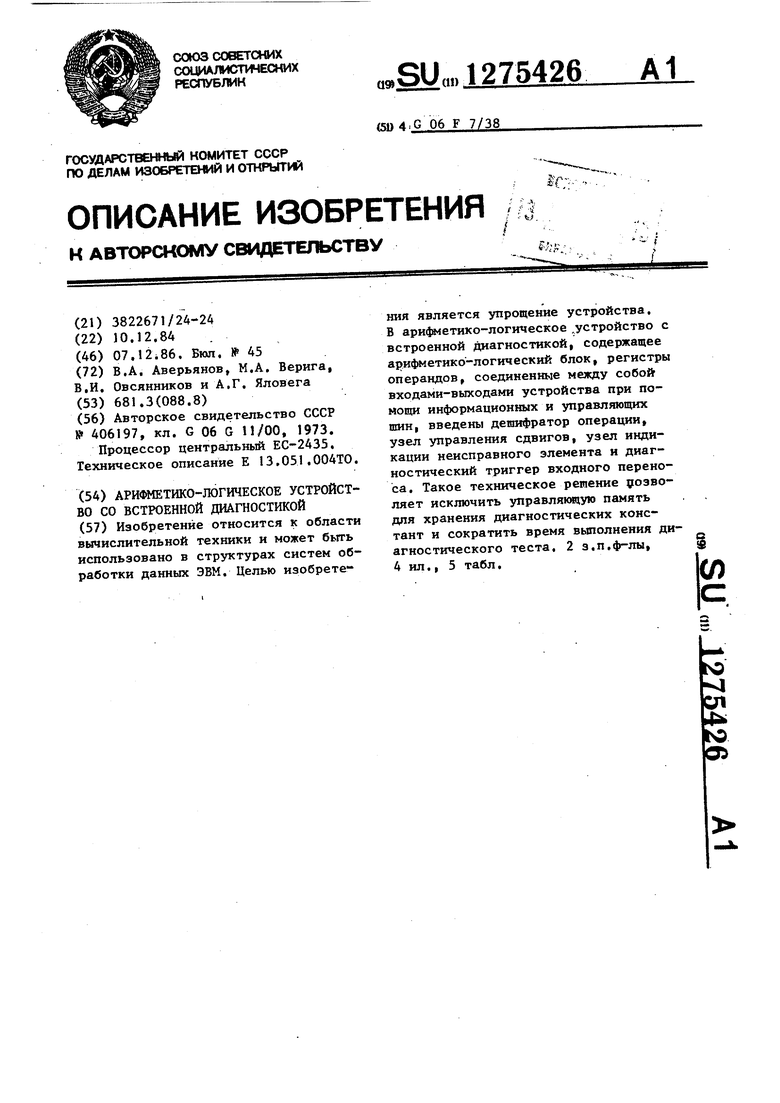

узел 4, где побайтно сравнивается на сумматорах 33.1-- 33,N-1 по модулю два. Результат сравнения поступает на элементы ИЛИ 34,1 - 34,N-2 и элемент И 35, которые формируют синдромы на выходах 12, В табл, 5 приведены синдромы.

После занесения операндов в регистры 2 и 3 вьщается импульс счета на шину 19, который устанавливает счетчик 36 в единичное состояние, и через элемент И-ИЛИ 39 на шине сдвига устанавливает потенциал разрешения сдвига. За импульсом счета следует сигнал сдвига по шине 18 сигнала сдвига, В регистрах 2 и 3 операнды сдвигаются на один разряд. Устройство описанным вьш1е способом выполняет операцию над сдвинутым операндом. Для арифметических операций сдвиг выполняется семь раз, Однако по четвертому импульсу счета триггер 7 диад ностического переноса устанавливает.ся в единичное состояние, и перенос в процессе работы со сдвинутыми операндами меняет свое значение из О в 1, Для логических операций сдвиг выполняется три раза. Перед занесением нового кода операций выполняется сброс счетчика 36 и триггера7 диагностического переноса. По новому коду операции вырабатываются новые операнды в дешифраторе 5 и процедура, описанная вьшзе, повторяется. Количество диагностических кодов операций определяется количеством функций арифметико-логического устройства, которое оно выполняет врабочем режиме,

Формула изобретения

1, Арифметико-логическое устройство со встроенной диагностикой, содержащее ари(я4етико-логический блок, первый и второй мультиплексоры, генератор тестов, регистры первого и второго операндов, выходы которых подключены к первой и второй группам информационных входов арифметико-логическогй блока, выходы которого подключены к информационному выходу устройства, информационные входы которого подключены к первым информационным входам регистров первого и второго операндов, вход кода операции устройства подключен к первому информационному входу первого мультиплексора, выходы которого подключены к входу кода операции арифметико-логического блока, вход задания режима работы устройства подключен к входу управления режимом арифметико-логического блока, к входам управления режимом регистров первого и второго операндов, к управляющим входам первого и второго мультиплексоров, вход переноса устройства подключен к первому входу переноса арифметико-логического блока, вход Строб записи устройства подключен к первому информационному входу второго мультиплексора, выход которого подключен к входу разрешения записи регистров первого и второго операндов, а вход пуска устройства подключен к входу пуска генератора тестов, отличающееся тем, что, с целью упрощения устройства, оно содержит дешифратор операций, узел управления сдвигом, узел вбщеления неисправного элемента и диагностический триггер входного переноса, установочный.вход которого подключен к первому выходу узла управления сдвигом, второй выход которого подключен к входам разрешения сдвига регистров первого и второго операндов, а первый, второй и третий входы узла управления сдвигом подключены к выходам счета, типа операции и сброса генератора тестов, информационный выход которого подключен к второму информационному входу первого мультиплексора и входу дешифратора операции, выходы которого подключены к вторым информационным входам регистров пер вого и второго операндов, а входы сдвига регистров первого и второго операндов подключены к выходу сдвига генераторов тестов, выход занесения которого подключен к второму информационному входу второго мультиплексора, вход останова генератора тестов подключен к вьпсоду узла вьщеления неисправного элемента, входы которого подключены к информационным

выходам арифметико-логического блока второй вход переноса которого подключен к выходу диагностического триггера входного переноса, вход сброса диагностического триггера входного переноса подключен к выходу сброса генератора тестов, группа выходов узла выделения неисправного элемента подключена к контрольному выходу yctpoйcтвa. . 2,Устройство по п.1, о т л и ч аю щ е е с я тем, что узел, управ л ения сдвигом содержит счетчик, элемент ИЛИ-НЕ, элемент НЕ, элемент И и элемент И-ИЛИ, причем первый и третий входы узла подключены соответственно к входам разрешения и сброса счетчика, разрядные выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И-ИЛИ, второй и третий входы которого соединены с выходами третьего и четвертого разрядов счетчика, второй вход узла соединен с четвертым входом элемента ИИЛИ и через элемент НЕ - с его пятым входом и первым входом элемента И, второй вход которого соединен с выходом третьего разряда счетчика, выход первого разряда которого соединен с его счетным входом, выходы элемента И и элемента И-ИЛИ являются соответственно первым и вторым выходами узла,

3.Устройство по П.1, отличающееся тем, что узел выделения неисправного элемента содержит группу сумматоров по.модулю два, группу элементов ИЛИ, элемент И, причем входы узла попарно подключены к входам сумматоров по модулю два груп пы, прямые выходы которых попарноv подключены к входам.элемейтов ИЛИ группы, выходы которых образуют группу выходов узла, инверсные выходы сумматоров по модулю два группы

соединены с входами элемента И, выход которого является выходом узла.

F. «A,

F, . гГТБ,.

F, -A,B,.

F 0

F . . А.В;

F - В.

F. - А. &+ Bj

F. - А.В,

F,. - А. VB,

F А,- © В,

Fi -В,F. - A.Bi

F. - I

A A В

0101 0101 ООП ООП 0101 0101

A В

001 1 ООП

0010 0101 0101

ООП ООП

ООП

A. В 0101 0101

ООП ООП

0100

А В 0101 0101

ООП ООП

0101

в 0101 0101

001I 0011

А В

опо 0101 0101

ООП ООП

011

А В 0101 0101

ООП ООП

1000

А В 0101 0101

ООП ООП

А В

1001 0101 0101

0101 0101

в

ООП ООП

А В 0101 0101

ООП ООП

1100

АгЬ.

АэВа

. F-, J

11 Т

jO

01

0

T1

1

10

01

00

1 1

1

т

01

00„

11

10

1

о 11

1

00,

10

01

о

11

10

01

г

1

10

1 1

00

о 11

01

00

-о

11 00

10

Т о

т

и ц а Af

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для сопряжения | 1980 |

|

SU877520A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

Изобретение относится к области вычислительной техники и может быть использовано в структурах систем обработки данных ЭВМ. Целью изобретения является упрощение устройства. В арифметико-логическое „устройство с встроенной диагностикой, содержащее арифметико-логический блок, регистры операндов, соединенные между собой входами-выходами устройства при помощи информационных и управляющих шин, введены дешифратор операции, узел управления сдвигов, узел индикации неисправного элемента и диагностический триггер входного переноса. Такое техническое решение цозволяет исключить управлякяаую память дпя хранения диагностических констант и сократить время выполнения диагностического теста. 2 з.п.ф-лы, 4 ил., 5 табл. (Л

1

1001

о 1001

о 1001

о 1001

о 1001

о 1001

о 1001

О

о 1001

О

о 1001

О

о 1001 О

о 1001

о о о о о

о 1001

о 1001

о 1001

о . 1001

Арифметио о ческий . тип операции

о

1

о

1

о

1

о

1

о 1

о 1 о

1001

О О

О О 100)

I

1110 1110

о о о о о о о о 1110 1110 1110 1110 1110 П 10 1110 .

о о 1 1 о о

о 1 1

1 1

О О О

о о о

1

о

О 1

1 О

О О

о о 1

о о о I

Логический тип операции

о 1

о 1

о 1

о 1 о

о 1

о о о о 1 1

О О О О

о о о о о о

1 о

фаг. I

С...

ЗЗ.

I

:

VII-N

//-/V-/;

12

55

1 t

J С

//-J

U//-/

//-

Фиг. 2

23 Z

35 irhn

Фиг.5

Сброс зон

Счет С88иг

28 Фиг.

| УСТРОЙСТВО для ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ В ЛОГИЧЕСКИХ СХЕМАХ | 0 |

|

SU406197A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Реле | 1925 |

|

SU2435A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1986-12-07—Публикация

1984-12-10—Подача