1

Изобретение относится к импульсной технике.

Известен логический элемент Запрет, содержащий первый и второй усилительные каскады, включающие выходные п-р-п транзисторы и блок запрета. Эмиттеры входных транзисторов усилительного блока и блока запрета подключены к соответствующим входам. Подача сигнала запрета во втором усилительном каскаде осуществляется на один эмиттер двухэмиттерного транзистора. Два выхода усилителя, соединенные, с коллекторами первых ВЫХОДНЕЛХ п-р-п транзисторов и через диоды - с эмиттерами вторых выходных п-р-п транзисторов, инвертированы друг относительно друга l.

Наиболее близким к йредлагаемому является элемент, содержащий два входных транзистора, база одного из которых через диод и резистор соединен;а с источником питания и. через разделительный диод с источником запрещающего сигнсша, база второго транзистора через диод и резистор соединена с источником питания и через второй разделительный диод с источником ин-. формационного сигнала, и инвертирующий транзистор 2.

Данный элемент потребляет значительную мощность,

Целью ,изобретения является уменьшение потребляемой мощности.

Поставленная цель достигается тем что в логическкй элемент, содержащий два входных транзистора, база одного из которых через диод и резистор соединена с источником питания и через разделительный диод и источником запрещающего сигнала, база второго транзистора через диод и резистор соединена с источником питания и через второй разделительный диод с источником информационного сигнала, и инвертирующий транзистор, введены четыре дополнительных диода и резистор, причем первый дополнительный диод включен между эмиттером первого транзистора и точкой соединения резистора и диода подключенного к базе второго транзистора, эмиттер которого через разнополярно включенные второй и третий допол }ительные диоды соединен с базой инвертирующего транзистора, при этом точка соединения упомянутых второго и третьего дополнительных транзк-::торов соединена через дополнительный резистор с источником питания и чераз

Четвертый дополнительный диод с эмиттером первого входного транзистора.

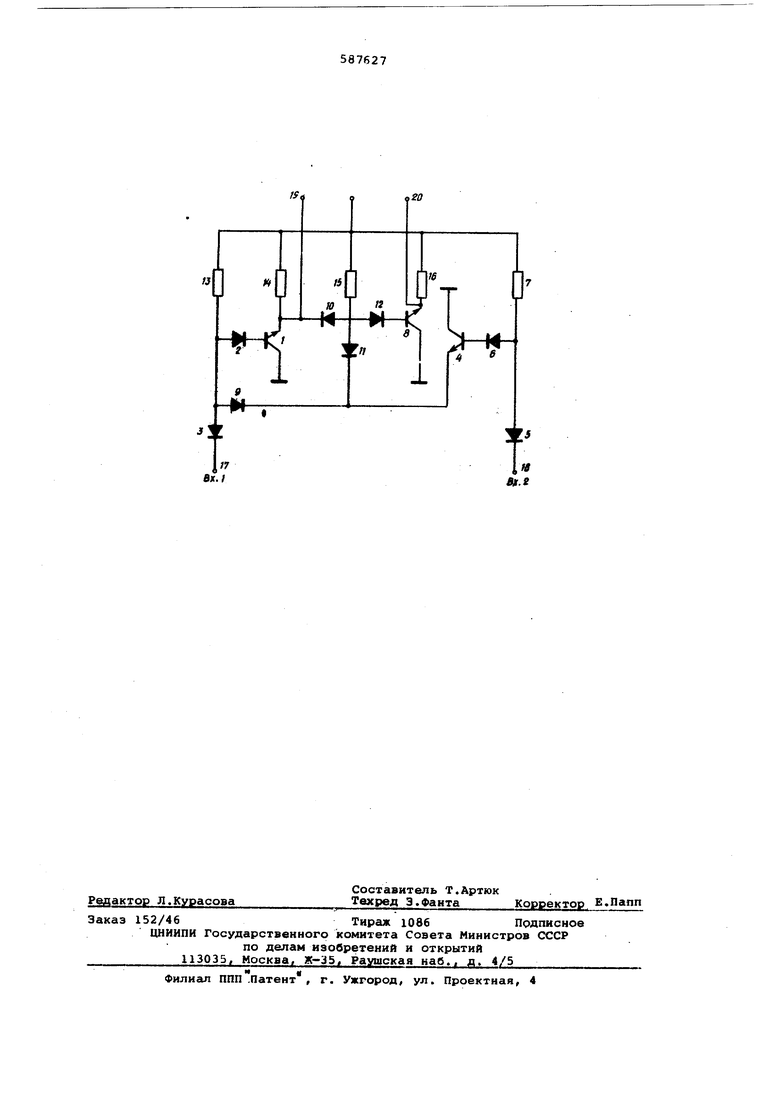

Принципиальная электрическая схема элемента приведена на чертеже.

Элемент содержит входной транзистор 1, разделительные диоды, диод 2, входной диод 3, входной транзистор 4, разделительный диод 5, диод 6, резистор 7, инвертирующий транзистор 8, диоды 9-12 и резисторы 13-16, На вход 17 подан информационный сигнаш, на вход 18 - запрещающий сигнал.

Выходные сигналы снимоиотся с выходов 19, 20.

|1ринцип работы заключается в следующем.

Пусть ко входу 18 приложен низкий потенциал. От шины питания через резистор 7, диод 5 ток замыкается на общую шину. Транзистор 4 запирается, обесточивает цепи диодов 9 и 11, подготаиливая схему к прохождению сигналов по входу 17. При поступлении на вход 17 высокого потенциала, диод 3 запирается, и ток от шины питания через резистор 13, диод 2 смещает в прямом направлении переход база-коллектор транзистора 1, который переходит в насыщенное состояние. Низкий потенциал с эмиттера транзистора 1 поступает на выход 19 усилителя. Ток, протекающий через резистор 15, ответвляется в цепь: диод 10, открытый транзистор 1, а цепь диода 11 обесточена запертш- транзистором 4. Отсутствие тока через диод 12 и переход база-коллектор транзистора 8 обеспечивает запирание последнего. Высокий потенциаш с эмиттера транзистора 8 поступает на выход 20 усилителя.

При поступлении на вход 17 низкого потенциала, ток через резистор 13, диод 3 замыкается на общую шину. Отсутствие базового тока через диод 2 , запирает транзистор 1, и высокий потенциал эмиттера передается на выход 19. Диод 10 заперт, и ток от шины пиТания через резистор 15, диод 12 смещает в прямом направлении переход, база-коллектор транзистора 8 и отпирает его. Низкий потенциал эмитт а насыщенного транзистора 8 поступает на выход 20.

Таким образом, при наличии низкого потенциала на входе 18 ипоступлении по входу 17 высокого уровня на выходе 19 устанавливается низкий потенциа а на выходе 20 - высокий.

Подача по входу 17 низкого потенциала обеспечивает высокий уровень на выходе 19 и низкий потенциал на выходе 20.

Запрещение прохождения сигнала через усилитель реализуется подачей высокого потенциала на вход 18. В этом случае ток через резистор 7 и диод 6 отпирает транзистор 4. По цепи резистор 13, диод 9, открытый транзистор 4, а также по цепи резистор 15, диод 11 и открытый транзистор 4 ток проходит . на общую шину. Транзисторы 1 и 8 запираются, и высокий потенаиал эмиттеров поступает на выходы 19 и 20. Это состояние сохраняется при подаче любого сигнала на вход 17 усилителя.

Импульсный усилитель обладает низкой потребляемой мощностью вследствие инверсного включения транзисторов.

Упрощение принципиальной схемы (уменьшение числа схемных элементов), уменьшение числа резисторов, и диодов, имеющих общую точку соединения, транзисторов с общей коллекторной областью а также слаботочный режим работы транзисторов способствуют повышению надежности устройству.

Формула изобретения

Логический элемент Запрет, содержащий два входных транзистора, база одного из которых чарез диод и резистор соединена с источником питания и через разделительный диод с источником запрещающего сигнала, база второго транзистора через диод и pe3HCTO соединена с источником питания и через второй разделительный диод с источником информационного сигнгша, и инвертирующий транзистор, отличающийся тем, что с целью уменьшения потребляемой мощности, в него введены четыре дополнительных диода и резитор, причем первый дополнительный диод включен между эмиттером первого транзистора и точкой соединения резистора и диода, подключенного к базе второго транзистора, эмиттер, которого через разнополярно включенные второй и третий дополнительные диоды соединен с базой инвертирующего транзистора, при этом точка соединени упомянутых второго и третьего дополнительных транзисторов соединена через дополнительный резистор с источником питания и через четвертый дополнительный диод с Э1101ттером первого входного транзистора.

Источники информации, принятые во внимание при экспертизе:

1.Микросхемы интегральные,

сер.134-2, ЧТУ-21.93.487.000,ТУ. 1973

2.Texas anetr umentft,l971,SN 5449

f

„го

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое устройство | 1977 |

|

SU738171A1 |

| Импульсный стабилизатор напряжения | 1985 |

|

SU1325440A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ЗВУКОВОЙ ЧАСТОТЫ | 1993 |

|

RU2115224C1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU693434A1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Формирователь импульсов | 1977 |

|

SU692071A2 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ЗАПРЕТ» | 1972 |

|

SU423251A1 |

| Коммутатор | 1974 |

|

SU497730A1 |

D

ю

. Г

.«

Авторы

Даты

1978-01-05—Публикация

1976-01-14—Подача