(54) ЛОгаЧЕСКОЕ УСТГОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Инвертор | 1976 |

|

SU661804A1 |

| Трехвходовой дешифратор | 1974 |

|

SU517155A1 |

| Буферное логическое ТТЛ устройство | 1981 |

|

SU993477A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

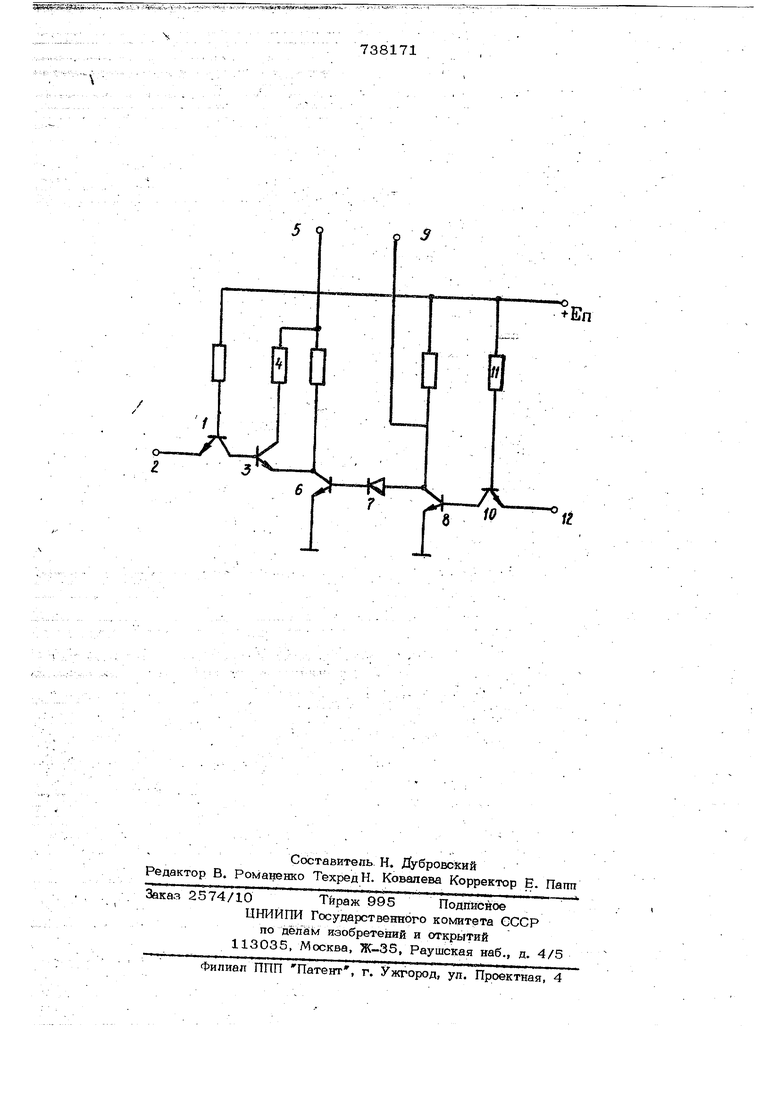

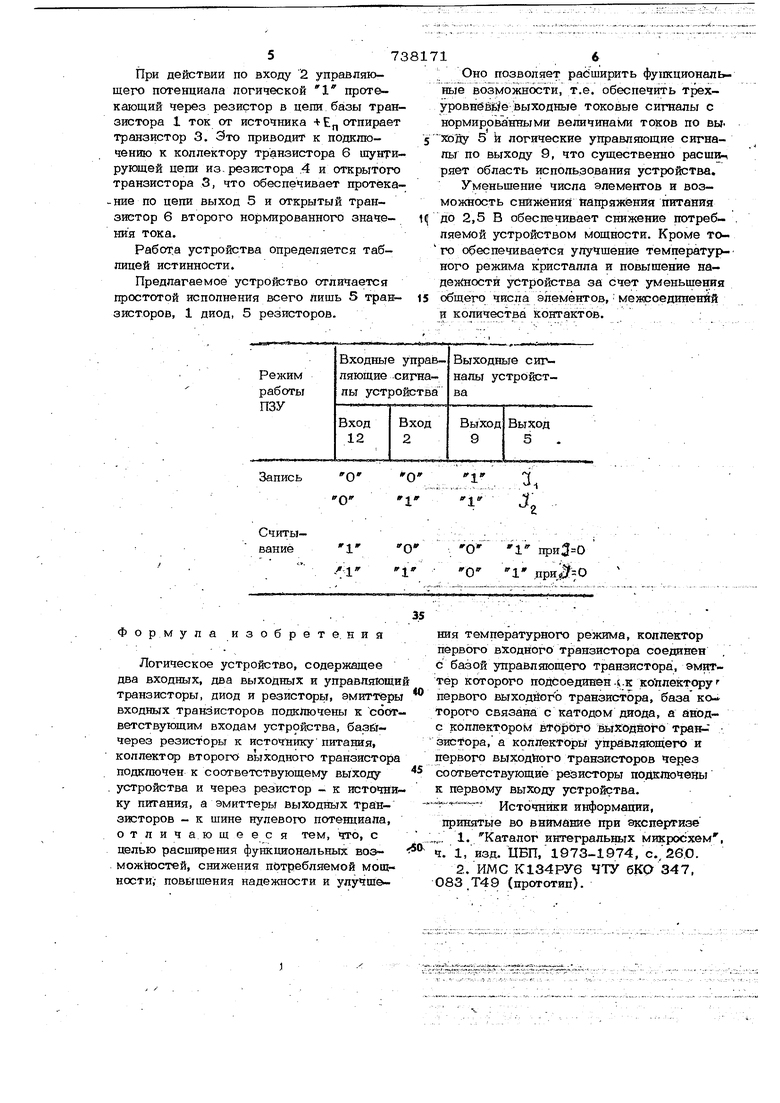

Изобретение относится к айтбматикв; телемеханике и вычислительной технике и может быть использовано в узлах стыковки логических и управляющих токовых сигналов, в частности как блок схемы управления постоянного репрог ам мйруемого запоминающего устройствас матрицей запоминающих эл:ементбв на основе халькогенидных стекол. Известно логическое устройство (фор мирователь разрядной записи-усилйтель воспроизведения), содержащее входные выходные и управляющие транзисторы, диоды и резисторы l . Это логическое устройство имеет вес ма сложное построение, значительные потребляемую мощность и напряжение питания, снизить которые не предотавля- ется возможным. . Наиболее близким к предлагаемому по технической сущности являё я логическое устройство, содержащее две входные цепи, два выходных двухэмиттерных транзистора, один из э fиттepoв которых яодйл бчен к базе того же транзистора и через соответствующий резистор - к ши|й-Ё йёШГб 1ШВДШЖ,у не-посредственно к шине нупевого потенпиала. Коллекторы выходных транзисторов соедйгнё1йа. с Соответствующими выходами устройства и через соответствующие резисторы - с шийой питания. Два упГ авляющйх транзистора Takike выпопйеньг двуХэмиттерными, причем один из э ятттеров каждого из этих транзисторов подключен к базе того тке транзистора и собтВ1этствующий резистор к ипше нулевого потенаиапа, а втор6й непосрёдственно шине нулевого потенаиапа. Коллекторы управ/Ггдаадйс: равзйстбрбв объединены и через резистор подключены к шине питания, а так:1кё через дйод в йрямом включении - к базе первого выходного транзистора . - Недостатки известного устройства закЛ{бча бтся 6 епоясйости конструктивного исполнения, в том, что логические сигналы на выходах устройства действуют в 75 противофазе, что ограничивает возможности применения его в ПЗУ, а также в значительной площади, занимаемой на кристаппе в интегральном исполнении (вследствие включения в устройство многоэмиттерных транзисторов и шести диодов).. Цель изобретения - расширение функцио.нальных возможностей устройства, сни жение потребляемой к ощности, повышение надежности и улучшение температурного режима. Поставленная цель достигается тем, что в логическом устройстве, содбржащем два входных, два выходных и управляющий транзисторы, диод и резисторы, эмиттеры входных транзисторов подключегш к соответствующим входам устройства, базы- через резисторы к источнику питания, коллектор второго выходного транзистора подключен к соответствующему выходу устройства и через резистор - к источнику питания, а эмиттеры выходных транзисторов - к шине нулевого потенциала, коллектор первого входного транзистора соединен с базой управляющего транзистора, эмиттер которого подсоединен к коллектору первого в ходного транзистора, база которого связана с катодом диода, а анод - с коллек тором второго выходного транзистора, а коллекторы управляющего и первого вйходного транзисторов через соотйетствуто щиё резисторы подключены к первому вы ХОД5- устройства. На чертеже схематически представлено логическое устройство. Эмиттер первого входногб транзистора 1 Подключен к первому входу 2 устройства. База транзистора 1 через резистор соединена с источником питания t-Ef, . Коллектор транзистора 1 связан с/базой управляющего транзистора 3. Ко лектор транзистора 3 через резистор 4 подсоединен к первому выходу 5 уст|рЬйства. Эмиттер транзистора 3 подключен к коллектору лервого выходного транзистора б и через резисторк первому выходу 5 Устройства. Эк даттер транзистора б соединен с шиной нулевого потенциала а база его - с катодом диода 7, анод которого связан с коллектором второго выходного транзистора 8, qo вторым выходом 9 устройства и через резистор с источником питания. Эмиттер транзистора 10 подсоединен ко второму входу устройства 12, Таким образом, устройство содержит два управляющих входа (2- информаиион 14 ных сигналов логического О или 1 и 12 - выбора режима), подача сигналов на которые обеспечивает управление состояниями двух выходов (9 - с действующими потенциалами сигналов логического О или 1, 5 - с действующими трехуровневыми токовыми сигналами (отсутствие тока, нормированный ток малой величины, нормированный ток большой величины). Это позволяет выходными потенциальными сигналами логического О или 1 с выхода 9 управлять режимом работы блоков схемы управления путем разрешения или запрета работы блоков, а токовые выходные сигналы с выхода 5 использовать для записи информации в ячейки матрицы памяти. Логическое устройство работает следующим образом. Пусть ко входу 12 приложен потенциал логической 1 и по эмиттеру транзисторы 10 действует втекающий ток. От источника питания + через резистор Неоткрытый переход база-коллектор транзистора 10 в базу транзистора 8 протекает ток. Транзистор 8 открывается и пропускает ток от -(-ЕП , На выходе 9 устанавливается потенциал логического О, который прикладывается также к аноду диода 7. Транзистор б заперт из-за от-, сутствия базового тока, через транзистор б и выход 5 ток не протекает, независимо от состояния транзистора 3 и сигнала по входу 2. При действии по входу 12 сигнала логического О ток от источника питания tEf, через резистор 11 и переход базаэмиттер транзистора 10 замыкается на источник входного сигнала логического О. Отсутствие базового тока транзистора 8 запирает транзистор, и по выходу 9 устанавливается потенциаллогической I, который через диод 7 отпирает пере... ход база-эмиттер транзистора &, Через открытый транзистор б образуется цепь для протекания токового сигнала по выходу Sv Нориирование величины этого токового сигнала производится управляющим сигналом по входу 2, Пусть ко входу 2 приложен потенциал логического О. Ток через переход база-эмиттер транзистора 1 замыкается на источник входного сигнала. Транзистор 3 заперт, .и цепь из резистора 4 и закрытого транзистора 3 не шунтирует резистор в коллекторе транзистора б. Величина тока, протекающего по цепи выход 5 и открытый Тра нзистор б, нормируется величиной резисторов в коллекторе транзистора б.

При действии по входу 2 управляющего потенциала логической I протекающий через резистор в цепи базы транзистора 1 ток от источника tE отпирает транзистор 3. Это приводит к пощслючению к коллектору транзистора 6 шунтирующей цепи из. резистора .4 и открытого транзистора 3, что обеспечивает протёка-ние по цепи выход 5 и открытый транзистор 6 второго нормированного значения тока.

Работа устройства определяется таблицей истинности.

Предлагаемое устройство отличается простотой исполнения всего лишь 5 транзисторов, 1 диод, 5 резисторов. Формула изобрете. ния Логическое устройство, содержащее два входных, два выходных и управляющи транзисторы, диод и резисторы, эмиттеры входных транзисторов подключены к соответствующим входам устройства, ба;зйчерез резисторы к источнику питания, коллектор второго выходного транзистора подключен к соответствующему выходу устройства и через резистор - к источнику питания, а эмиттеры выходных транзисторов - к шине нулевого потенциала, отличающееся тем, что, с целью расширения функциональных возможностей, снижения пЬтребляемой мощности,- повышения надежности и улучщ& Оно позволяет расширить функциональные возможности, т.е. обеспечить трехypoBHeeiS/e выходные токовые сигналы с нормированы ми величинами токов по вызаэду 5 k логические управляющие сигналы по выходу 9, что существенно расшв-, ряет область использования устройства. Уменьшение числа элементов и возможность снижения напряжения питания до 2,5 В обеспечивает снижение потреб.ляемой устройством мощности. Кроме того обеспечивается улучшение температурного режима Кристалла и повышение надехностй устройства за счет уменьшения общего числа элементов, мезнсоединенйй и количества контактов. ния температурного режима, коллектор первого входного транзистора соединен с базой управляющего транзистора, эмнттер которого подсоединен л.к коллектору первого выходйого транзистора, база которого связана с катодом диода, а анодс коллектором вто|)ого выходного трав- зисТора, а коллекторы управляющего и первого выходйого транзисторов через соответствующие ре;зисторы подключейы к первому выходу з зтройства. Источники информации, прин5ггые во внимание при экспертизе .„ 1. Каталог интегральных MmcpocxeM, ч. 1, изд. ЦБП, 1973-1974, с.,26.0. 2. ИМС К134РУ6 ЧТУ бКО 347, (прототип).

J, jri 0 BO

738171

Бп

K|

Авторы

Даты

1980-05-30—Публикация

1977-12-30—Подача