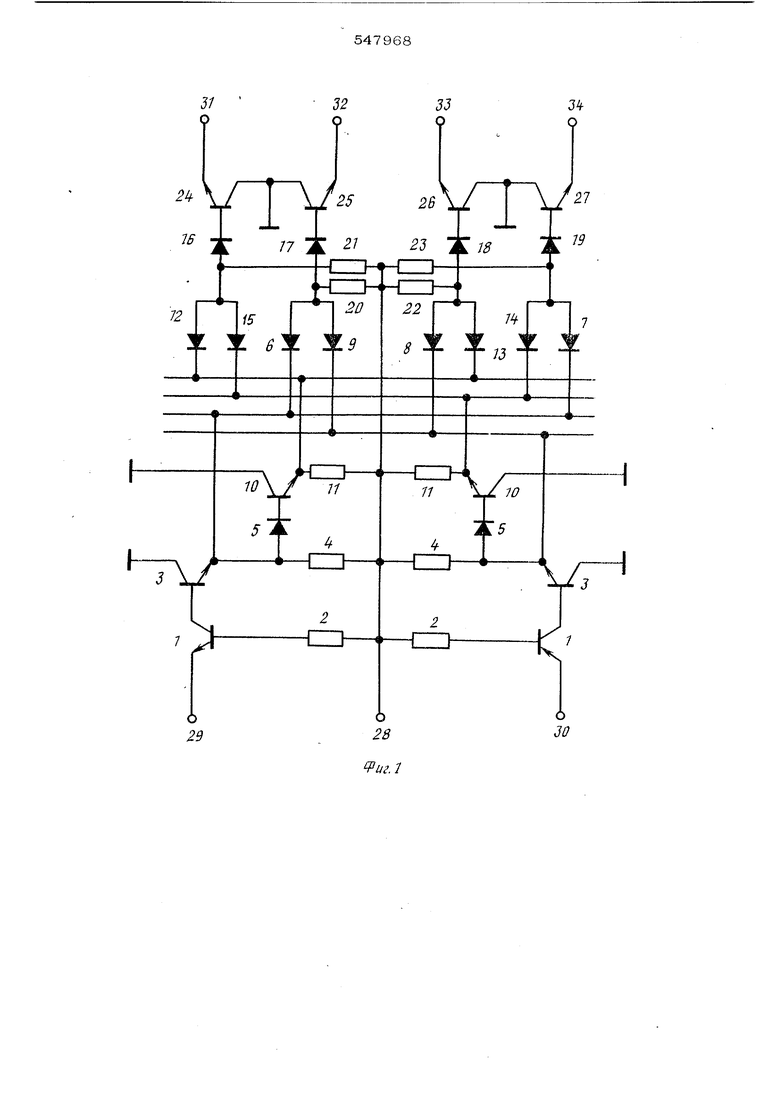

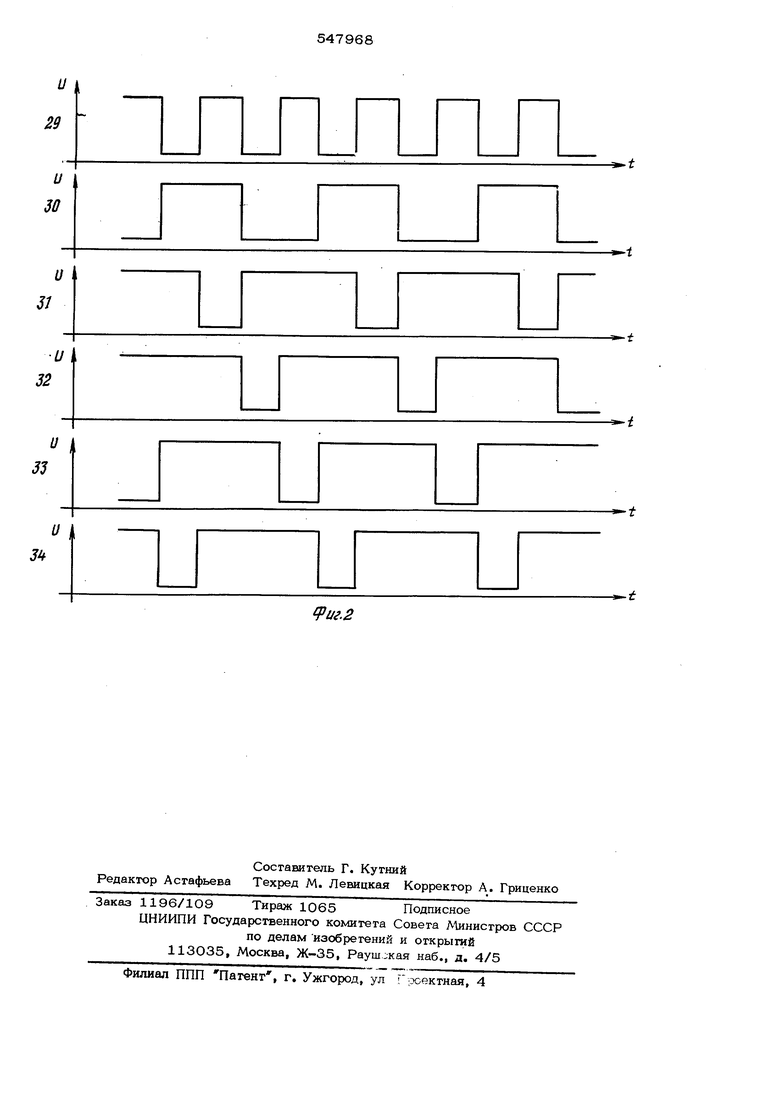

(54) ДЕШИФРАТОР а эмиттеры - с соответствующими выходам дешифратора. На фиг. 1 показана принципиальная схем предлагаемого дешифратора; на фиг. 2 - вр менные диаграммы прохождения импульсных сигналов на входе и выходе устройства. Дешифратор содержит в каждом канале входЕЮго каскада входной транзистор 1, эм тер которого подключен к соответствующем входу дешифратора База транзистора 1 чер резистор 2 соединена с шиной пр1тания. Ко лектор TparKJHCTOpa 1 подключен к базе пе ключаюшегэ транзистора 3, коллектор КОТО рогэ связан с общей шиной. Эмиттер тран зистора 3 через резистор 4 подключен к иино питания, к аноду диода 5 и к катодам диодов 6 и 7 для левого канала, 8 и 9 для правого канала выходного каскада. Катод диода 5 связав с базой инвертируюtuoro транзистора 10, коллектор которого соединен с обшей шиной. Эмиттер тран uiCTOpa 10 через резистор 11 подключен к шине питания и к катодам диодов 12 и 1 выходного каскада для левого канала и 14 и 15 для правого канала. Объединенные аноды диодных пар 12 и 15, 6 и 9, 8 и 13, 7 и 1.4 соединены с .чподами диодов 16 и 17, 18 и 19 соответственно и через резисторы 20 и 21, 2 и 23 с шиной питания. Катоды диодов 16 и 17, 18 и 19 связаны с базами выходных транзисторов 24 и 25, 26 и 27 сооТветственно. Коллекторы транзисторов 24, 25,26 и 27 объединены и подключены к общей шине. Шина питания 28, входы дешифратора 29,30. Эмиттеры этих транзисторов подключены к соответствующим выходам дешифратора 31-34, Дешифратор работает следующим образом Пусть на входы 29 и 30 поданы сигналы логической 1 ( и 2,40). В эт случае ток протекает по цепи резистор 2 транзистор 1 (база-коллектор)- транзистор 3 (база-коллектор) в каждом канале входного каскада и далее на общую щину. Коллекторные переходы транзисторов 3 смешаются в прямом направлении, а транзисто ры переходят в насыщенное состояние. При этом потенциалы на эмиттерах транзисторов 3 с оставляют - О. Ток в цепи диод 5 - транзисторы 10 (база-коллектор) отсутствует, и транзисторы 10 заперты. Через резистор 20, диоды 6 и 9, резистор 22, диод 8 и резистор 23, диод 7 и насыщенные транзисторы 3 обоих каналов ток протекает на общую шину. Диоды 12 и 15 заперты потенциалами эмиттеров закрытых транзисторов 10. Ток через резистор 21 по цепи резистор 21 - диод 16 - транзистор 24 (база-коллектор) замыкается на общую шину. Транзистор 24 переходит в насыщенное состояние. Транзисторы 25,26,27 заперты (базовый ток о-тсутствует) и уровни потенциалов на эмиттерах соответствуют Логической . Пусть теперь на один из входов дешифратора (например 29) подан сигнал логической 1, а на другой (ЗО) - логического О. В этом случае ток протекает по цепи резистор 2 - транзистор 1 (базаколлектор) - транзистор 3 (база-коллектор) левого канала входного дешифрирующего каскада, а далее на общую шину. Коллекторный переход транзистора 3 этого канала смещается в прямом направлении, а транзистор переходит в насыщенное состояние. При этом потенциал на эмиттере транзистора 3 составит и„ - О. Ток в цепи диод 5 - транзистор 1О (база-коллектор) отсутствует, и транзистор 10 заперт. Через резистор 20, диод 6, резистор 23, диод 7 и насыщенный транзистор 3 левого канала ток протекает на общую щипу. Диоды 12 и 13 заперты потенциалом на эмиттере закрытого транзистора 10 левого канала. В то же время в правом канале ток протекает по цепи резистор 2 - переход база-эмиттера транзистора 1 и вход устройства на общую шину. Транзистор 3 переходит в закрытое состояние, и потенциал на эмиттере примерно равен потенциалу источника питания Е L Ток протекает по цепи диод 5 транзистор 10 (база-коллектор) правого канала на общую щину. Транзистор 10 правого канала переходит в .ненасыщенное состояние, потенциал его эмиттера . Тогда ток через оезистор 21, диод 15, а также через резистор 23 диод 14 и открытый транзистор 10 правого канала протекает на обшую шину. При этом диоды 8 и 9 заперты высоким потенциалом на эмиттере закрытого транзистора 3 правого канала. Поскольку из четырех диодных пар только пара диодов 8 и 13 находится в закрытом состоянии, ток протекает через резистор 22, диод 18, переход база-коллектор выходного транзистора 26 на общую шину. Транзистор 26 переходит в насыщенное состояние, и уровень потенциала на его эмиттере соответствует О, а транзисторы 24, 25 к 27 заперты (базовый ток Отсутствует) и уровни потенциала на их эмиттерах соответствуют логической 1. Таким образом, двуразрядный код на входах дешифратора преобразуется в четырехразрядный адресный код на выходах в соответствии с таблицей истинности.

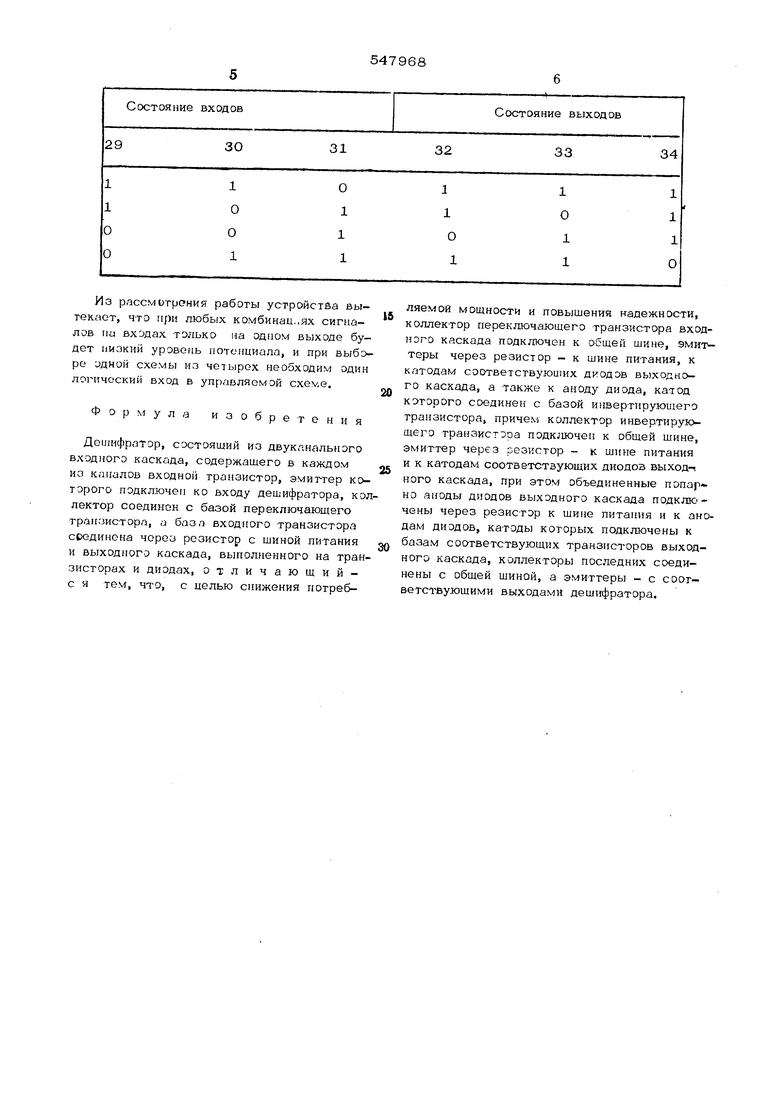

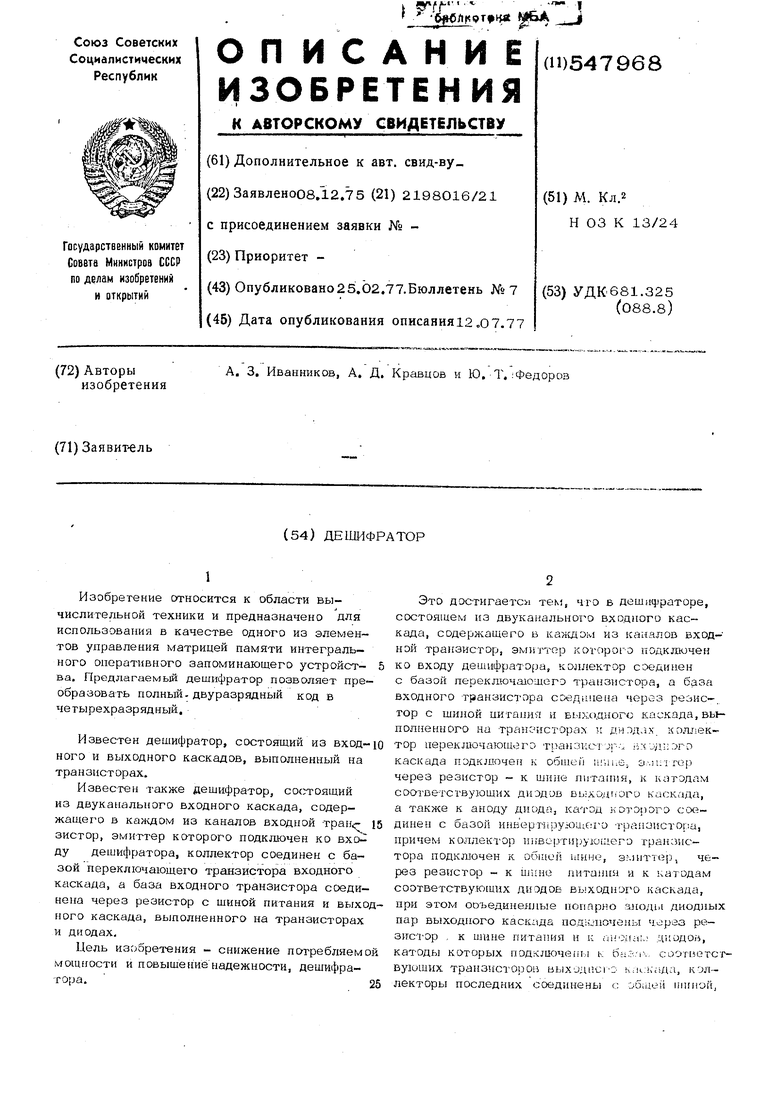

Ссютояние входов

31

30

29

О

1 О О

1 1 1

1

Состояние выходов

34

33

32

1 о

1 1

1 1

о 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое устройство | 1977 |

|

SU738171A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Логический элемент | 1988 |

|

SU1529441A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Инвертор | 1976 |

|

SU615604A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Логический элемент "запрет" | 1976 |

|

SU587627A1 |

Из рассмотрения работы устройства вытекает, что при любых комбинац..ях сигналов на вхэдах только на одном выходе будет низкий уровень потенциала, и при выборе одной схемы из четырех необходим один логический вход в управляемой схеме. Формула изобретения Дои;ифратор, состоящий из двукпнального входного каскада, содержащего в каждом ио каналов входно) транзистор, эмиттер которого подключен ко входу дешифратора, кол лектор соединон с базой переключающего транаистора, а база входного транзистора ссхэдинена через резистор с шиной питания и выходного каскада, выполненного на транзисторах и диодах, отличающийс я тем, что, с целью снижения потребляемой мощности и повышения надежности, коллектор переключающего транзистора входного каскада подключен к общей шине, эмиттеры через резистор - к шине питания, к катодам соответствующих диодов выходного каскада, а также к аноду диода, катод которого соединен с базой инвертирующего транзистора, причем коллектор инвертирующего транзистора подключег к общей шине, эмиттер через резистор - к шине питания и к катодам соответствующих диодов выход-ч ного каскада, при этом объединенные попарна аноды диодов выходного каскада подклКчены через резистор к шине питания и к анодам диодов, катоды которых подключены к базам соответствуюш,их транзисторов выходного каскада, коллекторы последних соединены с общей шиной, а эмиттеры - с соответствующими выходами дешифратора.

и

29

и 30

Уиг.2

Авторы

Даты

1977-02-25—Публикация

1975-12-08—Подача