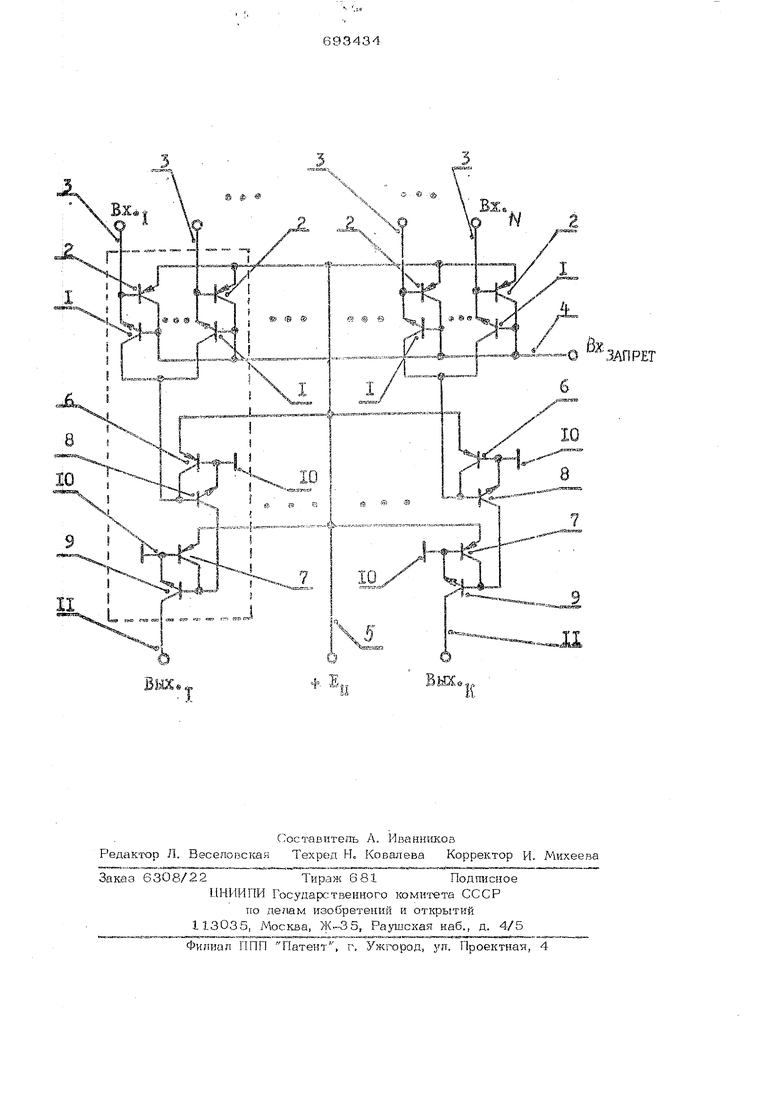

(54) УСТГОЙСТЮ ДЛЯ СЧИТЫВАНИЯ ИНФОРМАШ1И ИЗ БЛОКОВ ПАМЯТИ 3 ной, переключающий и выходной элемент выполнены на двух транзисторах р-и-Р и h-P- И -типа, причем база p-h-p и эмиттер Ц-р- И -транзисторов входны элементов подключены к входной шине, коллектор р- и -р и база ц -р- h -тран зисторов входных элемен еь подключены к шине ЗАПРЕТ, эмиттеры p-h-pтранзисторов входных элементов подключены к шине питания, а коллекторы П-р- П -транзисторов входньпс элементов подключены к базе и к коллектору П -Р- И и р- П -р -транзисторов, переключающетх) элемента, дмкттер р- П -р- транзистора переключающего элемента подключен к шине питания, база р- h --р - и эмиттер ц -р- ц -тра зисторов переключаюшего элемента подключены к шине нулевого потенциала, коллектор И-р- п-транзистора переключающего элемента подключен к базе П -р- И и к коллектору р- п -ртранзисторов выходного элемента, эмиттер р- VI -р - транзисторов выходного элемента подключен к шине питания, база р- и -р и эмиттер h -р- п -тран зисторов выходного элемента подключены к шине нулевого потенциала а коллектор И -р- и -транзисторов выходног элемента - к выходу устройства. На чертеже представлено устройство для считывания информации, построенное на К последовательно соединенных разрядах, где К - число выходов устройства. ., Каждый из транзисторных элементов разряда представляет собой такое сочетание И-р- ц и р- п -р - тран зисторов, в котором эмиттер -- и транзистора соединен с базой ро- Y -Ртранзистора, а база п -р- Y - транзистора связана с коллектором р- П ртранзистора. Число входных транзисторных элемен тов равно N соответственно числу вхо дов разряда. При этом объединенные эмиттер И -р- и -транзистора 1 и база р- п -р-транзистора 2 каждого из входн транзисторных элементов присоединены к соответствующей входной штше 3. Объединенные база п -р- И -транзистора 1 и коллектор р- vn -р - транзистора 2 входных элементов подключены к шине ЗАПРЕТ 4. Эмиттеры р- и -ртранзистоцов 2 связаны с шиной питания 5, к которой подсоединены эмиттеры р- h -р- транзисторов б и 7 34 первого и второго выходных транзисторных элементов Коллекторы транзисторов 1 входных элементов соединены с объединенными коллектором р-и -р -транзистора б и базой п -р- П -транзистора , 8, коллектор которого соединен с коллектором р- и -р транзистора 7 и базой П-р- и -транзистора 9 вьссодных элементов. Объединенные база транзистора б и эмиттер транзистора S, а также база транзистора 7 и эмиттер транзистора 9 подключены к шине нулевого потенциала 10. Коллекторы транзисторов 9 соединены с выходной шиной 11. Устройство для считывания информации из блоков памяти работает следующим о бравом. Управление устройством для считыванияинформации осуитествляется сигналом, например с блока выбора кристалла, который разрешает или запрещает прохождение основного сигнала через устройство. При подаче на управляющий вход (Вх. ЗАПРЕТ) разрешающего сигнала логической 1 подготавливаются к отпиранию базоэмиттерные переходы И-Р-Итранзисторов 1, а устройство готово к считыванию информации током, вытекающим из входов Вх - Вх , каждого из разрядов устройства. Рассмотрим работу устройства при считывании информации из блоков памяти с помощью одного из разрядов ц-ного слова. Пусть на входную шину 3 (Вх) поступает потенциал логического О, который открывает эмиттерный переход транзистора 1, создавая вытекаюший из входа (Вх..) ток. Транзистор 1 включается и замыкает через себя ток базы транзистора 8, который инжектируется транзистором б. Транзистор 8 при этом запгфается. Инжектируемый транзистором 7 ток отпирает эммитерный переход транзистора 9, что обеспечивает на выходе разряда потенциал логического О, При считывании логической 1 высокий потенциал поступает на вход (Вх ), запирая транзистор I и прерывая вытекаюший ток. Инжектируемый транзистором б ток отпирает транзистор 8 и переводит его в проводящее состояние. Ток, инжектируемый транзистором 7, замыкается через открытый транзистор 8 на шину нулевого потенциала 10. Это приводит к запиранию транзистора 9 и появлению ютенциала логической I на выходе устройства. Аналогичным образом происходит считывание информации при поступлении сигнала на любой из входов устройства считывания. Запрет считывания обеспечивается подачей на шину ЗАПРЕТ 4 управляющего сигнала логического О, что замыкает инжектируемый транзистором 2 ток через входную цепь на шину нулевого потенциала 10. Это приводит к запиранию транзистора 1, и инжектируемый транзистором 6 ток включает в проводящее состояние транзистор 8. Через открытый транзистор 8 инжектируемый транзистором 7 ток замыкаетс.я на шину нулевого потенциала Ю. Транзистор 9 при этом запирается, что обес печивает состояние логической 1 на выходе устройства. Аналогично осуществляется перевод всех выходов (Вых..-Вых. , ) устройс ва при подаче сигнала запрета в состояни логической 1. Устройство для считывания информации предполагает многоразрядное упра ление считыванием информации в отличие от известных устройств для считывания информации, что позволяет осуществлять передачу одинакового объема информации за более короткое время. Кроме того, имеется возможность управления от одного устройства несколькими схемами одновременно. Устройство отличается простотой ис полнения. Оно содержит меньшее число схемных компонентов по сравнению с известными.и полностью исключает пассивные компоненты {резисторы,, диоды Это позволяет уменьшить площадь, занимаемую устройством на кристалле, упростить топологическую компоновку, уменьшить число омических контактов и таким образом, повысить надежность устройства. Надежность повыщаётся также за счет упрощения изоляции межд компонентами и ис 1ользования самоизоляции. Устройство отличается универсально стью применения в вычислительных системах, простотой согласования с различными ТТЛ и ДТЛ-устройствами. Устройство также имеет более низго .напряжение питания (порядка 0,9-1,18 46 о сравнению с известными устройствами ого же назначения ( Ч- 5В), что позвояет улучшить качественный показатель стройства - произведение мощности отребления на среднюю величину задержи распространения сигнала, Формула изобретения Устройство для считьшания информации из блоков памяти, содержащее в каждом разряде п-входных .элементов, переключающий и выходной элементы, 1ПИНЫ питания и нулевого потенциала, отлич-ающееся тем, что, с целью повышения быстродействия и надежности устройства., оно содержит ши-: ну ЗАПРЕТ, а входной, переключающий и выходной элементы выполнены на двух транзисторах р- п Р и п-р- К1 -типа, причем база р- . ц -р и эмиттер П -р- И -транзисторов входных элементов подключены ко входной шине, коллектор р- У1 -р и база Ц -Р И транзисторов входных элементов подключены к ЗАПРЕТ, эмиттеры р- li-p- транзисторов входных элементов подключены к шине питания, коллекторы Н -транзисторов входных элементов подключены к базе и коллектору VI -р- и и р- ц -р- транзисторов переключающего элемента, эмиттер р-ц-р транзистора переключающего элемента подключен к шине питания, база р- ц -р и эмиттер и -р- П - транзисторов переключающего элемента подключены к щине нулевого потенциала, коллектор И Р- И транзистора переключающего элемента подключен к базе п -р- И и к коллектору р-У) -р-транзисторов выходного элемента, эмиттер р- h -р транзисторов выходного элемента подключен к щине питания, база р-ц-р и. эмиттер J-1 -р- и - транзисторов выходного элемента подключены к шине нулевого потенциала, а коллектор h-P И транзисторов выходного элемента подключен к вькод ; ус тройства. Источники информации, принятые во внимание при экспертизе 1.Каталог электронных схем Д.А.Т.А., 1974, с. 14. 2.Патент ФРГ № 2103 9ОО, кл. Gdll С 17/06, 1976 (прототип). О ЗАПРЕТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1975 |

|

SU656192A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| Коммутатор | 1977 |

|

SU684742A1 |

| Входной транслятор И @ Л-типа | 1984 |

|

SU1202049A1 |

| Дешифратор | 1977 |

|

SU1050110A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

Авторы

Даты

1979-10-25—Публикация

1977-05-20—Подача