Изобретение относится к области вычислительной техники и может быть использовано в специализированных и универсальных цифровых машинах.

Известно цифровое устройство для вычисления логарифмов чисел, содержащее блок управления, накопитель, арифметические блоки и логические элементы 1.

Недостатком этого устройства является низкое быстродействие и невозможность вычислгния логарифмов при произвольных основаниях.

Наиболее близким техническим решением к данному изобретению является устройство для вычисления логарифмов чисел, содержаш.ее регистр числа, накопитель, блок управления, элементы И, ИЛИ 2.

Данное устройство предназначено для вычисления только натуральных логарифмов и, кроме того, требует большой емкости накопителя и сложной схемы дешифрирования.

Целью изобретения является упрощение устройства и расширение его функциональных возможностей.

Поставленная цель достигается тем, что устройство содержит блок деления, схему сравнения, кольцевой сдвигающий регистр, первый и второй регистры результата, причем первые входы первой группы элементов ИЛИ являются информационными входами

устройства, а вторые входы подключены к соответствующим выходам блока деления, выходы элементов ИЛИ первой группы подключены к соответствующим входам регистра числа, выходы которого подключены к первым входам первой группы элементов И и первой группе входов схемы сравнения, выходы накопителя подключены к первым входам второй группы элементов И и ко второй группе входов схемы сравнения, адресные входы накопителя подключены к выходам кольцевого сдвигающего регистра, первый, второй и третий выходы схемы сравнения подключены соответственно к первому, второму и третьему управляющим входам блока управления, первый выход блока управления подключен к тактовым входам кольцевого сдвигающего регистра п регистров результата, второй выход блока управления - ко входу младшего разряда первого регистра результата, третий выход - ко вторым входам первой и второй группы элементов И к первому входу дополнительного элемента ИЛИ, четвертый выход управляющего блока - к первым входам элементов И третьей и четвертой группы и ко второму входу дополнительного элемента ИЛИ, выход старшего разряда первого регистра результата подключен ко входу младшего разряда второго регистра результата, выходы первого и второго регистров результата подключены ко вторым входам элементов И третьей и четвертой групп соответственно, выходы элементов И первой группы подключены к первым, а выходы элементов И четвертой группы - ко вторым входам элементов ИЛИ второй группы, выходы элементов И второй группы подключены к первым, а выходы элементов И третьей группы - ко вторым входам элементов ИЛИ третьей группы, выходы элементов ИЛИ второй группы подключены ко входам делимого блока деления, выходы элементов ИЛИ третьей группы - ко входам делителя блока деления, выход дополнительного элемента ИЛИ подключен к управляющему входу блока деления, выход сигнала окончания деления блока деления - ,к четвертому управляющему входу блока управления.

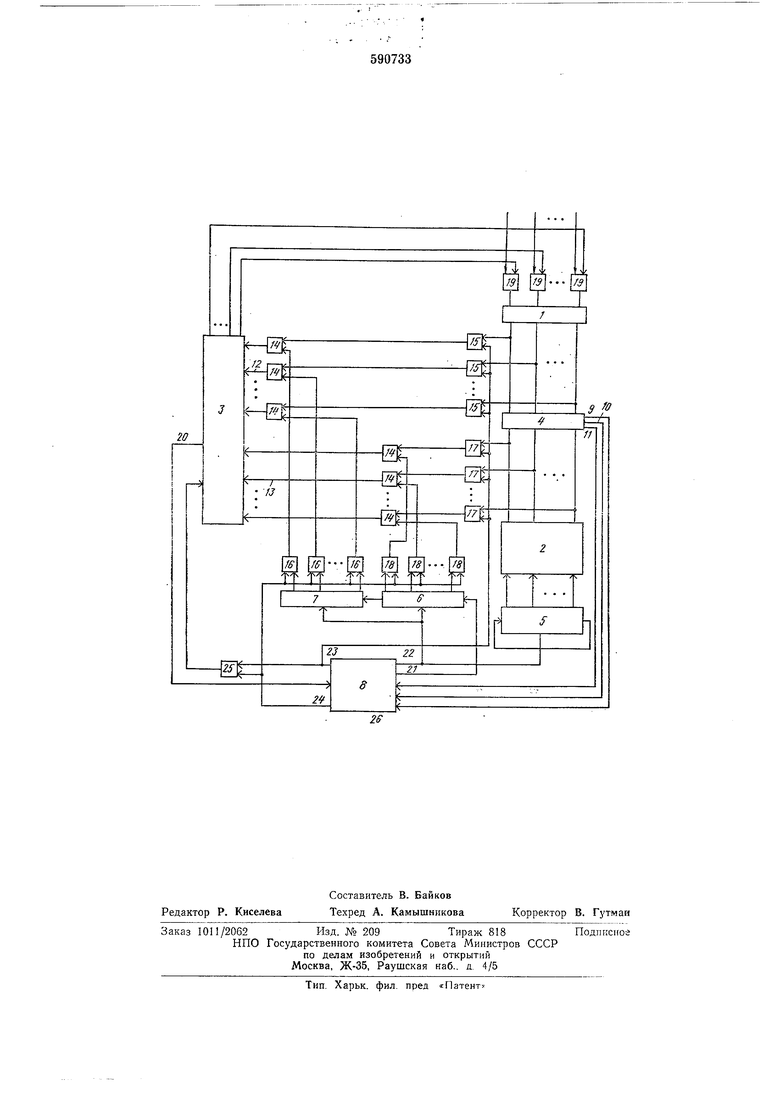

На чертеже показана -блок-схема предлагаемого устройства.

Устройство для вычисления логарифмов чисел содержит регистр числа /, накопитель 2, блок деления S, схему сравнения 4, кольцевой сдвигающий регистр 5, регистры результата 6 и 7 и блок управления 5. Выходы кольцевого регистра 5 подключены к адресным шинам накопителя 2. Выходы сигнала «Больше 9, сигнала «Равно 10 и сигнала «Меньше /7 схемы сравнения 4 подключены к управляющим входам блока управления 8. К схеме сравнения 4 подключены выходы регистра числа / и выходы накопителя 2. Входы блока деления 3 разделены на две группы - входы делимого 12 и входы делителя 13. К каждому входу блока деления подключен один двухвходовой элемент ИЛИ 14. Выходы i-ых разрядов регистра числа / и регистра результата 7 соответственно через ;-ые элементы И 15 м 16 -R элемент ИЛИ 14 подключены к t-ому входу делимого 12. Аналогично t-ый выход накопителя 2, и выход i-To разряда регистра результата 6 соответственно через элементы И /7 и /5 и элемент ИЛИ 14 подключены к t-ому входу делителя 13. Выходы результата с блока деления 3 герез элементы ИЛИ 19 подключены к входам регистра числа 1, а выход сигнала об окончании деления - к блоку управления 8. Выходы 20 блока деления 3 подключены к входам блока 8. К связанным между собой регистрам результата 5 и 7 подключены выходы сигнала «Запись 21 и сигнала «Сдвиг 22 блока управления 8. Элементы И /5 и /7 подключены к выходу 23 блока управления 8, а элементы И 16 и «/5 - к выходу 24. Выходы 23 и 24 блока .управления 8 через двухвходовой элемент ИЛИ 25 соединены с блоком деления 3. Кольцевой сдвигающий регистр 5 связан с выходом 22 блока управления 8. Вход 26 блока 8.

Алгоритм работы устройства основан на методе проб и оценок. Если необходимо вычислить и у имеет вид:

у а2 -f аг + . . . Н- а + а2 -f .

+ осГ

2 4, « {0,1

ТО П е-, где / - веса всех разрядов

-m

у, имеющие значения, равные логической «1. В первом такте вычислений принимаем, что значение разряда числа у с весом 2 равно логической «1 и сравниваем х с еЕсли , то проба удачна и значение разряда у с весом 2 действительно равно

логической «1, так как е- П е-.

i -m

Делим X на и полученное частное - х/е-сравниваем с т. е. делаем пробу для определения разряда с весом 2.

Если л; , то .

При проба неудачна, значение разряда у с весом 2 равно логическому «О, а

о/-1

в следующем такте сравниваем х с е После (/+т) проб мы определяем значения всех разрядов у.

В начале вычисления в регистре числа 1 записан двоичный код х, а в накопителе 2 в последовательном порядке записаны коды

чисел , , ,

а в кольцевом регистре 5 записан код 1000 .... О, так, чтобы единица возбуждала

l+m-l

адресную шину кода . При поступлении сигнала «Начало вычисления на вход 26 блока управления 8 в зависимости от того, какой сигнал поступает со схемы сравнения 4, а они могут быть «Больше, «Равно и «Меньше, блок управления 8 выдает различные последовательности сигналов. Если имеет сигнал «Больше, то блок управления 8 по этому сигналу вырабатывает единичный сигнал на выходе 21, по которому в младший разряд регистра результата 6 записывается логическая «1. Одновременно с этим с выхода 23 блока управления 8 к входам элементов И /5 и 17 поступает сигнал, они открываются и коды делимого х и делителя передаются в блок деления 3, куда через элемент ИЛИ 25 поступает сигнал «Начало деления. По окончании деления результат записывается в регистр числа / и выдается сигнал «Конец деления на выходе 20 блока деления 3. Этот сигнал означает окончание первой пробы. Для подготовки к следующему такту на выходе 22 блока управления 8 вырабатывается сигнал «Сдвиг и по этому сигналу сдвигается информация, записанная в регистрах результата 6 и 7 и кольцевом регистре 5. В следующем такте возбуждена шина кода накопителя 2.

Если при сравнении л; и е получаем сигнал «Равно с выхода 10 схемы сравнения 4, то в блоке управления 8 вырабатываются сигналы «Запись и 1+т-1 сигналов «Сдвига, которые соответственно с выходов 21 и 22 постулают в регистр результата б и 7 и в кольцевой регистр. Если в I-OM такте в блок управления 8 поступил сигнал «Равно, то выдается сигнал «Запись и (1 + т-i) сигналов сдвига.

При появлении сигнала «Меньше на выходе 11 схемы сравнения 4 в блоке управления 8 вырабатывается только сигнал «Сдвиг.

Выполняя (1+т) тактов, получаем результат в регистре результата 6.

Если необходимо вычислить , то последовательно вычисляются значения пх и 1па по вышеописанному алгоритму. После вычисления пх и 1па их коды находятся соответственно в регистрах результата 7 и 6. Для вычисления блок управления вырабатывает единичный сигнал на выходе 24. По этому сигналу открываются элементы И 16 и IS, коды чисел пх и 1па поступают в блок деления 3, куда поступает сигнал «Начало деления с выхода 24 блока управления 8. Результат деления получается на регистре числа 1.

В предложенном устройстве дешифратор заменен кольцевым регистром, что сокраш,ает аппаратурные затраты.

В известном устройстве для получения результата с точностью 16 двоичных разрядов необходима память объемом 9223 бит. В предлагаемом устройстве для получения результата с такой же точностью необходимо 16 шестнадцатиразрядных ячеек накопителя, что дает 256 бит или сокраш.ение в 36 раз аппаратурных затрат при реализации накопителя.

Так как в предлагаемом устройстве результат получается последовательно со старшими разрядами, то при необходимости получить разряд с более низкой точностью можно не выполнять все (1+т) тактов вычисления, а ограничиться числом тактов, дающих необходимую точность.

Устройство дает возможность вычислять значения логарифмов при любом основании.

Формула изобретения

Устройство для вычисления логарифмов чисел, содержащее регистр числа, накопитель, блок управления, элементы И, ИЛИ, отличающееся тем, что, с целью упрощения устройства и расширения его функциональных возможностей, оно содержит блок деления, схему сравнения, кольцевой сдвигающий регистр, первый и второй регистры результата, причем первые входы элементов ИЛИ первой группы являются информационными входами устройства, а вторые входы подключены к соответствующим выходам блока деления, выходы элементов ИЛИ первой группы подключены к соответствующим входам регистра числа, выходы которого подключены к первым входам элементов И первой группы и первой группе входов схемы сравнения; выходы накопителя подключены к первым входам элементов И второй группы и ко второй группе входов схемы сравнения, адресные входы накопителя подключены к выходам кольцевого сдвигающего регистра, первый, второй и третий выходы схемы сравнения подключены, соответственно, к первому, второму и третьему управляющим входам блока управления, первый выход блока управления подключен к тактовым входам кольцевого сдвигающего регистра и регистров результата, второй выход блока управления - ко входу младшего разряда первого

регистра результата, третий выход - ко вторым входам первой и второй группы -элементов И и первому входу дополнительного элемента ИЛИ, четвертый выход управляющего блока - к первым входам элементов И третьей и четвертой группы и ко второму входу дополнительного элемента ИЛИ, выход старшего разряда первого регистра результата подключен ко входу младшего разряда второго регистра результата, выходы первого и

второго регистров результата подключены ко вторым входам элементов И третьей и четвертой групп соответственно, выходы элементов И первой группы подключены к первым, а выходы элементов И четвертой группы -

ко вторым входам элементов ИЛИ второй группы, выходы элементов И второй группы подключены к первым, а выходы элементов И третьей группы - ко вторым входам элементов ИЛИ третьей группы, выходы элементов ИЛИ второй группы подключены ко входам делимого блока деления, выходы элементов ИЛИ третьей группы - ко входам делителя блока деления, выход дополнительного элемента ИЛИ подключен к управляющему входу блока деления, выход сигнала окончания деления блока деления - к четвертому управляющему входу блока управления.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 448459, кл. G 06 F 7/38, 1973. 2. Оранский А. М., Рейхенберг А. Л. Повыщение эффективности вычисления использования табличных предпроцессоров. Сб. «Теория и применение математических машин, М., изд. МГУ, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

Авторы

Даты

1978-01-30—Публикация

1975-12-30—Подача