версный вход которого соединен с выходом четвертого элемента ИЛИ и с прямым входом четвертого элемента запрета, выход которого соединен с первым выходом устройства и вторьом информационным входом первого сдвигающего регистра, выход пятого элемента запрета соединен с вторым выходом устройства и вторым входом второго сдвигающего регистра, выходы

первого и второго сдвигающих регистров соединены соответственно с первыми входами элементов И соответственно первой и второй групп, вторые входы элементов И первой группы соединены соответственно с вторыми входами элементов И второй группы и соответственно с входами управления заданием величины коэффициента устрой. ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для алгебраического сложения чисел | 1976 |

|

SU638959A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНОГО ЧИСЛА НА КОЭФФИЦИЕНТ,, содержащее первь1й и второй сдвиганяцке регисТ1 а, входы сдвига которых соединены .с тактовым входсял устройства, отличающееся teM, что, с целыо noBuiiieHlia быстродействия, в него введены первый и второй коммутаторы, первый и второй т-входовые элементы ИЛИ (где m -разрядность коэффициента), первая и вторая группы элементов И, вычисли.тельный блок,содержащий первый, второй, третий, четвертый и пятый элементы запрета, первый и второй триггеры, элемент И, перВ1ЫЙ и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и чет- . вертьй элементы ИЛИ, выходы : элементов И первой и второй: групп; . соответственно соединены с входами первого; и второго элементс в ход первого элемента ИЛИ соединен с первыми информационными входами первого и второго к яи мутатород, выход второго элемента ИЛИ ссюдинён с вторьоий инфо{ 4аци9ннь№4и входами первого и второго коммутаторов, выход первого коммутатора соединен с первым входом первого элемента ИЛИ вычислительного блока и прямым входом первого элемента запрета вычислительного блока, второй вход первого элемента ИЛИ, инверсный вход второго элемента запрета и первый вход элемента И которого соединены с выходом второго коммутатора управляющий вход которого соединен с управляющим входом первого коммутатора и входом уттравления выбором типа коэффициента устройства, первый инфо рмационный вход которого соединен с первым входом второ го элемента ИЛИ, инверсным в ходом пе рв ого Элемента за пре та и вторьди входом элемента И вычислительного блока, в то рой информационный вход устройства соединен с вторым входом второго элемента ИЛИ и прямым входом второго элемента запрета вычислитель- § ного блока, тактовый вход первого (Л триггера которого соединен с тактоBfciM входом второго триггера и тактовым входом устройст: а, вьtxoд второго элемента запрета вычиcлитeльнJЭГo блока .соединен с первым входсм третьего элемента ИЛИ, второй вход которого соединен с выходе первого элемента запрета, а третий вход г с выходом элемента И и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего эле мента Эапрета., инверсный вход которого соединен с выходом третьего эле мента ИЛИ и с первым входом первого элемента ИСКЛЮЧАОДЕЕ ИЛИ, второй вход которого соединен с прямым входом третьегоэлемента запрета и с выходом первого триггера, информационный вход которого соединен с выходом вто рого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединён с выходом первого элемента ИЛИ, а второй вход с выходом второго элемента ИЛИ, информационный вход второго триггера соединен с выходом первого элемента ЙСКЛЮЧАКМЦЕЕ ИЛИ, выход второго триггера соединен с инверсным входом четвертого элемента запрета и с прямым входом пятого элемента запрета, ин

Изобретение относится к вычислительной технике и может быть применено в системах автоматического.управления, измерения и контроля.

Известно устройство для деления двоичного Числа на коэффициент, :в состав кбторого входит (п-1) вычитателей, где п разрядность оиеранда. Каждый вычислитель состоит из полусумматора, элементов ИСКЛЮЧЖЯЦЕЕ

ИЛИ, И, или |1 . , ; . :. ; 1: .

Недостатком устройства является ограниченная область- применения ; вследствие малого набора коэффициентов., .-. . -;. . J , ; , .. ;,.7 .; , ;

Известно также делительное усзтРОЙСТВО, с помощью которого MQ3KHO

производить деление на .коэ:ффициент В его состав входят регистрьт,ау1у1 маторы, схема управления ,

Однако устройство обладает низким быстродейс;твием ,в тех случаях,/ ийформадия поступает на вхой устройства последовательным кодом, начиная со старших разрядов. Это не.позволяет эффективно использовать его в системах управления процессами в реальном масштабе времени/ когда информация поступает на вксады устройства, например, с преобра: ователей аналоГ-код или цифровых измерительных приборов поразрядного уравновешивания. В этом случае в устройствах необходимо время для накопления всех цифр операндов, и общее время вычис-f ления результата составит tg где время .накоплеИия операндов t0 - время вычислений в устройстве. На протяжении времени t|, нельзя формировать управляющее воздействие для Исполнительного органа системы .управления, так как информация 6 его величине отсутствует.

Наиболее близким к изобретению является устройство, содержащее блок суммирования, регистры делимого, делИтеля, частного, триггер, дешифратор, элемент ИЛИ. Регистры делимого и частного являются сдвигающими. Суммирующий блок предназначен для суммирования четырех кодов и содержит (п+б) разрядов. Причем регистр частного соединен с первым и вторлу выходами дешифратора и первым и вторьм

выходами устройства, выход элемента ИЛИ соединен с первым входом управления регистра делителя, выходы которого соединены ;С первой группой . информационных :в: содов сумЕматора,

0 первый и второй. вход1л дешифратора соединены соответственно с- арякклм и инверсным выходом старшего разряда сумматора, выходы регистра делимого соединены с второй группой входов

5 сумматора, а первый и второй информадионньзе выходы .регистра делимого соединены с первой и второй инфо1 1адионныии изинами, прямой .и инверсный BHXQJra стасадегр разряда сумматора соединены с вторым и третьим входами управления р гистра делителя и с первым и вторым входами триггера, вьрсоды которого соединеныг с третьим и четвертым входами дешифратора. Третья и четвертая информационные шины соединены соответственно с первой и второй группой информационных вхбдов регистров делителя и частного, выхоЗцы которого соединены с третьей группой входов сумматора, пер0 вая шина управления соединена с входом управлений сумматора и четвертым входом управления регистра делителя, вторая шина управления соединена с первым входом элемента ИЛИ,

5 счетным входом триггера, вводом управления регистра делимогб и третьим входом управления регистра частного, третья шина управления соединена с вторим входом элемента ИЛИ, пятым

0 входом управления регистра делителя, четвертым входом управления регистра частного. Это устройство позволяет вычислять частное от деления двух чисел при поразрядном поступлении операндов. При этом операнды и резуль тат представлены избыточным двоичным кодом с цифрами {l. О, 1 з} .

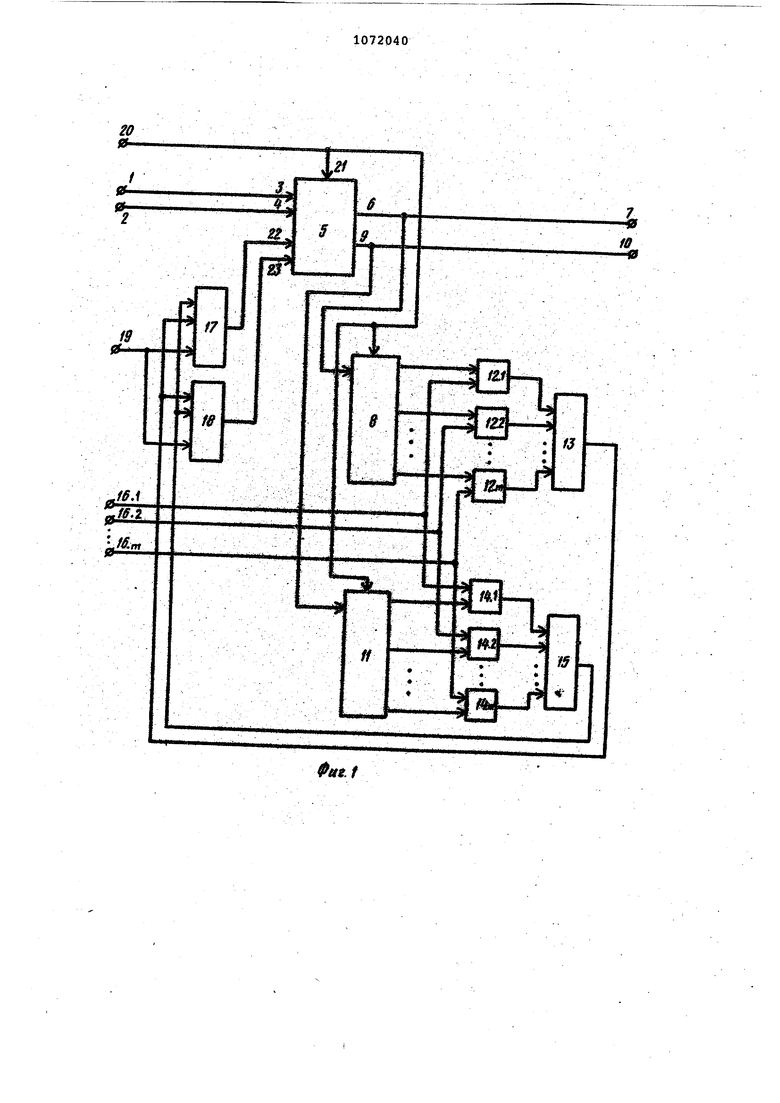

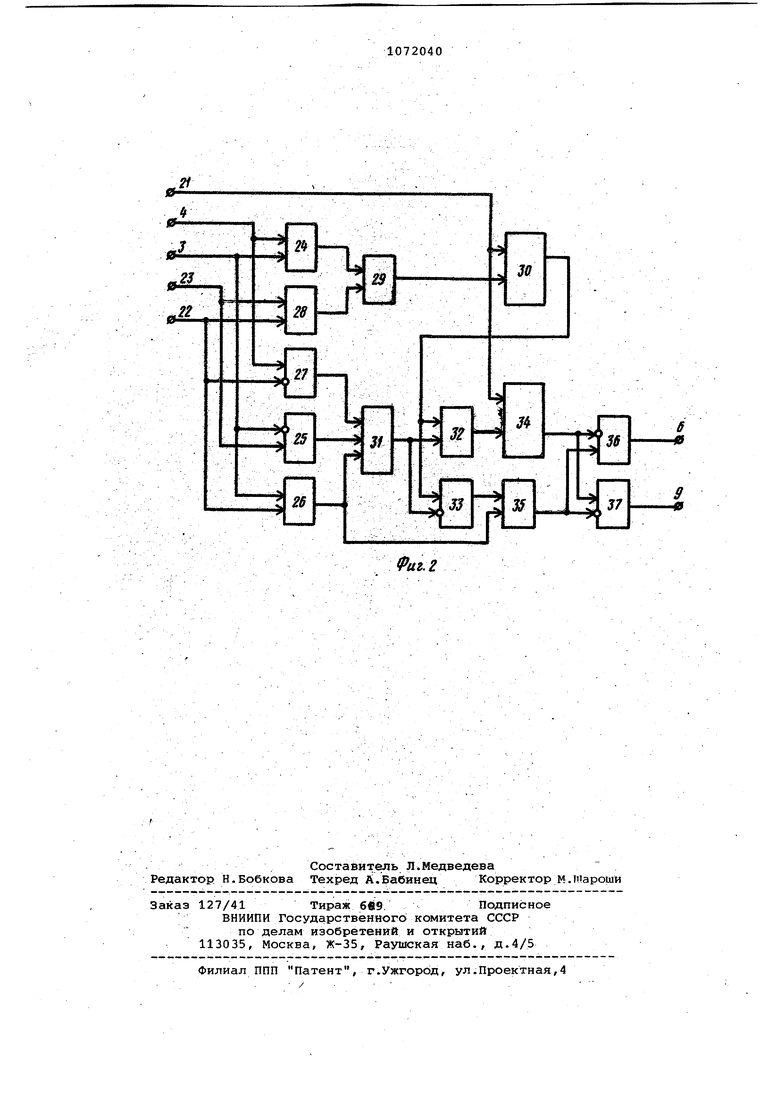

Недостатком известного устройства является низкое быстродействие вследствие большого времени вычислений в каждом цикле. Время выполнения цикл в известном-устройстве состоит из в мени сдвига , -времени суммиров ния четырех кодов tg и времени сум мирования двух кодов t0 в суммирую щем блоке, Таким образом, время вы полнения цикла вычислений в извест ном устройстве составит Ч - САВ Целью изобретения является повышение быстродействия. Поставленная цель достигается . тем, что в устройство, содержащее первый и второй сдвигающие регистры входы сдвига которых соединены с тактовым входом устройства, введены первый; и второй коммутаторы, первый и второй т-входовые элементы ИЛИ (где га - разрядность коэффициен та), первая и вторая группы элементов .И/ вычислительный блок, содержа щий первый, второй, третий, четвертый и пятый элементы запрета, перйы и второй триггеры, элемент И, первый и вторОй .элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и чёт.вертый элементы ИЛИ, причем выходы элементов И первой и второй групп соответственно соединены с входами первого и в торого э лементов ИЛИ, вы код первого элемента.ИЛИ соединен с переьми информационными входами пер вого и второго коммутаторов, выход второго элемента ИЛИ соединен с вторыми инфорл ационными входами первого и второго коммутаторов, выход первого коммутатора соединен с первым входом первого элемента ИЛИ вычислитель.ного блока и прямым входом первого элемента запр1ета вычислительного блока, второй вход перво го элемента ИЛИ, инверсный вход второго элемента запрета и первый вход элемента Икоторого соединены с Выходом в торо гО к оммута то ра, уп ав 1яющий вход которого соединен .с управляющим входом первого коммутатора и входом управления выбором типа коэффициента устройства, первый информационный вход которого . соединен с первым входом второго эл мента ИЛИ, инверсным входом первого элемента запрета и вторым входом элемента И вычислительного блока, второй информационный вход устройства соединен с вторым входом второго элемента ИЛИ и прямьлм входом второго элемента запрета вычислительного блОка, тактовый вход первогО триггера которого соединен с тактовым входом второго триггера и тактовым входом устройства, выход второго элемента запрета вычислительного блока соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента запрета, а третий вход - с выходом элемента И и первым входом четвертого ;элемента ИЛИ, второй вход которого соединен с выходом третьего элемента запрета, инверсный вход которого соединен с выходом третьего элемента ИЛИ и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которо- го соединен с прямым входо.М: третьего элемента запрета и с выходом первого триггера, информа.ционный вход которого соединен с выходом второго элемента ИСКШ)ЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом первого элемента ИЛИ, а второй вход с выходом второго элемента ИЛИ, информационный вход второго триггера соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго триггера соединен с инверсным входом четвертого элемента запрета и с пряMt3M входом пятого элемента запрета, инверсный вход которого соединен с выходом четвертого элемента ИЛИ ис прямым входом четвертого элемента запрета, выход которого соединен с первым выходом устройства и вторым информационным входом первого сдвигающего регистра, выход пятого элемента запрета соединен с вторым выходом устройства и вторым входом второго сдвигающего регистра, выходы первого и второго сдвигающих регистров соединены соответственно с первыми входами элементов И соответственно первой и второй групп, вторые входЕЛ элементов И первой группы соединены соответственно с вторыми входами элементов и второй группы и соответственно с входами управления заданием величины коэффициента устройства. На фит. 1 изображ1ана структурная схема устройства для деления двоичного числа на коэффициент; на фиг.2структурная схема вычислительного блока. . .. Входы 1 и 2, устройства подключены к входам 3 и 4 вычислительного блока 5, выход 6 которого связан с выходом 7 устройства и информационным входом сдвигающего регистра 8, а выход 9 - с выходом .10 устройства и информационным входом сдвигающего, регистра 11. Выходы сдвигающего регистра 8 ггодключены к первым входам элементов И 12.1-12.т, выходы которых связаны с входами элемента ИЛИ 13. Выходы сдвигающего регистра 11 соединены с первыми входами элементов И 14.1-14.т, выходы которых связаны с входами элемента ИЛИ 15. Вторые входы каждых j-x (,m) элементов И 12.j и 14., соединены с входом 16.j устройства. Выходы элементов ИЛИ 13 и 15 связа:ны с информационными входами коммутаторов 17 и 18. Управляющие входы коммутаторов 17 и 18 подключены к входу 19 управления выбором типа коэффициента устройства. Тактовый вход 20 устройства связан с управляющим вхо дом 21 вычислительного блока 5, а также с входами сдвига сдвигающих регистров 8 и 11. Выходы коммутаторов 17 и 18 подключены соответственно к входам 22 и 23 вычислительного блока 5. Вычислительный блок 5 может.быть построен следующим образом (фиг.2). Вход 3 соединен с входом элемента ИЛИ 24, с инверсным входом эле-г мента 25 .запрета и с входом элемента И 26. Вход 4 связан со входом элемента ИЛИ 24 и с прямым входом элемента 27 запрета. Вход 22 соединен с входом элемента VI 26 vi элемента ИЛИ 28, а также с инверсным входом элемента 27 запрета, вход 23 подключен к входу элемента ИЛИ 28 и к прямому входу элемента 25 запрета. Выходы элементов ИЛИ 24 и 28 соединены с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29, выход которого подключен к входу триггера 30. Выходы элементов 25 и 27 запрета и элемента И 26 связаны с входами элемента ИЛИ 31 , выход которого подктаочен к входу элемента ИСКЛЮЧАЮ ЩЕЕ ИЛИ 22 к к инверсному входу элемен та 32 запрета.Прямой вход элемента 33 и второй вход элемента ИСКЛЮЧАЮЩЕ ИЛИ 32 подключены к выходу триггера 30. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 связан с входом триггера 34, Выходы эле ментов И 26 и запрета 33 соединены с входами элемента ИЛИ 35, выход ко торого связан с первым входом элемента 36 запрета и с инверсным входом элемента 37 запрета. Выход триг гера 34 подключен к вторым входам элементов 36 и 37 запрета, выходы которых соединены соответственно с выходами 6 и 9. К управляющим входа триггеров 30 и 34 подключен вход 21 Триггеры 30 и 34 могут быть построе ны на основе D-триггеров с внутрен ней задержкой. Устройство предназначено для деле ния двоичного числа на коэффициенты типа К,| 4+2 или 4-2% где ,1 1,т . В исходном состоянии сдв гающие регистры 8 и 11 и триггеры 30 и 34 обнулены. Перед началом вычислений на вход 19 поступает сигнал, который выбирает тип коэффицие та. Если этот .сигнал равен единице, то производится деление на. коэффициент типа kg/ если же он равен нулю, то производится деление на коэффициент типа k«. Кроме того, на один из входов 1ь.1-16.т поступает единичный сигнал (например, на вход 16.j), который окончательно выбирае значение. коэффициента fcij или kjj 4-Z. Сигналы на входах 19 и 16 присутствуют в течение всего времени вычислений. Вычисления в устройст.ве производятся в (n-tp) тактах, где п-разрядность операнда, а р добавочное число тактов, определяющее точность вычислений. На вход устройства последовательно со старших разрядов поступает операнд, представленный в избыточной двоичнойсистеме счисления с цифрами fl. О, 1}. Ограничения на знак числа не накладываются. Операнд представляется в естественной форме, т.е. запятая фиксируется досле разряда с весом 2. К началу каждого i-го такта на входы 1 и 2 поступает 1-й разряд операнда х , При этом, е.сли единица присутствует на входе 1, то х 1 , если единица присутствует на входе 2, то х 1, если на обоих входах - нули, то х| 0. На входы 22 и 23 вычислительного блока 5 поступсцот цифры второго операнда . Это задержанные на J тактов сигнала с выходов 6 и 9, т.е. с игн алы с выходов элеме н тов ИЛИ 13 и 15. При этом, если на вход 19 поступает единичный сигнал, то на вход 22 поступает сигнал с выхода элемента ИЛИ 13, а на вход 23 - сигнал с в ыхрда элемента ИЛИ 15. И наоборот, если на входе 19 присутствует нуль, то на вход 22 поступает сигнал с выгхода элемента- ИЛИ 15, а на вход 23 с выхода элемента ИЛИ ДЗ. Значение у- 1 кодируется наличием единицы на входе 22, а у в Т - наличием единицы на входе 23, в противном случае у| 0. Вычислительный блок 5 22(Х + У). реализует функцию Z При поразрядном поступлении операндов он работает следукадим образом. Если сумма очередных разр5адов операндов ( у-) равна 1 или 1, единич ный сигнал появляется на выходе элемента ИСКЛЮЧА1ВДЕБ ЮШ 29. Если ( yj ) равна 1,2 или 2, то единица - на выходе элемента ИЛИ 31. Если (х у, ) 2, то единица - на выходе элемента И 26. JB зависимости от значений сигналой на выходах элемейтов И 26 и ИЛИ 31, а акже состояний триггеров 30 и 34 на выходы б и 9 передается значение очередного разряда результата 2} . При этом кодируется наличием единицы на выходе 6, Zi Т наличием едийиды на выходе 9 и Z О - отсутствигем сигналов на обоих выходах. Затем на тактЫый вход 20 устройства поступает управляющий сигнал. После его окончания производится прием кода в триггеры 30 и 34 и сдвиг в сдвигающих регистрах 8 и 11. На этом заканчивается один такт вычислений. В результате выполнения (п+р тактов на выходах устройство последовательно, разряд за разрядом.

значение Z +2-

X

4 - 2-1

Пример. Пусть необходимо разделить на k .4-2 3.5 число X (-11,625) {1101,iiil. Вычисления следует произвести до седьмого двоичного знака после запятой. Перед началом вычислений на входы 19 и 16.1 поступают единичные сигналы. Состояния элеменгов устройства показаны в таблице в каждом такте вычислений. В результате вшюлнения 11-ти тактов вычислений на выходах устройства сформировалось значение .(0101, OIOIOOI) (-3,3203)ft, .

Время выполнения такта в данном устройстве состоит из времен образования очередной цифры результата tp и вроиени t| , необходимого для ; сдвига сдвигакщих регистров и поступления новой цифры операнда у- на входы 22 и 23 вычислительного блока. Из описания работы вычислительного блока следует, что tp 5Ь, где tg - время срабатывания логического элемента. В. свою очередь tj Чке 9 (здесь время срабатывания

коммутаторов, в качестве которых используются мультиплексоры, принято равным 2t9 ). Таким образом, время выполнения такта в предлагаемом устройстве составит t Тогда время вычислений в предлагаемом устройстве в t ic +tef -tcAt

-I t 9t,f-.-tcVe

.: раз меньше,чём 9t, + tcftB

в известном устройстве, при последовательной организации распространения переноса в суммирующем блоке. Здесь принято tc-i (n+6)t+, где задержка в одноразрядном комбинационном сумматоре. В свою очередь t принято равным 2ь . Например, для и 32, q л 15.

При использовании сверхпараллельных сумматоров t (2logf 1 + 3)t4, где 1 - длина сумматора. Тогда ti, 2( (п+б) Ч-. з)% + t{.,e , что при п 32 составит. t(j GOt +tjig. Ив этом случае быстродействие устройства примерно в 6,5 раз выше быстродействия известного устройства.

Таким образом, введение новых элементов и конструктивных связей позволяет увели ить быстродействие устройства. .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР 758153, кл.с 06 Р 7/52, 1.975 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-01—Подача