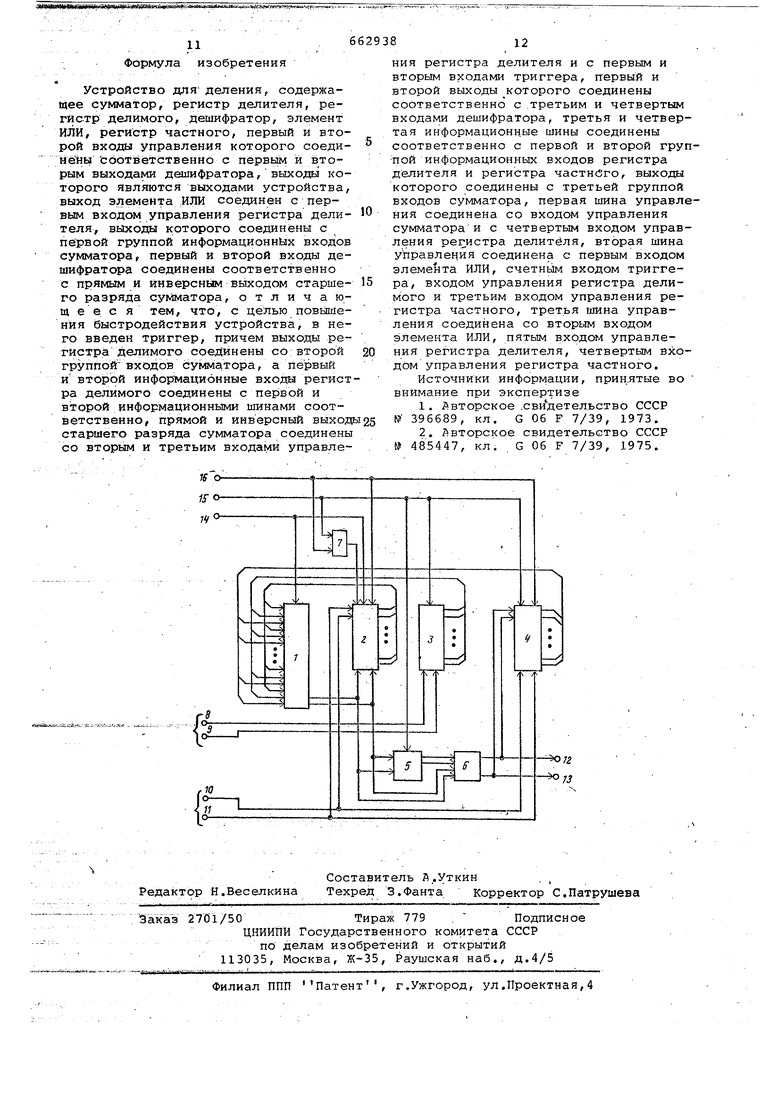

., V./ ; ;:,:Г . ;- ; ;.. Изобретение относится к области вычислительной техники и может быть применейб и цифровых вычислительньК машинах, специализированных цифровых вычислительныхустройствах, и .вычйсдительнйх средах, построенных на бол ших интегральных схемах. .V Известно устройство для деления в котором время выполнения операций деления ПрЬпорциональнО,п ij. Недостатком известного устрбйстйа является невысзркое быстродействие при раЬот в реальном масштабе времени,, .. Наиболее близким по технической сущности к предлагаемому явлйется устройство , содержащее сумматор, регистр делителя, регистр делимого, де шифратор, элемент ИЛИ, регистр часг. тногб, первый и: второй входы управления которого соединены соответст венно с первым и вторым выходами дешифратора, выходы которого являются выходами устройства, выход элемента ИЛИ соединен с первым входом управления регистра делителя, выходы кото рого соединены с первой группой информационных входов сумматора, первый и второй входы дешифратора соединены соответственно с прямым и ин.ве сным; вйх6д6м ;сгга5)шёго разр1Яйа -сумматора Г2). . ... : Недостйтйой йайн6 о устройства является ни.зкбёбыстродействие. Цель изобретения - повышение быстродействия устройдтва. С этой целью в иёгЬ:введен триггер, .йрйчем выходы регистра ДёлймбгО соединены со второй группой входов сумматора, а первый и второй информационные входы регистра дёйймогб соединены с первой И втЬрой инфо рмацибнными шинами coovвё Ственно, и инверсный выходы старшего разряда сумматора соединены со вторым и третьим входами управленйя р|ег ст 1а делителя не первым и вторым.вхЪдами триггера, первый и второй выходы которого соедичейы Соответственно с третьим и четвертым вхсщами дешифратора, третья и четвертая информационные шины соединены соответственно с первой и второй группой информационных входов регистра делителя и регистра частного, выходы которого соединены с третьей группой входов сумматора, первая шина управления соединена со входом управления сумматора и с четвертым входом управления регистра делителя, вторая шина управления соединена с первым входом .элемента ИЛИ, счетным входом т ри ггера, в ходом у п{«айл ния регистра делимого и третьим ходом управления регистра частного, IrpeTlbH управления соединена со вторым входом элемента ИЛИ, пятым вх дом управления регистра делителя, четвертым входом управления регистра частного. На чертеже изображена структурная схема предлагаемого делительного уст ройства. Устройство содержит (п+6) разрядный блок суммирования 1 (п-разрядность исходных операндов),(п+3) разрядный регистр 2 делителя,, п-разрядный регистр делимого 3, поразрядный регистр 4. частного, триггер 5, деишф ратор 6, элемент ИЛИ 7, информационные шины 8-11, выходы устройства 12, 13, шины управления 14-16. Блок суммирования. 1 имеет цепь сдвига содержимого на два разряда влево. Регистры 2,3 и 4 имеют цепи вьщаЧИ. прямого и дополнительного кодов и Цепи сдвига на один разряд влево. РегистЕжл 2 и 4, кроме того, имеют цепи приема кода. Младшие разряды регистров 2 и 4 являются суммир гйЩМи, а остальные разряды этих ре гистров имеют Цепь распространения переноса. Дешифратор 6 может быть построен в соответствии с системой перек:лк)чательных функций вида: : ft Ч 7 где fi- функция i-ro выхода () дешифратора б; р - значение старшего .разряда блок суммирования 1 с весом - значение состояния тригге, 5 . , Исходные операции А и В и результат X представлены двоичным избыточным ЙОДОМ с цифрами 1,0,1. При этом операнды и в и результат X имеют вид: А.Е а; 1-1 f.-. 1|де а,Ь|,,0 ,ij. ii ..Каждый разряд числа в избыточном представлении кодируется двумя цифр ми .из множества Г,О,у. При этом цифре Т соответствует сигнал на вксд В или 10, или на выходе 12. Цифре 1 соответствует сигнал на входе 9 или 11, или выходе 13. Цифре О соответствует отсутствие сигналов на входа 8,9, на входах 10,11 или на выходах 12,13. Коды делимого А и делителя В пос пают поразрядно соответственно на входы 8,9 и 10,11 одновременно, т.е. в каждый момент времени на входы поступают разряды делимого и делителя с одинаковыми весами. На величины и и В накладываются следующие ограничения: , L|2i& i. Принцип работы устройства заключается в следующем. В исходном состоянии в младшем разряде регистра 3 записана единица, а все остальные регистры, блок суммирования 1 и триггер 5 установлены в нулевое состояние. В каждом цикле вычислений на тактирующие входы 14,15 и 16 поочередно поступают соответственно тактирующие сигналы у, У2 и УЗ . К началу каждого i-ro цикла вычислений (,2... п+З) на входы 8,9 и 10,11 поступают цифры очередных разрядов соответственно aj и bj. В первом такте цикла деления сигнал у со входа 14 поступает на цепь сдвига блока суммирования 1 и на цепь приема кода регистра 2. В результате этого содержимое блока суммирования 1 сдвигается на два разряда влево, а к младшему разряду регистра 2 прибавляется значени е очередного разряда bj. Если (присутствует сигнал на входе 10), то вычитается единица из младшего разряда регистра 2. Если (присутствует сигнал на входе 11), то прибавляется единица к младцаему разряду регистра 2, а если (сигнал на входах 10 и 11 отсутствует), то регистр 2 не изменяет своего состояния. Таким образом, в регистре 2 происходит накопление делителя В. Во втором такте цикла деления сигнал у с входа 15 поступает на цепь приема кода триггера 5, через элемент ИЛИ 7 поступает на цепи выдачи кодов регистра 2 и на цепи выдачи кодов и сдвига регистров 3 и 4. В результате этого в блоке суммирования 1 происходит суммирование содержимого этого блока с кодами, поступающими с выходов регистров 2,3 и 4, а в триггер 5 записывается предыдущее состояние старшего разряда блока суммирования 1 (одновременное суммирование в блоке суммирования 1 и запись предыдущего состояния старшего разряда этого б.лока в триггер 5 возможны, так как блок суммирования 1; является сдвигающим и, следовательно,каждый разряд этого блока должен быть построен на паре триггеров или на триггерах с внутренней задержкой), При этом код на выходах регистра 2 зависит от предыдущего состояния старшего разряда (знака) блока суммирования 1. Если в этом разряде записан нуль (положительный знак),то из регистра 2 выдается дополнительный код, а если в этом разряде эапиЬана единица (отрицательный знак), то из регистра 2 в блок суммирования 1 передается прямой код. Код на выходах регистра 3 зависит от сигналов на входах 8 и 9, Если присутствует сигнал на входе 8 ( ), то из регист ра 3 выдается дополнительный код, а если присутствует сйТНал нЖ вхЪдё 9 (ajsl) - выдается прямой код. При от сутствии сигналов на входах 8 и 9 код из регистра 3 не выдается. Кол н выходах регистра 4 зависит от значений сигналов на входах 10 и 11, Если присутствует сигнал на входе 10 (bj-Т), то из регистра 4 выдается прямой код, а если присутствует сигнал на в,ход« 11 () - вьщается дополнительный код. При отсутствии сигналов на входах 10 и И код из регистра 4 не выдается. Одновременно с этим содержимое ре гистров 3 и 4 сдвигается на один раз ряд влево (одновременная выдача кодов из этих регистров и сдвиг их содержимого возможны, так как регист ры 3 и 4 являются сдвигающими и следовательно, каждый разряд этих регистров должен быть построен на паре триггеров или на триггерах с внутрен ней задёряской) ., При выдаче дополнительного кода из регистров 2,3 и 4 на входы свободных (не связанных с выходами регистров 2,3 и 4) разрядов блока суммирования 1 подаются единич ные сигналы и,, кроме того, младшего разряда подается еще один единичный сигнал. Перед началом третьего такта цикла вычислений да1Шфра тор б анализирует состояние триггера 5 и старшего разряда блока суммирования 1 и на выходах дешифратора б появляется код очередного разряда частного х, который поступает на вы ходы 12 и 13 частного. В третьем так те цикла деления сигнал у с входа 16 поступает на цепь приема кода регистра 4, на цепь сдвига регистра 2 и через элемент ИЛИ 7 - на цепи выда чи кодов регистра 2. В результате этого из регистра 2, в соответствии со значением старшего (знакового) разряда блока суммирования 1, в блок суммирования 1 вф ается прямой или дополнительный код, а к младшему раз ряду регистра 4 прибавляется значени очередного разряда х(. При этом, если присутствует сигнал на выходе 12 (), то вычитается единица из ЮТадшего разряда регистра 4. Если присутствует сигнал на выходе 13 (), то прибавляется единица в младаиий разряд регистра 4, а если сигналы на выходах 12 и 13 отсутству 1ют (xjsO), то регистр 4 не изменяет своегб состояния. Таким образом, в регистре 4 происходит накопление частного X. Одновременно с этим содер жймое регистра 2 сдвигается на один разряд влево. На этом заканчивается один цикл вычислений. Разряд частного с весом 2 появляется через 3 38в цикла вычислений после поступления разрядов делимого И делителя с весом 2. Поэтому, для получения частного с точностью 2 необходимо выполнить п+3 циклов вычисления. Рассмотрим работу устройства на примере. Пусть Л (25/б4 дес.(0,11|111)изб., В а(43/б4)дес. (О,111011)изб. Для этих значений операндов , поэтому необходимо выполнить 9 циклов вычислений. Процесс вычислений иллюстрируется таблицей состояний блока суммирования, регистров и триггера устройства. Результат вычислений для этих значений исходных операндов (001,10111Т)изб. (3.7/б4)дес. Из рассмотренного примера видно, что для получения результата с точ2-пнеобходимо выполнить ностью гп+З ЦИКЛОВ вычислений. Отношение быстродействия известного и предлагаемого устройства составляет: Если принять па(32, что соответствует показателям современных ЦВМ, то Следовательно, быстродействие предлагаемого устройства выше быстродействия известного устройства при работе в реальном масштабе времени в 1,8 раз. Определим задержку, вносимую К устройствами при использовании их в вычислительной среде. Как было показано, после прихода разрядов делимо го. и делителя с весом 2 f разряд частного с весом 2 появляется через 3 цикла вычислений. Таким образом,оче-, редной разряд, полученный на выходе устройства, обрабатывается другим устройством в следующем цикле, следовательно задержка, вносимая одним устройством, составляет 4 цикла. Задержка, вносимая К устройствами, будет составлять -циклов. Таким образом, выигрыш в быстродействии при использовании в вычислительной среде предлагаемого устрой- ства по сравнению с изёестным будет пределяться выражением: ИЗБ. П(К+1) 4К-Г При nfe32 применение в вычислительной среде предлагаемого устройства розволяет увеличить быстродействие в 32/44 8 раз.

662938

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для деления | 1976 |

|

SU590738A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

OOObOOOWTOOOOb 000001 .0

UOOOOO 000010

000000 000100

OOOOOO OOlOOO

3 (. , , , - ,

00000.1010

000001

-.A- -.

1 01 0 00

oooooroio

000010 010000

000010100

000001

fe g ;fer - ggg ligty-ji..,,;

1 1 10 1 Ol

000010101

SffiS

.У11/111-1111110

;;ob 0000000000

00 0000000001

0 ii iiiiiiioiO

0poo000000

Ir ill 11 ill 10

0 11 1111110110

;;oo oooobooooo . oo;:Qo iooogpioo

00 0000000010 01

4i:.iiiiiioiiO ii iiiiiiiooo

11,1111100000

00 OOOOOlOlOO

oo oooooooobo

00:QOOOOUIOOO 41,1111111100 10 1

op OOOOOlOlOO 00,0000010000

00,0001000000 00,0000000000

11 1111110000

Авторы

Даты

1979-05-15—Публикация

1976-11-23—Подача