клона, второй буферный регистр, элемент ИЛИ, группа элементов ИЛИ и триг гер выбора режима, вход установки в единицу которого соединен с управляющим входом режима преобразования, вход установки в ноль триггера выбора режима соединен с управляющим входом режима записи преобразователя, прямой и инверсный выходы триггера выброса режима соединены соответственно с тре тьим входом первого элемента И и первым входом третьего элемента И, второй вход которого соединен с входом записи преобразователя, выход третьего элемента И соединен с стробируюащм входом записи блоков памяти узловых значений ординат и абсцисс, входом элемента задержки и первьм входом элемента ИЛИ, подключенного вторым входом к выходу сравнения блока вычитания ординат, выход элемента ИЛИ подключен к счетному входу реверсивного счетчика адреса, вход вычитаемого блока вычитания ординат соединен с 10 6 выходами элементов ИЛИ группы, первые входы которых соединены с выходами соответствующих разрядов реверсивного счетчика результата, вторые входы элементов ИЛИ группы соединены с выходами соответствующих разрядов второго буф-грного регистра, информационный вход которого соединен с выходом блока памяти узловых значений ординат, вход синхронизации второго буферного регистра соединен с выходом элемента задержки, входом синхронизации первого буферного регистра и стробирующим входом записи блока памяти коэффициентов наклона, подключенного адресным входом к выходу реверсивного счетчика адреса, информационный вход и выход блока памяти коэффициентов наклона соединены соответственно с выходом блЬка деления и управляющим входом управляемого делителя частоты, стробируюпшй вход которого соединен с вы-. ходом сравнения блока вычитания ординат .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Многофункциональный преобразователь | 1986 |

|

SU1401479A1 |

ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор импульсов, два элемента И, управляемый делитель частоты, реверсивный счетчик результата, первый буферный регистр, блок вычитания ординат,блок деления, блок вычитания абсцисс,блок памяти узловых значений ординат, блок памяти узловых значений абсцисс, регистр аргумента, блок вычитания аргумента, формирователь импульсов, триггер разрушения приема аргумента, знаковый регистр и реверсивный счетчик адреса, причем .выход генератора импульсов подключен к первому входу первого .элемента И, второй вход которого соединен с выходом сравнения блока вычитания ординат,первым входом второго элемента И, входом установки в ноль триггера разрешения приема аргумента и входом синхронизации знакового регистра, выход, первого элемента И соединен с сигнальным входом управляемого делителя частоты, подключенного выходом к счетному входу реверсивного счетчика результата, выход которого соединен с выходом преобразователя, вход управления реверсом реверсивного счетчика результата соединен с выходом знака разности блока вычитания ординат, выход кода разности которого соединен с входом кода делимого блока деления, вход уменьшаемого блока вьпитания ординат соединен с выходом блока памяти узловых значений ординат, подключенного адресным входом к адресному входу блока памяти узловых значений абсцисс и выходу реверсивного счетчика адреса, вход управления реверсом которого соединен с выходом знакового регистра, подключенного информационным входом к выходу знака разности блока вычитания аргумента и входу формирователя импульсов, выход которого подключен к входу установки в единицу триггера разрешения приема аргумента, инверсный выход которого соединен с вторым входом второго элемента И, подключенного выходом к входу синхронизации регистра аргумента, информационный вход которого соединен с входом ввода аргумента СО преобразователя, выход регистра ар00 гумента соединен с входом уменьшаемого блока вычитания аргумента, вход о о вычитаемого которого подключен к выходу блока памяти узловых значений Oi абсцисс информационному входу первого буферного регистра и входу уменьшаемого блока вычитания абсцисс,вход вычитаемого которого соединен с выходом первого буферного регистра, выход блока вычитания абсцисс соединен с входом кода делителя блока деления, отличаю щийся тем, что, с целью повьшения быстродействия, в него введены третий элемент И, элемент задержки, блок памяти коэффициентов на

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе гибридных вычислительных систем, а также для вьтолнения функциональных преобразований в измерительной технике.

Известно устройство для функционального преобразования цифровых сигналов, содержащее генератор импульсов, управляемый делитель частоты, реверсивный счетчик, блок вычитания кодов, блок памяти, деш1«} ратор и входной регистр fl 3.

Недостатком устройства является низкая точность функционального преоб разования, обусловленная равномерным расположением узлов аппроксимации.

Наиболее близким к предлагаемому является устройство для цифрового функционального преобразования, содер жащее регистр аргумента, генератор импульсов, первый элемент И, блок вычитания ординат, управляемый делитель частоты, реверсивный счетчик результата и блок памяти узловых значений ординат, причем информационные входы регистра аргумента соединены со входа ми устройства, первый вход первого

элемента И соединен с выходом генератора импульсов, а второй вход - с выходом обнуления блока вычитания ординат, выход первого элемента И соединен с сигнальным входом управляемого делителя частоты, выход которого соединен со счетным входом реверсивного счетчика результата, выходы которого соединены с выходами устройства и

входами вычитаемого блока вычитания ординат, выход знака разности которого соединен со входом управления реверсом реверсивного счетчика результата, выходы блока памяти узловых

значений ординат подключены к входам уменьшаемого блока вычитания ординат, причем выходы кода разности блока вычитания ординат соединены со входами делимого блока деления, выходы которого соединены с управляющими входами управляемого делителя частоты, входы

делителя блока деления подключены к выходам блока вычитания абсцисс, выход обнуления блока вычитания ординат

соединен со входами синхронизации блока деления, буферного регистра и,., регистра знака, а также со вторым входом первого элемента И и через элемент задержки - со счетным входом реверсивного счетчика адреса, первым входом второго элемента И и входом ус тановки в ноль триггера разрешения шриема аргумента, выход установки в единицу которого подключен к выходу формирователя импульсов, а инверсный выход соединен со вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра аргумента, выходы которого соединены с входами уменьшаемого блока вычитания аргумента, выход кода знака которого подключен к входу формирователя импульсов и информационному входу регистра знака, выход которого соединен со входом управления реверсом реверсивного счетчика адреса, выходы которого подключены к адресным входам блоков памяти узловых значений ординат и абсцисс, выходы блока памя.ти узловых значений абсцисс подключены к входам уменьшаемого блока вычита ния абсцисс, входам вычитаемого блока вычитания аргумента и информационным входам буферного регистра, выходы которого соединены с входами вычитаемого блока вычитания абсцисс Г2Д. Недостатком устройства является пониженное быстродействие, обусловленное необходимостью вычисления в каждой узловой точке коэффициента передачи управляемого делителя частоты . Целью изобретения является повыше ние бьютродействия.. Поставленная цель достигается тем, что в цифровой функциональный преобразователь, содержащий генератор импульсов, два элемента И, управляемый делитель частоты, реверсивный счетчик результата, первый буферный регистр, блок вычитания ординат, бло деления, блок вычитания абсцисс, блок памяти узловьк значений абсцисс блок памяти узловых значений ординат

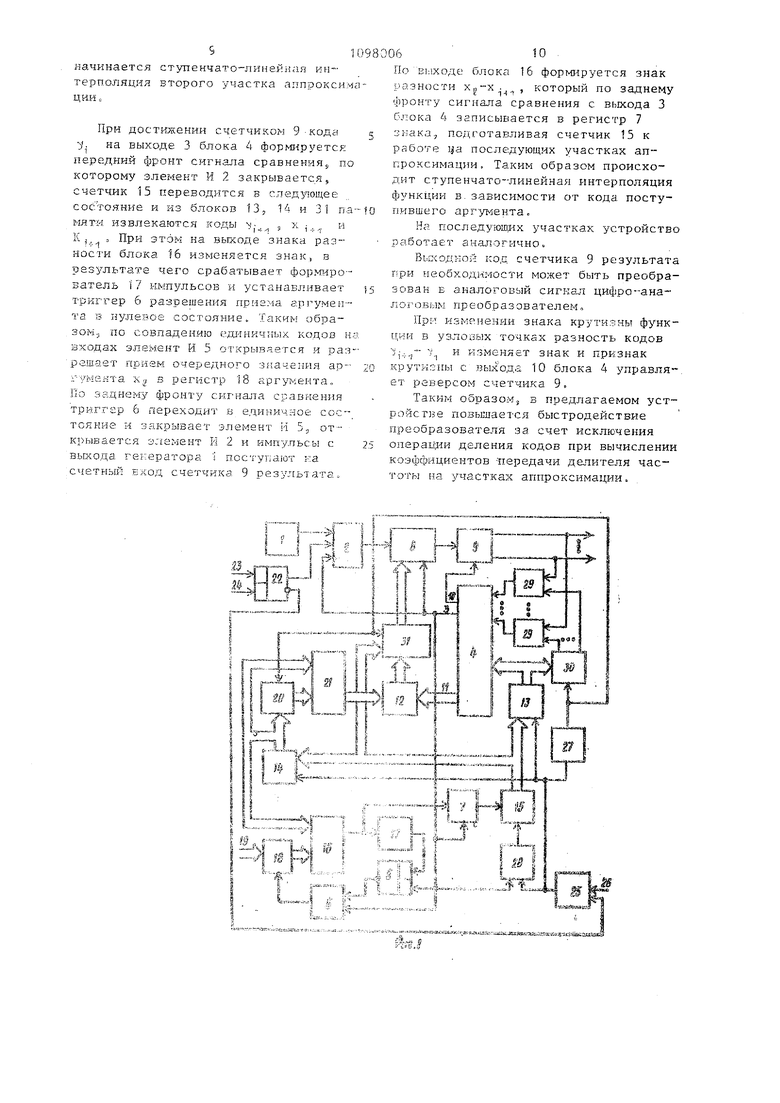

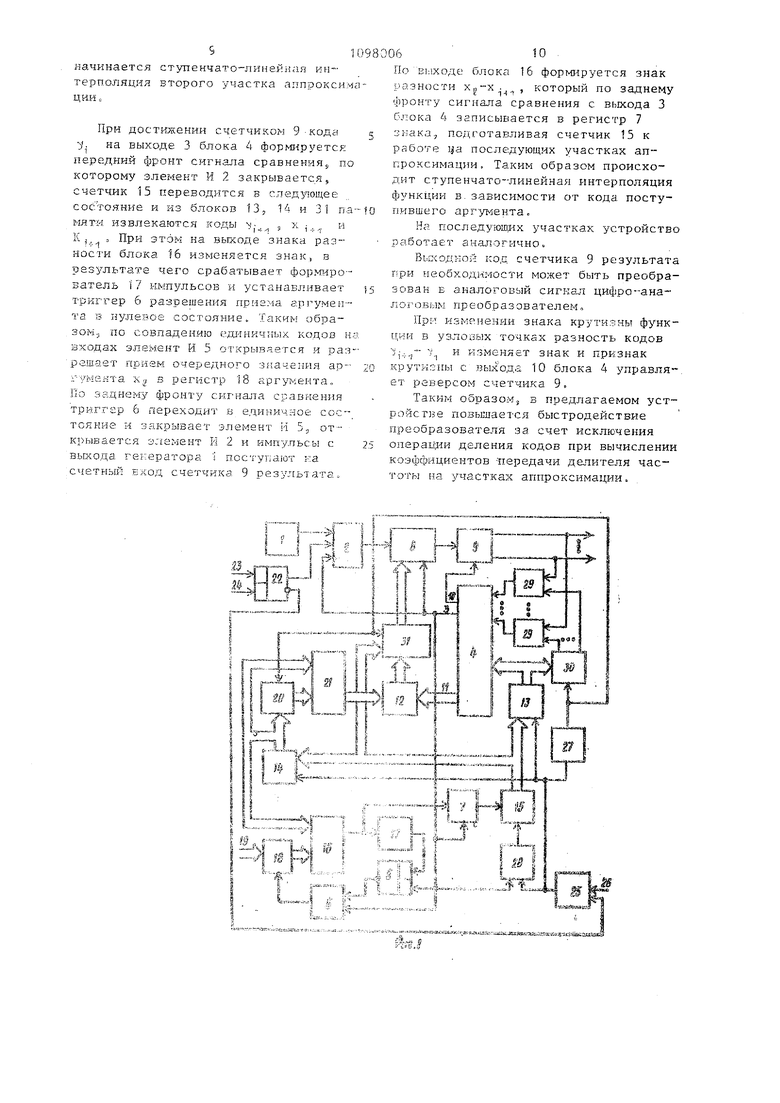

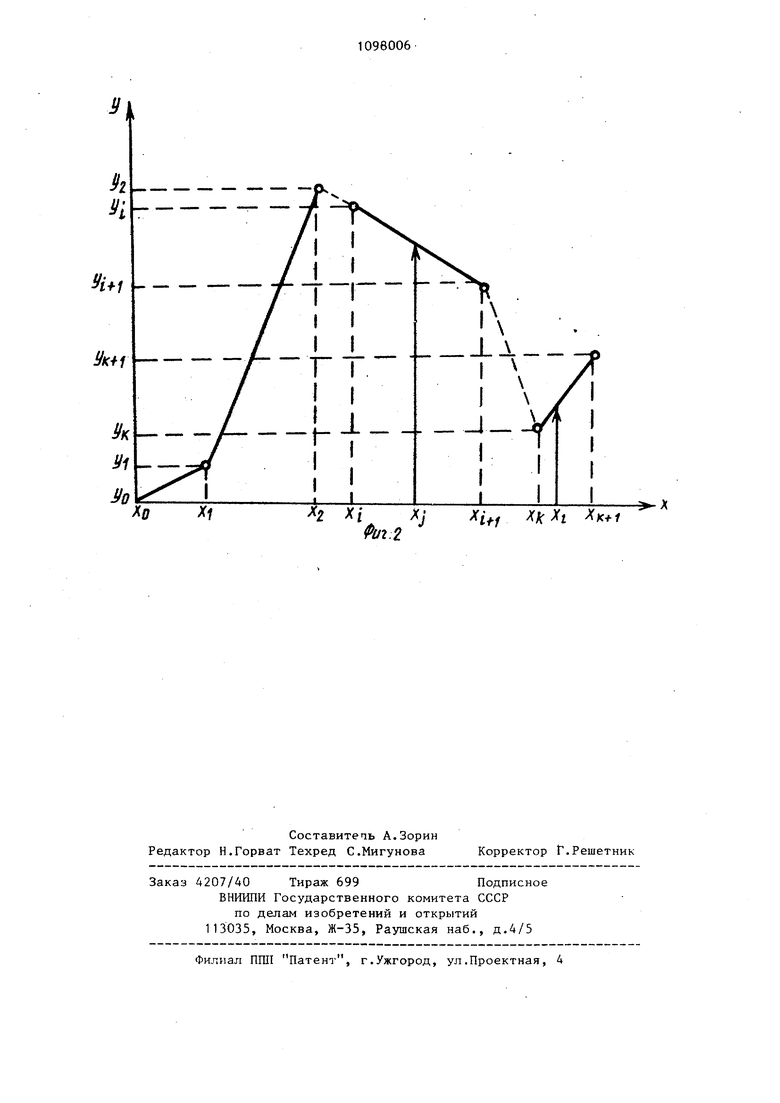

регистр аргумента,блок вычитания аргумента, формирователь импульсов,триггер разрешения приема аргумента, знаковый регистр и реверсивный счетчик адреса, причем выход генератора SQ импульсов подключен к первому входу первого элемента И, второй вход которого соединен с выходом сравнения блока вычитания ординат, первым входом второго элемента И, входом уста- 55 новки в ноль триггера разрешения приема аргумента и входом синхронизации знакового регистра, выход первого элеферный регистр, элемент ИЛИ, группа элемента ИЛИ и триггер выбора режима, вход установки в единицу которого соединен с управляющим входом режима преобразования, вход установки в ноль триггера выбора режима соединен с управляющим входом режима записи преобразователя, прямой и инверсный выходы триггера выбора режима соединены соответственно с третьим входом первого элемента И и первым входом третьего элемента И, второй вход которого соединен с входом запимента И соединен с сигнальным входом управляемого делителя частоты, подключенного выходом к счетному входу реверсивного счетчика результата, выход которого соединен с выходом преобразователя, вход управления реверсом реверсивного счетчика результата соединен с выходом знака .разности блока вычитания ординат, выход кода разности Которого соединен с входом кода делимого блока деления, вход уменьшаемого блока вычитания ординат соединен с выходом блока памяти узловых значений ординат, под|Ключенного адресным входом к адресному входу бло15а памяти узловых значений абсцисс и выходу реверсивного счетчика адреса, вход управления реверсом которого соединен с выходом знакового регистра, подключенного информационным входом к выходу знака разности блока вычитания аргумента и входу формирователя импульсов, выход которого подключен ко входу установки в единицу триггера разрешения приема аргумента, инверсный выход которого соединен со вторым входом второго элемента И, подключенного выходом к входу синхронизации регистра аргумента, информационный вход которого соединен со входом ввода аргумента преобразователя, выход регистра аргумента соединен с входом уменьшаемого блока вычитания аргумента, вход вычитаемого которого подключен к выходу блока памяти узловых значений абсцисс, информационному входу первого буферного регистра и входу уменьшаемого блока вычитания абсцисс, вход вычитаемого которого соединен с выходом первого буферного регистра, выход блока вычитания абсцисс соединен со входом кода делителя блока деления, дополнительно введены третий элемент И, элемент задержки, блок памяти коэффициентов наклона, второй буси преобразователя, выход третьего элемента И соединен со стробирующим входом записи .блока памяти узловьпх значений ординат и абсцисс, входом элемента задержки и первым входом элемента ИЛИ, подключенного вторьм входом к выходу сравнения блока вычи тания ординат, выход элемента ИЛИ подключен к счетному входу реверсивного счетчика адреса, вход вычитаемо го блока вычитания ординат соединен с выходами элементов ИЛИ группы, пер вые входы которых соединены с выходами соответствующих разрядов реверсивного счетчика результата,вторые входы элементов ИЛИ группы соединены с выходами соответствующих разрядов второго буферного регистра, информацион ный вход которого соединен с выходом блока памяти узловых значений ординат, вход синхронизации второго буферного регистра соединен с выходом элемента задержки, входом синхронизации первого буферного регистра и стро бирующим входом записи блока памяти коэффициентов наклона, подключенного адресным входом к выходу реверсивного счетчика адреса, информационный вход и выход блока памяти ко эффициентов наклона соединены соответственно с выходом блока деления и управляющим входом управляемого де лителя частоты, стробирующий вход ко торого соединен с выходом сравнения блока вычитания ординат На фиг.1 представлен преобразователь, блок-схема, на фиг.2 - график, поясняющий работу преобразователя. Цифровой функциональный преобразо ватель содержит генератор импульсов 1, элемент И 2, выход сравнения 3 блока вычитания ординат 4, элемент И триггер 6 разрешения приема аргумента, знаковый регистр 7, управляем1 1й делитель частоты 8, реверсивный счет чик результата 9, выход 10 знака раз ности и выход кода 11 блока 4 вычита ния ординат, блок деления 12, блок памяти 13 узловых значений ординат, блок памяти 14 узловых значений абсцисс, реверсивный счетчик адреса 15, блок вычитания аргумента 16, формиро вателя импульсов 17, регистр, аргумен та 18, вход аргумента 19, первый буферный регистр 20, блок вычитания аб цисс 21, триггер выбора режима 22, входы управления преобразователя 23 24, элемент И 25, вход записи преобразователя 26, элемент задержки 27, элемент ИЛИ 23, группа элементов ИЛИ 29, второй буферный регистр 30, блок памяти коэффициентов наклона 31. Преобразователь работает в двух релшмах: записи и преобразования. При работе преобразователя в режиме записи по входу 24 на вход установки в ноль триггера 22 выбора режима подается сигнал, переводящий триггер 22 в нулевое состояние. Таким образом, импульсы с выхода генератора 1 импульсов не поступают на счетный вход счетчика 9. В исходном состоянии регистр 18 аргумента, буферные 20 и 30 регистры, знаковый 7 регистр и счетчики 9 и 15 обнулены, а на информационные входы блоков 13 и 14 памяти поступает нулевой код. По коду счетчика 15 адреса осуществляется опрос адресов блоков 13, 14 и 31 памяти ординат, абсцисс и коэффициента наклона соответственно, причем нулевое значение знакового 7 регистра обуславливает режим суммирования счетчика 15, а единичное - резким вычитания. Запись кодовв блоки 13, 14 и 31 памяти осуществляется при подаче по шине 26 импульсной команды запись. По совпадению команды запись, поступающей по шине 26 на вход элемента И 25, и высокого потенциала с инверсного выхода триггера 22 выбора режима, на выходе элемента И 25 формируется импульсный сигнал записи, по переднег фронту которого в нулевые ячейки блоков 13 и 14 памяти заносится нулевой код. По заднему фронту сигнала записи с выхода эле- мента И 25 в счетчике 15 устанавливается код адреса первых ячеек блоков 13 и 14 памяти. При подаче очередной команды запись по шине 26 в первые ячейки памяти 13 и 14 заносятся коды ординаты и абсциссы х первой узловой точки. При этом блоки 4 и 21 вычитания ординат и абсцисс вычисляют разность кодов между,поступившим (из блоков 13 и 14 памяти) и предыдущим (из буферных 30 и 20 регистров) значениями ординат и абсцисс соответственно. Блок 12 деления определяет коэ ициент наклона первого участка аппроксимации, По задержанному элементом задержки 26 на время, ; 1еобходимое для вычисления коэффициента наклона, переднему фронту сигнала записи в первую ячейку блока 31 памяти коэффициентов наклона заносится код коэффициента наклона первого участка аппроксимации. По заднему фронту сигнала записи счетчик 15 адреса переводится в следующее состояние, подготавливая прием кодов ординаты и абсциссы Х2 второй узловой точки в блоки 13 и 14 памяти. По заднему фронту задержанного сигнала записи производится запись кодов ординаты и абсциссы х из блоков 13 и 14 памяти в буферные 30 и 20 регистры соответственно. Затем по очередной запись, посту пающей по шине 26 на вход элемента. И 25, осуществляется запись кодов ординаты 2 и абсциссы х,, второй узлевой точки в блоки 13 и 14 памяти и перевод счетчика 15 в следующее состояние. В блоке Т2 деления определяется коэффициент наклона второго участка аппроксимации К,, , 2 Xj-x который по переднему фронту задержан ного сигнала записи заносится во вто рую ячейку блока 31 памяти коэффициентов наклона. Таким образом, при за несении параллельных кодов ординат и абсцисс по импульсной команде запись осуществляется автоматическое |вычисление коэффициентов наклона аппроксимирующих участков и запоминание их в блоке 31 памяти коэффициент наклона. При работе преобразователя в режи ме преобразования по шине 23 на устй новочный вход триггера 22 выбора режима подается сигнал, переводящий его в единичное состояние. При этом элемент И 25 закрывается,блокируя прохождение и тульсной команды запись на блоки 13, 14 и 31 памяти В исходном состоянии регистр 18 аргумента, буферные 20 и 30 регистры знаковый 7 регистр, триггер 6 разрешения приема аргумента, счетчики 9 и 15 обнулены. Таким образом, по нулевому коду счетчика 15 из нулевой яче ки блока 13 памяти извлекается нулев код и на выходе 3 блока 4 вычитания формируется передний фронт сигнала сравнения. Сигнал сравнения с выхода 3 блока 4 поступает на, вход элемента И 2, закрывая его на время установки коэффициента деления делителя 8 частоты, на управляющий вход делителя 8 частоты, разрешая установку коэффициента передачи, на вход синхронизации регистра 7 знака, разрешая передачу знака управляющего реверсом счетчи-ка 15, на вход элемента И 5, разрешая прием кода первого значения аргумента XJ, и на счетный вход счетчика 15, переводя его в следующее состояние. По коду счетчика 15 из блоков 13, 14 и 31 памяти извлекаются коды ординаты , , абсциссы х и коэффициента наклона К первого участка аппроксимации. При этом в блоке 16 вычитания формируется знак разности кодов аргумента X. и абсциссы х с выхода блока 14 памяиИ; по сигналу сравнения с выхода 3 блока , в управляемый делитель 8 частоты заносится коэффициент передачи К, соответствующий первому участку аппроксимации, с выхода блока 31 паьшт.- После пост гпления на первый вход блока 4 кода ординаты f первого участка аппроксимации с выхода блока 13 памяти на выходе 3 блока 4 вырабатывается задний фронт сигнала сравнения, задержанный на время, необход55мое для установки коэффициента передачи в делителе 8 частоты. По заднему фронту сигнала сравнения открывается элемент И 2 и импульсы с выхода генератора импульсов 1 поступают на счетный вход реверсивного счетчика 9. По заднему фронту сигнала сравнения триггер 6 разрешения приема аргумента переводится в единичное состояние, закрывая элемент И 5 и запрещая прием очередного арглмента до момента отработки поступающего аргумента х ., Таким образом происходит ступенчато-линейная интерполяция функции на первом интервале аппроксимации, причем частота импульсов с выхода генератора 1, поступающая на вход счетчика 9, определяется коэффициентом деления делителя 8 частоты. При совпадении кода счетчика 9 и кода на выходе 3 сравнения блока 4 формируется очередной импульсный сигнал, по переднему фронту которого элемент И 2 закрывается, счетчик 15 переводится в следующее состояние и из блоков 13, 14 и 31 памяти извлекаются коды ординаты Vj , абсциссы х и коэффициента наклона К2 второго участка аппроксимации. В делитель 8 частоты заносится коэффициент передачи второго участка аппроксимации и начинается ступенчато-линейная интерполяция второго участка аппроксим При достижении счетчиком 9-кода j. яа выходе 3 блока 4 формируется передний фронт сигн,ала сравнения., п которому злемект И 2 закрывается, счетчик 15 переводится в состояние и из блоков 13, 14 и 31 па мят-и извлекаются коды NJ, j... х, и К; При этом на выходе знака разности блока 16 изменяется знак, в результате чего срабатывает формирователь (7 импульсов и устанавливает тркггер 6 разрешения приема аргумента в нулевое состояние. Таким образом., по совпадению ед -Енич -1Ых кодов я входах элемент И 5 открывается и раз решает прием очередного значения аргумента Xjf в регистр 18 аргу ;ента. По заднему фронтз сигнала сравнения тояние и закрывает элемент И

- Й 5

S l.

Ff l-1/i

.:.v,,,-i4 .ff :j 1I J I f

Iт ;-.«.«..:;. ij .,I . 11 .„,

1ВI и„„.| H,,.Jl . L.,,,. у

ч: ;---: -.-. ,,-, ,. .. , ... .::S-j- SS oiSSEi:

Щ / if

...i .f i F

- .-и:: Sti-ia i gj-ris-jiTJii- iatiiS 6 10 По Е1:1ходе блока 16 форг-оируется знак разности х,,-х.|, который по заднему фронту сигнала сравнения с выхода 3 -блока 4 записывается в регистр 7 siiU-iKa., под-готавливая счетчик 15 к работе ца последующих участках аппроксимации. Таким образом происходит ступенчато-линейная интерполяция функции в.зависимости от кода поступившего аргукента. На последующих участках устройство работает аналогично. Въа одной код счетчика 9 результата необходимости может быть преобразован Б аналоговый сигнал цифро--ана логчзвым преобразователем. При изменении знака крутизнь функции в узловых точках разность кодов j;,.,- v и изменяет знак и признак крутизны с выхода 10 блока 4 управля-. ет реверсом счетчика 9, Таким образом, в предлагаемом уст ройст)зе повышается быстродействие преобразователя за счет исключения операьгии деления кодов при вычислении коэффициентов - передачи делителя частоты на участках аппроксимации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для функционального преобразования цифровых сигналов | 1979 |

|

SU864293A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3322832/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-15—Публикация

1983-02-04—Подача