(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1981 |

|

SU982002A1 |

| Множительно-делительное устройство | 1981 |

|

SU1015373A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU310257A1 |

| Частотно-импульсное вычислительное устройство | 1980 |

|

SU881744A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| Устройство для перемножения двух частотно-импульсных сигналов | 1979 |

|

SU920723A1 |

I

Изобретение относится к автоматике и вычислительной технике и может найти применение для выполнения множительно-делительных операций над сигналами, представленными в цифровой форме.

Известно множительно-делительное устройство, содержащее генератор импульсов, элемент И, триггер, делитель частод-ы, блок преобразования кодов, счетчик, дешифратор нуля и управляемый делитель частоты на дробный коэффициент 1.

Известно также множительно-делительное устройство, содержащее генератор импульсов, элементы И, триггер, делители частоты, счетчик и блок сравнения кодов 2.

Недостаток этих устройств - пониженное быстродействие.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является множительно-делительное устройство, содержащее двухканальный преобразователь код-частота, подключенный первым входом к щине ввода кода делителя, а выходами - к первым входам первого и второго элементов И, вторые входы которых соединены с выходом триггера управления, причем выход первого элем1ента И подключен к входу первого счетчика, соединенного выходом с выходной кодовой щиной устройства, а выход бторого элемента И подключен к входу второго счетчика, соединенного выходом с первым входом блока совпадения кодов, второй вход которого подключен к выходу регистра, а выход блока совпадения кодов соединен с первым установочным входом триггера управления, подключенного вторым установочным входом к щине запуска устройства, причем вход регистра и второй вход двухканального преобразователя код-частота соединены с щинами ввода кодов сомножителей делимого 31.

Время выполнения множительно-делительных операций пропорционально отнощению кода сомножителя, вводимого в регистр, к коду делителя и при значительных величинах кода этого сомножителя время вычислений оказывается также значительным.

Цель изобретения - повыщение быстродействия устройства.

Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее двухканальный преобразователь код-частота, подключенный первым входом к шине ввода кода делителя, а выходами - к первым входам первого и второго элементов И, вторые входы которых соединены с выходом триггера управления, причем выход первого элемента И подключен к входу первого счетчика, соединенного выходом с выходной кодовой шиной устройства, а выход второго элемента И подключен к входу второго счетчика, соединенного выходом с первым входом блока совпадения кодов, второй вход которого подключен к выходу регистра, а выход блока совпадения кодов соединен с первым установочным выходом триггера управления, подключенного вторым установочным входом к шине запуска устройства, дополнительно введены блок сравнения кодов и управляемый коммутатор, подключенный первым и вторым информационными входами к шинам ввода кодов сомножителей делимого, выходами - к второму входу двухканального преобразователя код-частота и к выходу-регистра, а управляющим входом - к выходу блока сравнения кодов, соединенного входами с шинами ввода кодов сомножителей делимого.

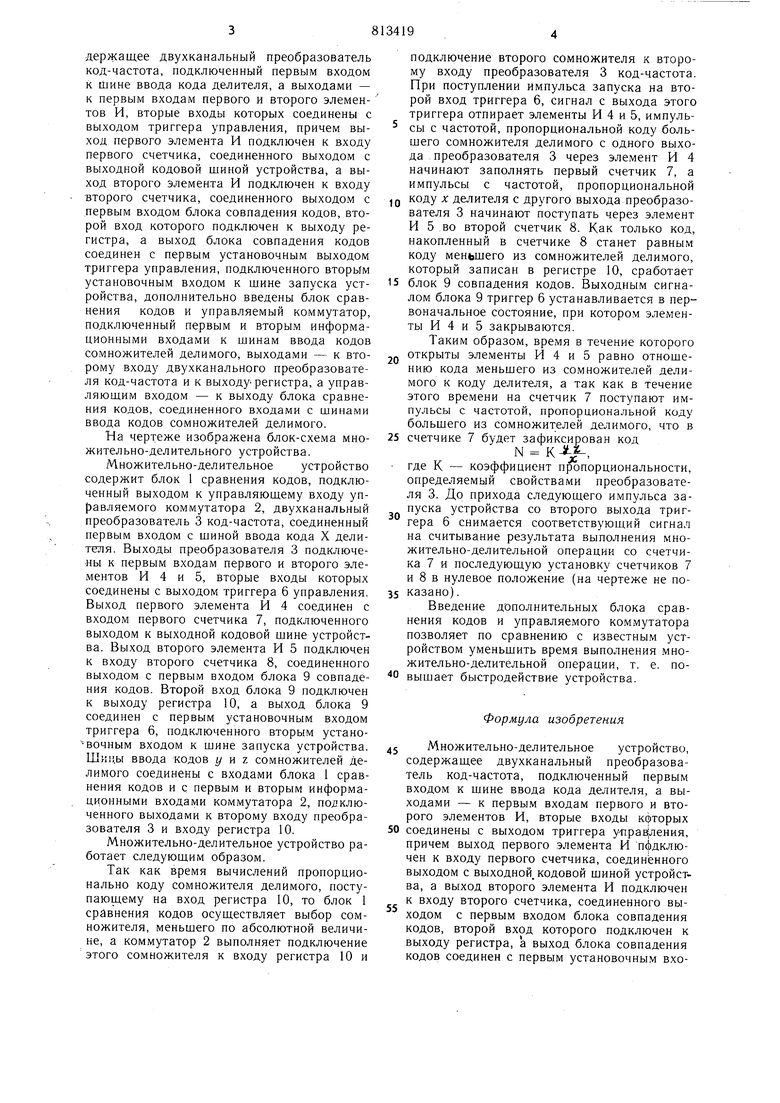

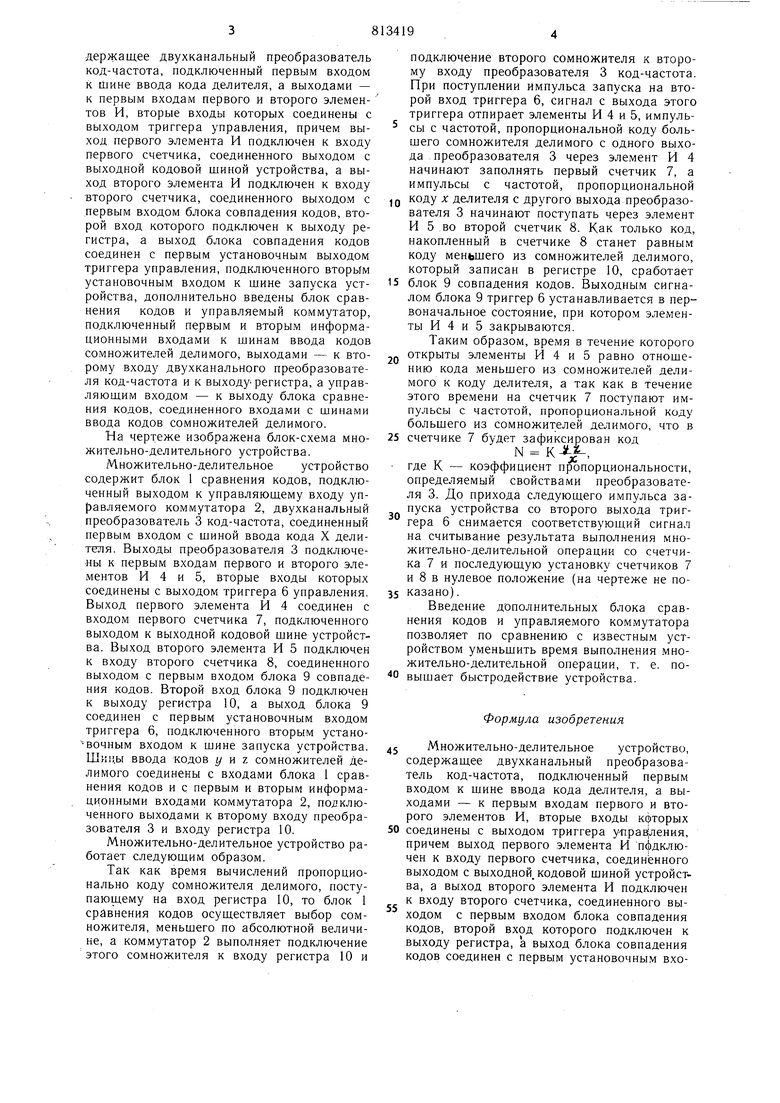

На чертеже изображена блок-схема множительно-делительного устройства.

Множительно-делительное устройство содержит блок 1 сравнения кодов, подключенный выходом к управляющему входу управляемого коммутатора 2, двухканальный преобразователь 3 код-частота, соединенный первым входом с шиной ввода кода X делителя. Выходы преобразователя 3 подключены к первым входам первого и второго элементов И 4 и 5, вторые входы которых соединены с выходом триггера 6 управления. Выход первого элемента И 4 соединен с входом первого счетчика 7, подключенного выходом к выходной кодовой шине устройства. Выход второго элемента И 5 подключен к входу второго счетчика 8, соединенного выходом с первым входом блока 9 совпадения кодов. Второй вход блока 9 подключен к выходу регистра 10, а выход блока 9 соединен с первым установочным входом триггера 6, подключенного вторым установочным входом к шине запуска устройства. Шин.ы ввода кодов у и z сомножителей Делимого соединены с входами блока 1 сравнения кодов и с первым и вторым информационными входами коммутатора 2, подключенного выходами к второму входу преобразователя 3 и входу регистра 10.

Множительно-делительное устройство работает следующим образом.

Так как время вычислений пропорционально коду сомножителя делимого, поступающему на вход регистра 10, то блок 1 сравнения кодов осуществляет выбор сомножителя, меньшего по абсолютной величине, а коммутатор 2 выполняет подключение этого сомножителя к входу регистра 10 и

подключение второго сомножителя к второму входу преобразователя 3 код-частота. При поступлении импульса запуска на второй вход триггера 6, сигнал с выхода этого триггера отпирает элементы И 4 и 5, импульсы с частотой, пропорциональной коду большего сомножителя делимого с одного выхода преобразователя 3 через элемент И 4 начинают заполнять первый счетчик 7, а импульсы с частотой, пропорциональной

коду X делителя с другого выхода преобразователя 3 начинают поступать через элемент И 5 во второй счетчик 8. Как только код, накопленный в счетчике 8 станет равным коду меньшего из сомножителей делимого, который записан в регистре 10, сработает

блок 9 совпадения кодов. Выходным сигналом блока 9 триггер 6 устанавливается в первоначальное состояние, при котором элементы И 4 и 5 закрываются.

Таким образом, время в течение которого

открыты элементы И 4 и 5 равно отношению кода меньшего из сомножителей делимого к коду делителя, а так как в течение этого времени на счетчик 7 поступают импульсы с частотой, пропорциональной коду большего из сомножителей делимого, что в

счетчике 7 будет зафиксирован код N К -,

где К - коэффициент пропорциональности, определяемый свойствами преобразователя 3. До прихода следующего импульса запуска устройства со второго выхода триггера 6 снимается соответствуюший сигнал на считывание результата выполнения множительно-делительной операции со счетчика 7 и последующую установку счетчиков 7 и 8 в нулевое положение (на чертеже не показано).

Введение дополнительных блока сравнения кодов и управляемого коммутатора позволяет по сравнению с известным устройством уменьщить время выполнения .множительно-делительной операции, т. е. повышает быстродействие устройства.

Формула изобретения

5 Множительно-делительное устройство, содержащее двухканальный преобразователь код-частота, подключенный первым входом к шине ввода кода делителя, а выходами - к первым входам первого и второго элементов И, вторые входы ксрторых

0 соединены с выходом триггера у-прайления, причем выход первого элемента И пйдключен к входу первого счетчика, соединённого выходом с выходной, кодовой щиной устройства, а выход второго элемента И подключен к входу второго счетчика, соединенного выходом с первым входом блока совпадения кодов, второй вход которого подключен к выходу регистра, а выход блока совпадения кодов соединен с первым установочным входом триггера управления, подключенного вторым установочным входом к шине запуска устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введены блок сравнения кодов и управляемый коммутатор, подключенный первым и вторым информационными входами к шинам ввода кодов сомножителей делимого, выходами - к второму входу двухканальдого преобразователя код-частота и к входу регистра, а управляющим входом - к выходу блока сравнения кодов, соединенного входами с шинами ввода кодов сомножителей делимого.

Источники информации, принятые во внимание при экспертизе

№ 310257, кл. G 06 F 7/52, 1970 (прототип).

y-z

yv

Авторы

Даты

1981-03-15—Публикация

1978-12-06—Подача