(54) ВЫЧИТАЮЩЕЕ УСТРОЙСТВО

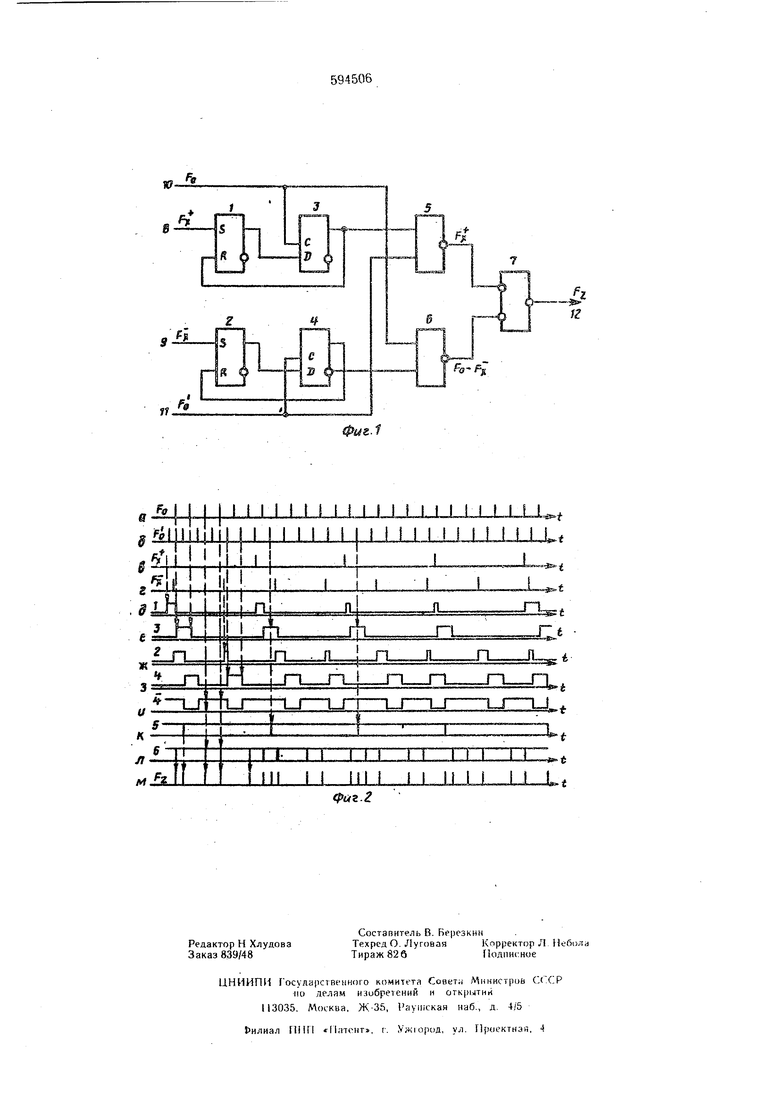

Устройство содержит RS-триггеры 1, 2 Dтриггеры 3, 4, элементы И 5, 6 и элемент ИЛИ 7.

Входные шины 8, 9 устройства соединены с S-входамн RS-триггеров 1, 2, единичные выходы которых связаны с D-входами D-триггеров 3, 4, С-входы которых подключены к шинам опорных частот 10, 1, а единичные выходы - к R-входам RS-триггеров I, 2, в свою очередь, единичный выход D-триггера 3 связан входом элемента И 5, второй вход которого подключен к шине второй опорной частоты 11, нулевой же выход D-триггера 4 соединен с входом элемента И 6, второй вход которого подключен к шине первой опорной частоты 10, а выходы обоих элементов И 5, 6 подключены к входам элемента ИЛИ 7, выход которого является выходом 12 устройства.

Схемы на триггерах 1, 3 и 2, 4 представляю,т собой схемы синхронизации входных импульсов FX и ft импульсами равных опорных частот FO и , сдвинутых на полпериода относительно друг друга.

Вычитающее устройство работает следующим образом.

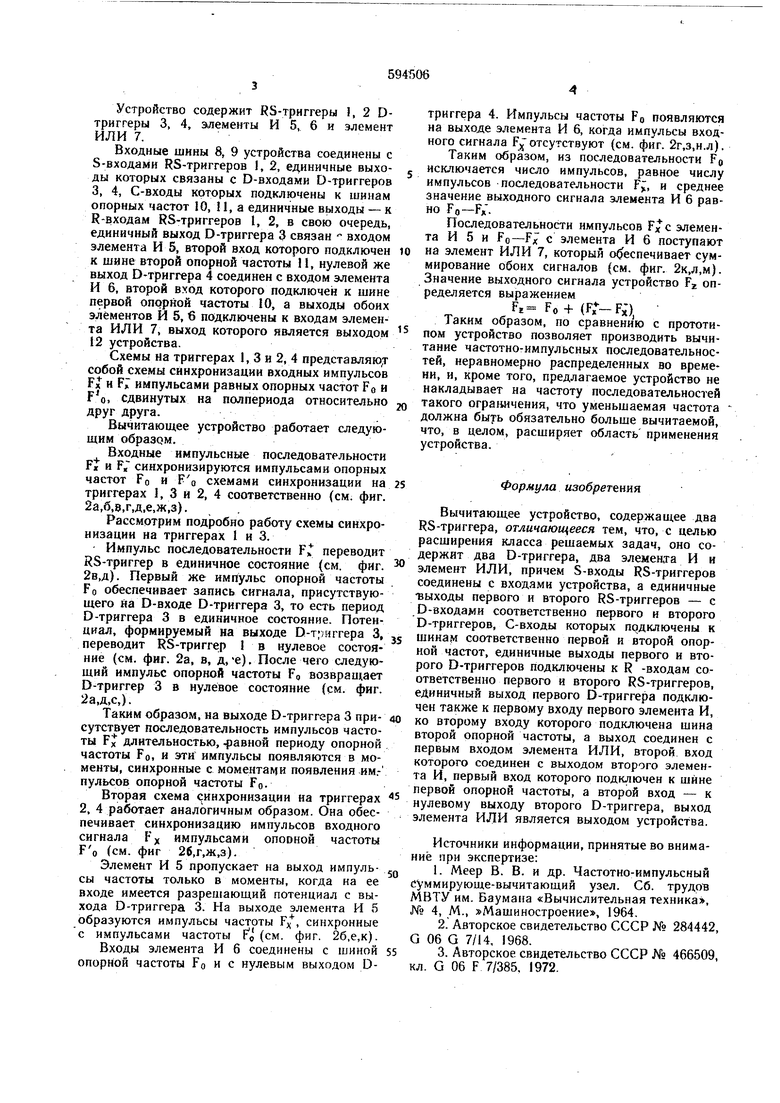

Входные импульсные последовательности pj и F, синхронизируются импульсами опорных частот FO и Fo схемами синхронизации на триггерах 1, 3 и 2, 4 соответственно (см. фиг. 2а,б,8,г,д,е,ж,з)..

Рассмотрим подробно работу схемы синхронизации на триггерах I и 3.

Импульс последовательности F переводит RS-триггер в единичное состояние (см. фиг. 2в,д). Первый же импульс опорной частоты FO обеспечивает запись сигнала, присутствующего на D-входе D-триггера 3, то есть период D-триггера 3 в единичное состояние. Потенциал, формируемый на выходе D-триггера 3, переводит RS-триггер 1 в нулевое состояние (см. фиг. 2а, в, д,е). После чего следующий импульс опорной частоты FO возвращает D-триггер 3 в Нулевое состояние (см. фиг. 2а,д,сЛ.

Таким образом, на выходе D-триггера 3 присутствует последовательность импульсов частоты FX длительностью, .равной периоду опорной частоты FO, и эти импульсы появляются в моменты, синхронные с моментами появления им.пульсов опорной частоты FQ.

Вторая схема синхронизации на триггерах 2, 4 работает аналогичным образом. Она обеспечивает синхронизацию импульсов входного сигнала F импульсами опооной частоты Fo (см. фиг 2б,г,ж,з).

Элемент И 5 пропускает на выход импульсы частоты только в моменты, когда на ее входе имеется разрешающий потенциал с выхода О-триггера 3. На выходе элемента И 5 образуются импульсы частоты F/, синхронные с импульсами частоты Fo (см. фиг. 2б,е,к).

Входы элемента И 6 соединены с шиной опорной частоты FO и с нулевым выходом Dтриггера 4. Импульсы частоты FO появляются на выходе элемента И 6, когда импульсы входного сигнала F jотсутствуют (см. фиг. 2г,з,н.л).

Таким образом, из последовательности FO исключается число импульсов, равное числу импульсов последовательности , н среднее значение выходного сигнала элемента И 6 равно FO-FX.

Последовательности импульсов F;Jc элемента И 5 и FO-FX с элемента И 6 поступают на элемент ИЛИ 7, который обеспечивает суммирование обоих сигналов (см. фиг. 2к,л,м). Значение выходного сигнала устройство Fj определяется выражением

FE Fo-f (F;-FX)

Таким образом, по сравнению с прототипом устройство позволяет производить вычитание частотно-импульсных последовательностей, неравномерно распределенных во времени, и, кроме того, предлагаемое устройство не накладывает на частоту последовательностей такого огра1И1чения, что уменьшаемая частота должна быть обязательно больше вычитаемой, что, в целом, расширяет область применения устройства.

Формула изобретения

Вычитающее устройство, содержащее два RS-триггера, отличающееся тем, что, с целью расширения класса решаемых задач, оно содержит два D-триггера, два элемента И и элемент ИЛИ, причем S-входы RS-триггеров соединены с входами устройства, а единичные выходы первого и второго RS-триггеров - с D-входами соответственно первого и второго D-триггеров, С-входы которых подключены к шинам соответственно первой и второй опорной частот, единичные выходы первого и второго D-триггеров подключены к R -входам соответственно первого и второго RS-триггеров, единичный выход первого D-триггера подключен также к первому входу первого элемента И, ко второму входу которого подключена шина второй опорной частоты, а выход соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого подключен к шине первой опорной частоты, а второй вход - к нулевому выходу второго D-триггера, выход элемента ИЛИ является выходом устройства.

Источники информации, принятые во внимание при экспертизе:

I. Меер В. В. и др. Частотно-импульсный суммирующе-вычитающий узел. Сб. трудов МВТУ им. Баумана «Вычислительная техника, № 4, М., Машиностроение, 1964.

2.Авторское свидетельство СССР № 284442

G 06 G 7/14, 1968.

3.Авторское свидетельство СССР № 466509 кл. О 06 F 7/385. 1972.

f

$

ГО

11.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсных последовательностей | 1981 |

|

SU961120A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1986 |

|

SU1406528A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1088136A1 |

| Преобразователь частоты в напряжение | 1982 |

|

SU1095391A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Селектор нижних и верхних частот | 1985 |

|

SU1352621A1 |

M I M M I i I t I M 1 I I I M M

Fa

Авторы

Даты

1978-02-25—Публикация

1975-12-29—Подача