(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ДИАГНОСТИКИ ЛОГИЧЕСКИХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики блоков электронных вычислительных машин | 1978 |

|

SU746556A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1251085A1 |

| Устройство для диагностики блоков электронных вычислительных машин | 1976 |

|

SU650080A1 |

| ПЕРЕНОСНОЙ ПРОГРАММНО-ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2007 |

|

RU2363975C2 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Система для контроля и диагностики цифровых узлов | 1980 |

|

SU911531A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики логических узлов.

Известны устройства для проверки логических узлов построенные на определенной логике и предназначенные для проверки логических узлов, построенных на элементах той же логики.

Известно устройство для проверки блоков ЭВМ, построенное на интегральных схемах ЕСЛ логики и предназначенное для проверки логических узлов, построенных на элементах ЕСЛ логики l.

Однако это устройство не позволяет осуществить проверку блоков ЭВМ, построенных на логических элементах другой серии, например на ТТЛ схемах, хотя большинство внешних устройств, дисков, магнитных лент и т.д. и устройства управления ими содержат схемы, построенные на элементах ТТЛ логики. Для проверки ТЭЗ этих устройств, а также блоков ЭВМ, построенных на элементах ТТЛ логики, используется комплект приборов и стендов индивидуального обслуживания, что значительно, снижает ремонтопригодность ЭВМ, а также приводит к значительному удорожанию их стоимости .

Наиболее близким к предлагаемому является устройство для диагностики блоков ЭВМ 2.

Известное устройство содержит накопитель тестов,, входной регистр, регистр тестов, блок преобразовате10лей параллельного кода в последовательный, блок управления, блок сравнения-, а также регистр результата и буферный блок памяти. Причем выход накопителя тестов соединен со

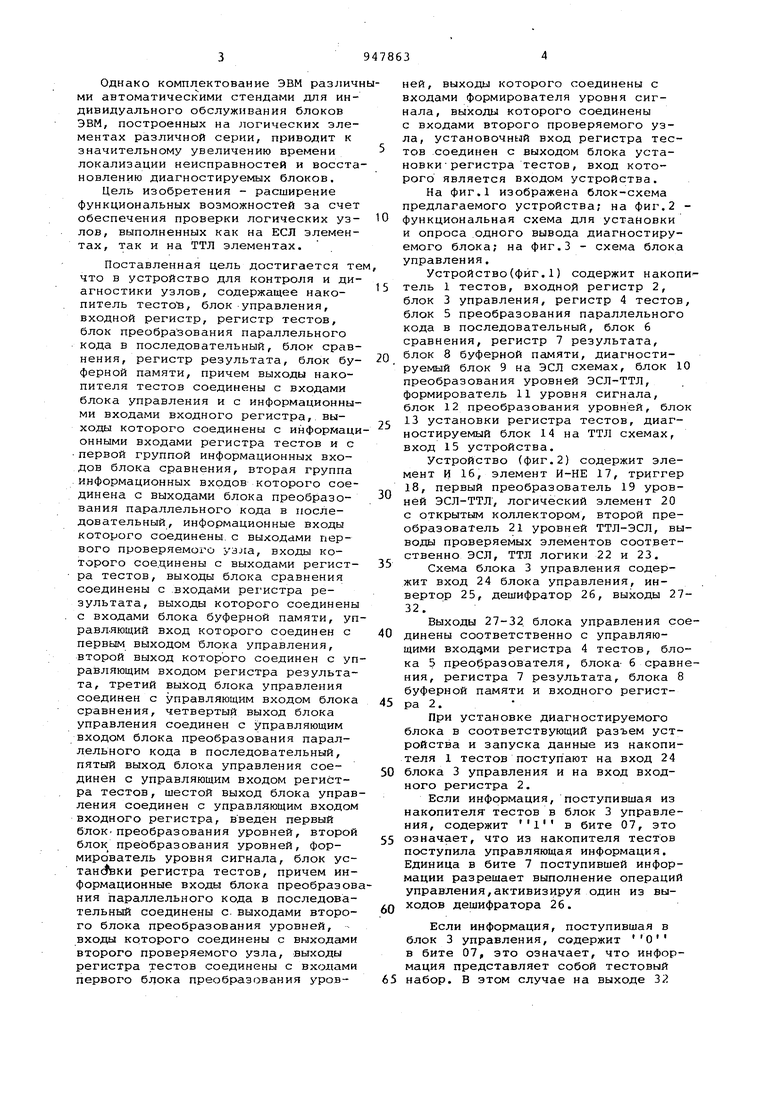

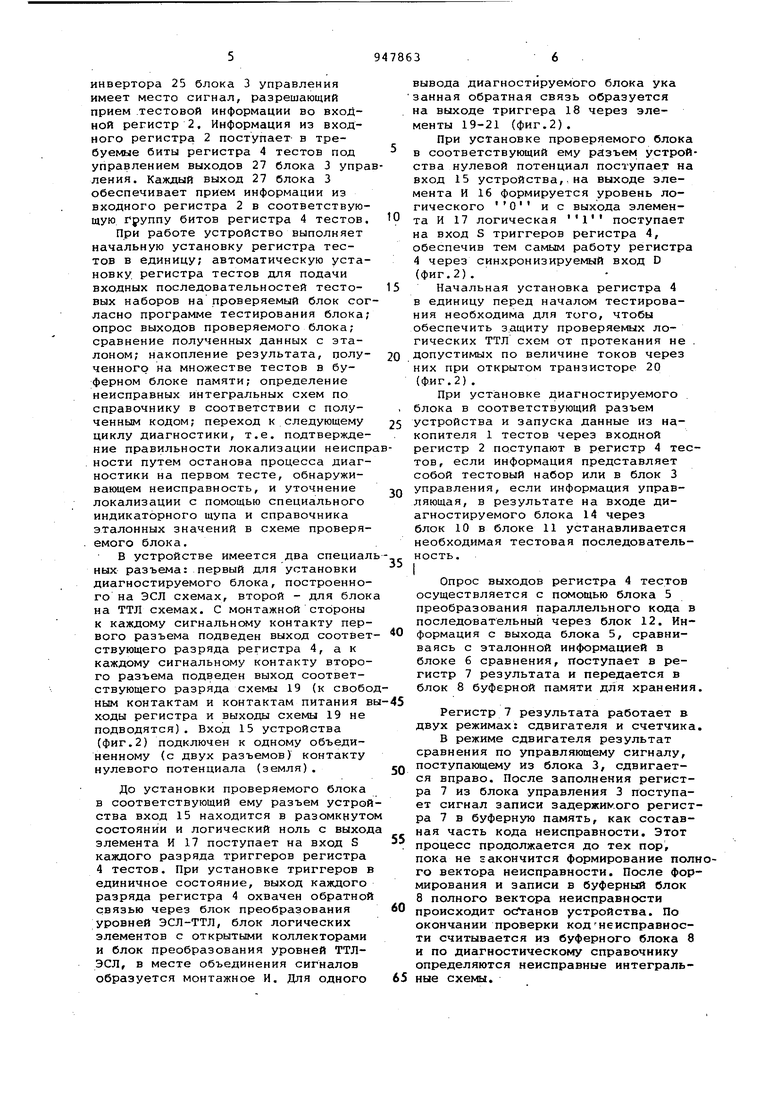

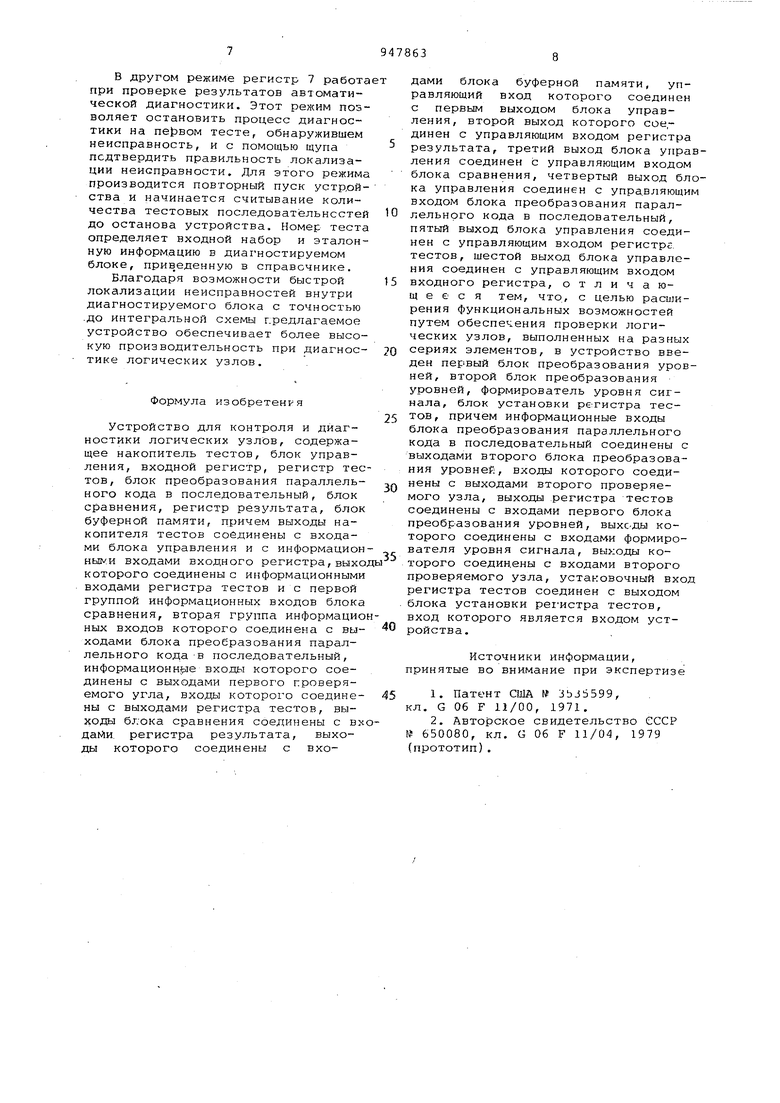

15 входами входного регистра и блока управления, выходы которого соединены с управляющими входами входного регистра, регистра тестов, блока преобразователей параллельно20го кода в последовательный, блока сравнения, регистра результата и блока буферной памяти. Здесь информация о состоянии выходов регистра тестов через преобразователь па25раллельного кода в последовательный поступает на блок для сравнения данных с эталонными, результат сравнения накапливается в регистре результата и через регистр обмена запи30сывается в буферный блок памяти. Однако комплектование ЭВМ различ ми автоматическ ими стендами для индивидуального обслуживания блоков ЭВМ, построенных на логических элементах различной серии, приводит к значительному увеличению времени локализации неисправностей и восста новлению диагностируемых блоков. Цель изобретения - расширение функциональных возможностей за счет обеспечения проверки логических узлов, выполненных как на ЕСЛ элементах, так и на ТТЛ элементах. Поставленная цель достигается те что в устройство для контроля и диагностики узлов, содержащее накопитель тестов, блок управления, входной регистр, регистр тестов, блок преобразования параллельного кода в последовательный, блок сравнения, регистр результата, блок буферной памяти, причем выходы накопителя тестов соединены с входами блока управления и с информационными входами входного регистра, выходы которого соединены с информаци онными входами регистра тестов и с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с выходами блока преобразования параллельного кода в последовательный, информационные входы которого соединены.с выходами первого проверяемого узла, входы которого соединены с выходами регистра тестов, выходы блока сравнения соединены с входами рехистра результата, выходы которого соединены с входами блока буферной памяти, уп равляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с уп равляющим входом регистра результата, третий выход блока управления соединен с управляющим входом блока сравнения, четвертый выход блока управления соединен с управляющим входом блока преобразования параллельного кода в последовательный, пятый выход блока управления соединен с управляющим входом регистра тестов, шестой выход блока управ ления соединен с управляющим входом входного регистра, введен первый блоКпреобразования уровней, второй блок преобразования уровней, формирователь уровня сигнала, блок устанс ки регистра тестов, причем информационные входы блока преобразов ния параллельного кода в последовательный соединены с. выходами второго блока преобразования уровней, входы которого соединены с выходами второго проверяемого узла, выходы регистра тгестов соединены с входами первого блока преобразования уровней, выходы которого соединены с входами формирователя уровня сигнала, выходы которого соединены с входами второго проверяемого узла, установочньай вход регистра тестов соединен с выходом блока установки регистра тестов, вход которого является входом устройства. На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 функциональная схема для установки и опроса одного вывода диагностируемого блока; на фиг.З - схема блока управления. Устройство(фиг.1) содержит накопитель 1 тестов, входной регистр 2, блок 3 управления, регистр 4 тестов, блок 5 преобразования параллельного кода в последовательный, блок 6 сравнения, регистр 7 результата, блок 8 буферной памяти, диагностируемый блок 9 на ЭСЛ схемах, блок 10 преобразования уровней ЭСЛ-ТТЛ, формирователь 11 уровня сигнала, блок 12 преобразования уровней, блок 13 установки регистра тестов, диагностируемый блок 14 на ТТЛ схемах, вход 15 устройства. Устройство (фиг.2) содержит элемент И 16, элемент И-НЕ 17, триггер 18, первый преобразователь 19 уровней ЭСЛ-ТТЛ, логический элемент 20 с открытым коллектором, второй преобразователь 21 уровней ТТЛ-ЭСЛ, выводы проверяемых элементов соответственно ЭСЛ, ТТЛ логики 22 и 23. Схема блока 3 управления содержит вход 24 блока управления, инвертор 25, дешифратор 26, выходы 2732. Выходы 27-32. блока управления соединены соответственно с управляющими входами регистра 4 тестов, блока 5 преобразователя, блока- б сравнения, регистра 7 результата, блока 8 буферной памяти и входного регистра 2. При установке диагностируемого блока в соответствующий разъем устройства и запуска данные из накопителя 1 тестов поступают на вход 24 блока 3 управления и на вход входного регистра 2. Если информация, поступившая из накопителя тестов в блок 3 управления, содержит в бите 07, это означает, что из накопителя тестов поступила управляющая информация. Единица в бите 7 поступившей информации разрешает выполнение операций управления,активизируя один из выходов дешифратора 26. Если информация, поступившая в блок 3 управления, содержит 0 в бите 07, это означает, что информация представляет собой тестовый набор. В этом случае на выходе 32 инвертора 25 блока 3 управления имеет место сигнал, разрешающий прием .тестовой информации во входной регистр 2, Информация из входного регистра 2 поступает- в требуемые биты регистра 4 тестов под управлением выходов 27 блока 3 упра ления. Каждый выход 27 блока 3 обеспечивает прием информации из входного регистра 2 в соответствующую группу битов регистра 4 тестов. При работе устройство выполняет начальную установку регистра тестов в единицу; автоматическую установку, регистра тестов для подачи входных последовательностей тестовых наборов на проверяемый блок сог ласно программе тестирования блока; опрос выходов проверяемого блока; сравнение полученных данных с эталоном; накопление результата, полученногр на множестве тестов в буферном блоке памяти; определение неисправных интегральных схем по справочнику в соответствии с полученным кодом; переход к следующему циклу диагностики, т.е. подтверждение правильности локализации неиспр ности путем останова процесса диагностики на первом тесте, обнаруживающем неисправность, и уточнение локализации с помощью специального индикаторного щупа и справочника эталонных значений в схеме проверяемого блока. В устройстве имеется два специал ных разъема: первый для установки диагностируемого блока, построенного на ЭСЛ схемах, второй - для блок на ТТЛ схемах. С монтажной стороны к каждому сигнальнсячу контакту первого разъема подведен выход соответ ствующего разряда регистра 4, а к каждому сигнальному контакту второго разъема подведен выход соответствующего разряда схемы 19 (к свобо ным контактам и контактам питания в ходы регистра и выходы схемы 19 не подводятся). Вход 15 устройства (фиг.2) подключен к одному объединенному (с двух разъемов) контакту нулевого потенциала (земля). До установки проверяемого блока в соответствующий ему разъем устро ства вход 15 находится в разомкнут состоянии и логический ноль с выход элемента И 17 поступает на вход S каждого разряда триггеров регистра 4 тестов. При установке триггеров единичное состояние, выход каждого разряда регистра 4 охвачен обратной связью через блок преобразования уровней ЭСЛ-ТТЛ, блок логических элементов с открытыми коллекторами и блок преобразования уровней ТТЛЭСЛ, в месте объединения сигналов образуется монтажное И. Для одного вывода диагностируемого блока ука занная обратная связь образуется на выходе триггера 18 через элементы 19-21 (фиг.2). При установке проверяемого блока в соответствующий ему разъем устройства нулевой потенциал поступает на вход 15 устройства,. на выходе элемента И 16 формируется уровень логического О и с выхода элемента И 17 логическая поступает на вход S триггеров регистра 4, обеспечив тем самым работу регистра 4 через синхронизируемый вход D (фиг.2). Начальная установка регистра 4 в единицу перед началом тестирования необходима для того, чтобы обеспечить защиту проверяемых логических ТТЛ схем от протекания не . допустимых по величине токов через них при открытом транзисторе 20 (фиг.2) . При установке диагностируемого блока в соответствующий разъем устройства и запуска данные из накопителя 1 тестов через входной регистр 2 поступают в регистр 4 тестов, если информация представляет собой тестовый набор или в блок 3 управления, если информация управляющая, в результате на входе диагностируемого блока 14 через блок 10 в блоке 11 устанавливается необходимая тестовая последовательность. Опрос выходов регистра 4 тестов осуществляется с помощью блока 5 преобразования параллельного кода в последовательный через блок 12. Информация с выхода блока 5, сравниваясь с эталонной информацией в блоке б сравнения, поступает в регистр 7 результата и передается в блок 8 буферной памяти для хранения. Регистр 7 результата работает в двух режимах: сдвигателя и счетчика. В режиме сдвигателя результат сравнения по управляющему сигналу, поступающему из блока 3, сдвигается вправо. После заполнения регистра 7 из блока управления 3 поступает сигнал записи задержимого регистра 7 в буферную память, как составная часть кода неисправности. Этот процесс продолжается до тех пор, пока не гакончится формирование полного вектора неисправности. После формирования и записи в буферный блок 8 полного вектора иенсправности происходит осЛ-анов устройства. По окончании проверки коднеисправности считывается из буферного блока 8 и по диагностическому справочнику определяются неисправные интегральные схемы. В другом режиме регистр 7 работа при проверке результатов автоматической диагностики. Этот релшм позволяет остановить процесс диагностики на тесте, обнаружившем неисправность, и с помощью щупа подтвердить правильность локализации неисправности. Для этого режима производится повторный пуск устройства и начинается считывание количества тестовых последовательностей до останова устройства. Номер теста определяет входной набор и эталонную информацию в диагностируемом блоке, прив еденную в справочнике. Благодаря возможности быстрой локализации неисправностей внутри диагностируемого блока с точностью .до интегральной схемы предлагаемое устройство обеспечивает более высокую производительность при диагностике логических узлов. Формула изобретения Устройство для контроля и диагностики логических узлов, содержащее накопитель тестов, блок управления, входной регистр, регистр тес тов, блок преобразования параллельного кода в последовательный, блок сравнения, регистр результата, блок буферной памяти, причем выходы накопителя тестов соединены с входами блока управления и с информацион ныг.и входами входного регистра, выхо которого соединены с информационными входами регистра тестов и с первой группой информационных входов блока сравнения, вторая группа информацио ных входов которого соединена с выходами блока преобразования параллельного кода-в последовательный, информационн}ле входы которого соединены с выходами первого проверяемого угла, входы которого соединены с выходами регистра тестов, выходы блока сравнения соединены с вх дайи. регистра результата, выходы которого соединены с входами блока буферной памяти, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с управляющим входом регистра результата, третий выход блока угтравления соединен с управляющим входом блока сравнения, четвертый выход блока управления соединен с упра.вляющим входом блока преобразования параллельного кода в последовательный, пятый выход блока управления соединен с управляющим входом регистра, тестов, шестой выход блока управления соединен с управляющим входом входного регистра, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения проверки логических узлов, выполненных на разных сериях элементов, в устройство введен блок преобразования уровней, второй блок преобразования уровней, формирователь уровня сигнала, блок установки ре:гистра тестов, причем информационные входы блока преобразования параллельного кода в последовательный соединены с выходами второго блока преобразования уровней, входы которого соединены с выходами второго проверяемого узла, выходы регистра тестов соединены с входами первого блока преобразования уровней, выхс-ды которого соединены с входами формирователя уровня сигнала, выходы которого соединены с входами второго проверяемого узла, установочный вход регистра тестов соединен с выходом блока установки регистра тестов, вход которого является входом устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3bJ5599, кл. G 06 F 11/00, 1971, 2.Авторское свидетельство СССР № 650080, кл, G 06 F 11/04, 1979 (прототип),

Авторы

Даты

1982-07-30—Публикация

1980-04-25—Подача