Изобретение относится к области вычислительной и контрольно-измерительной техники,конкретнее к системам автоматического контроля функционирования цифровых узлов электронной ап- ратуры

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля объектов с асинхронным приемом информации.

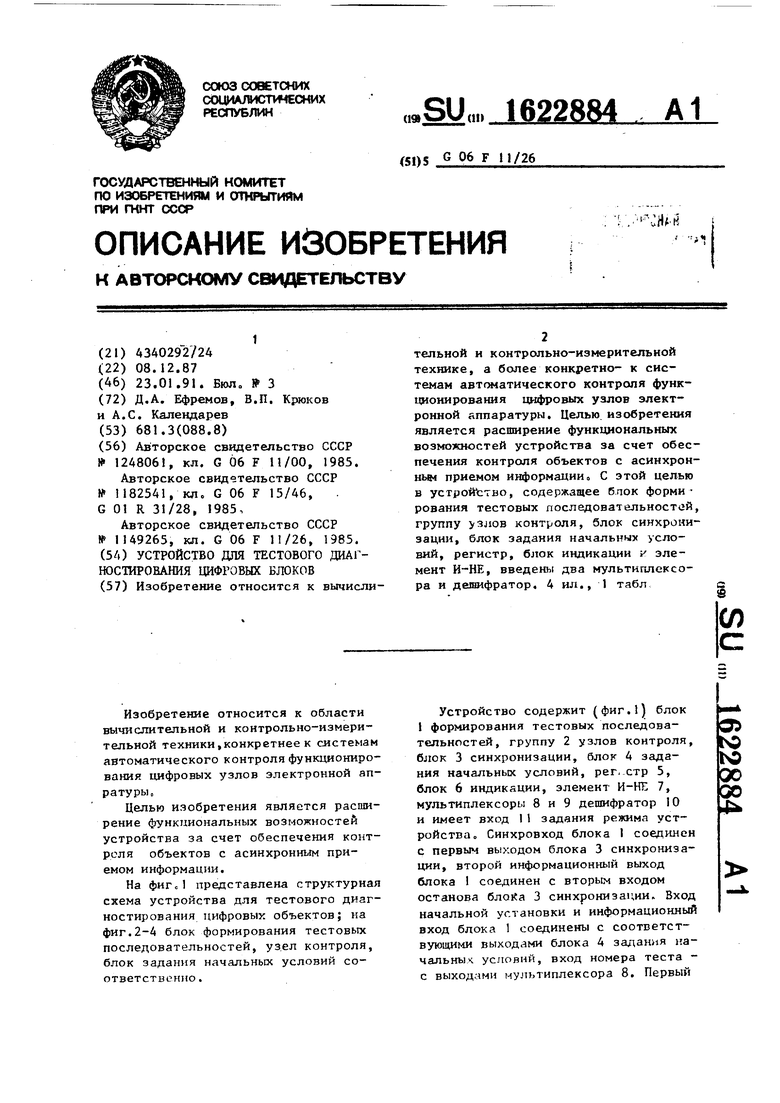

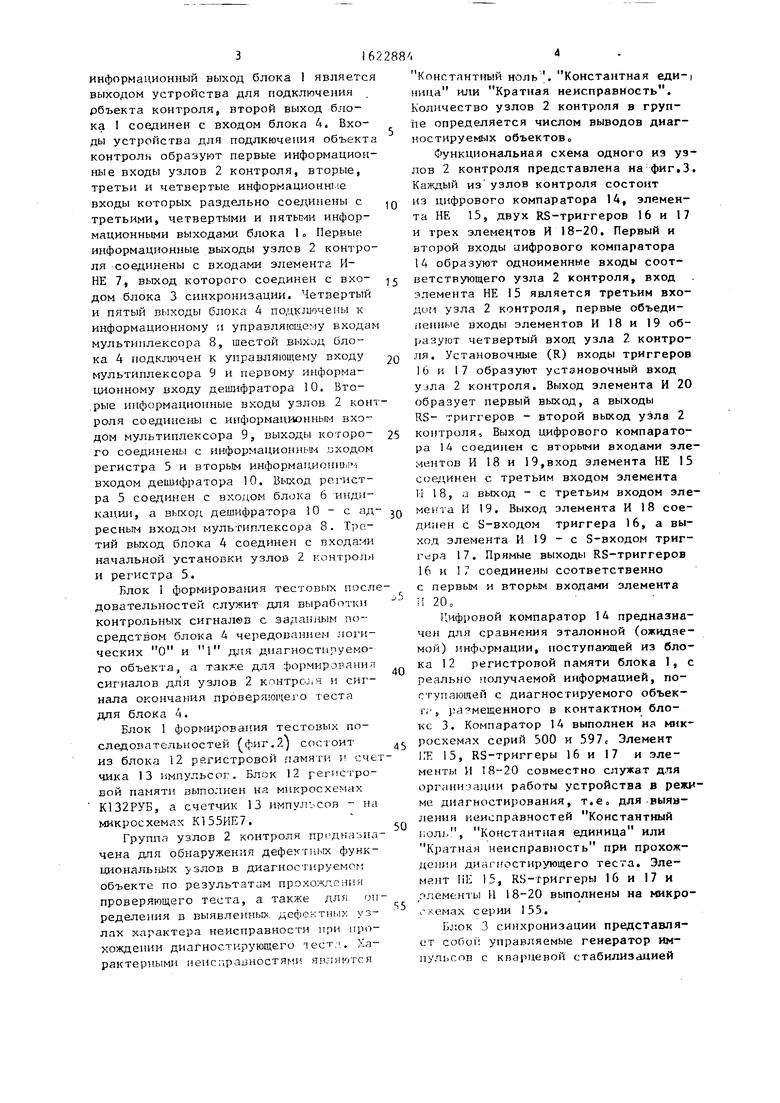

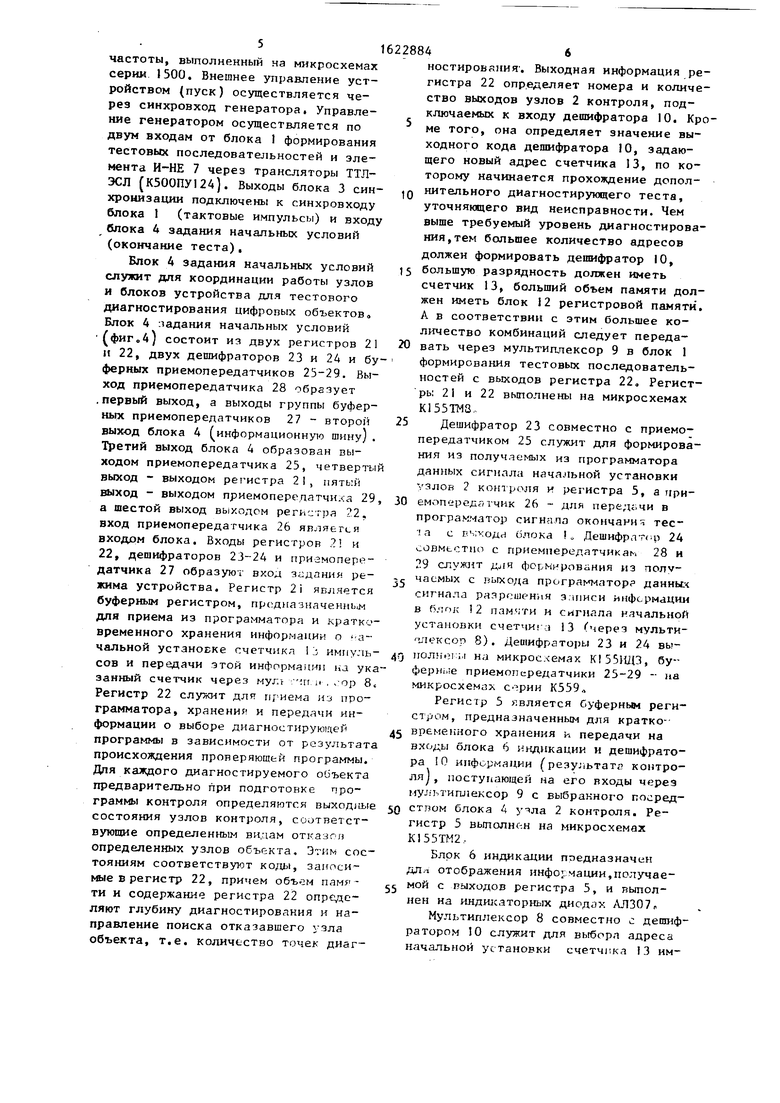

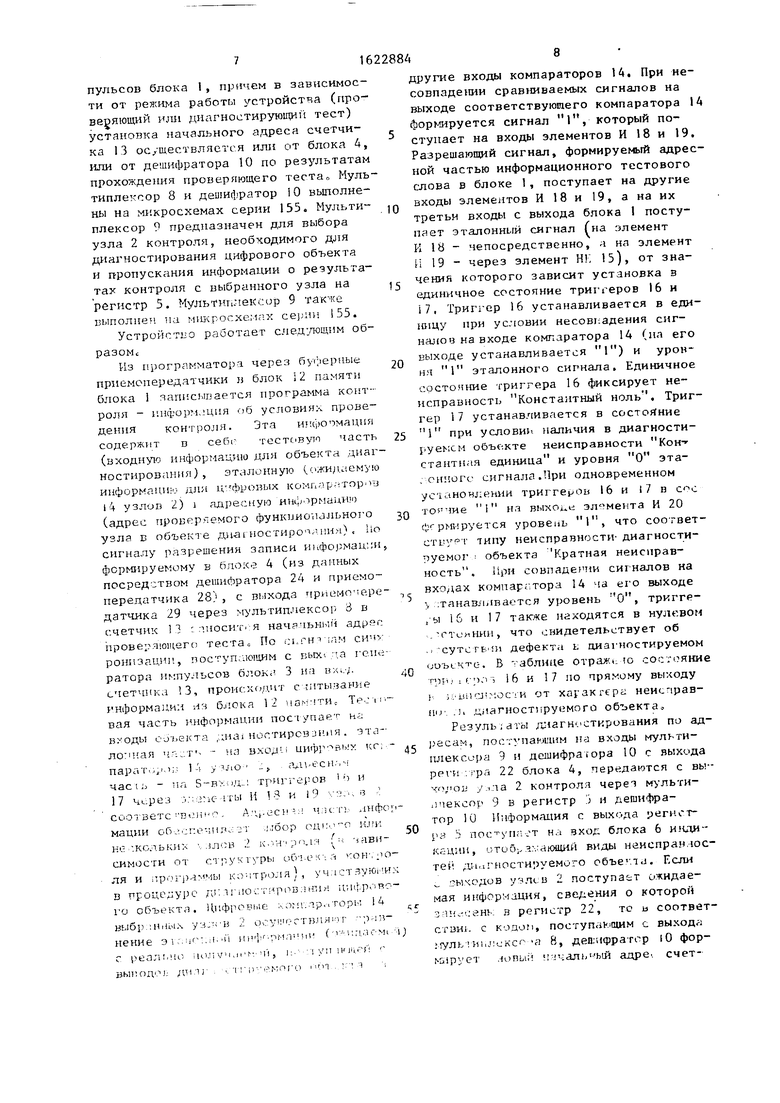

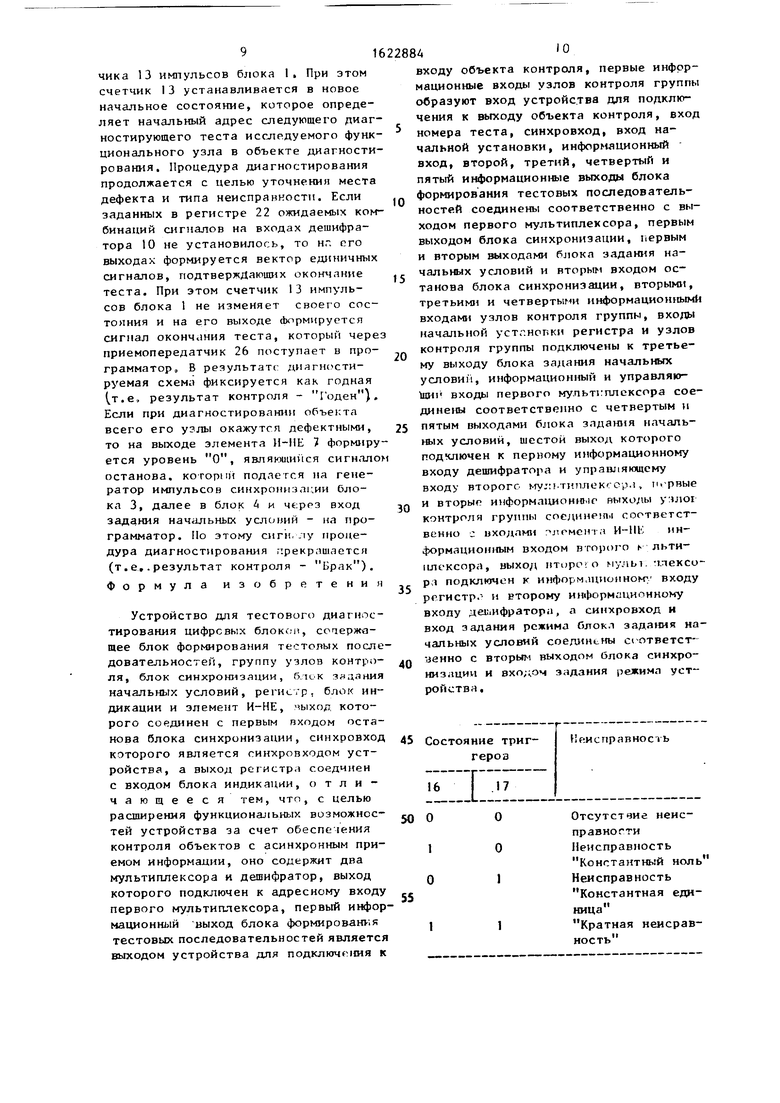

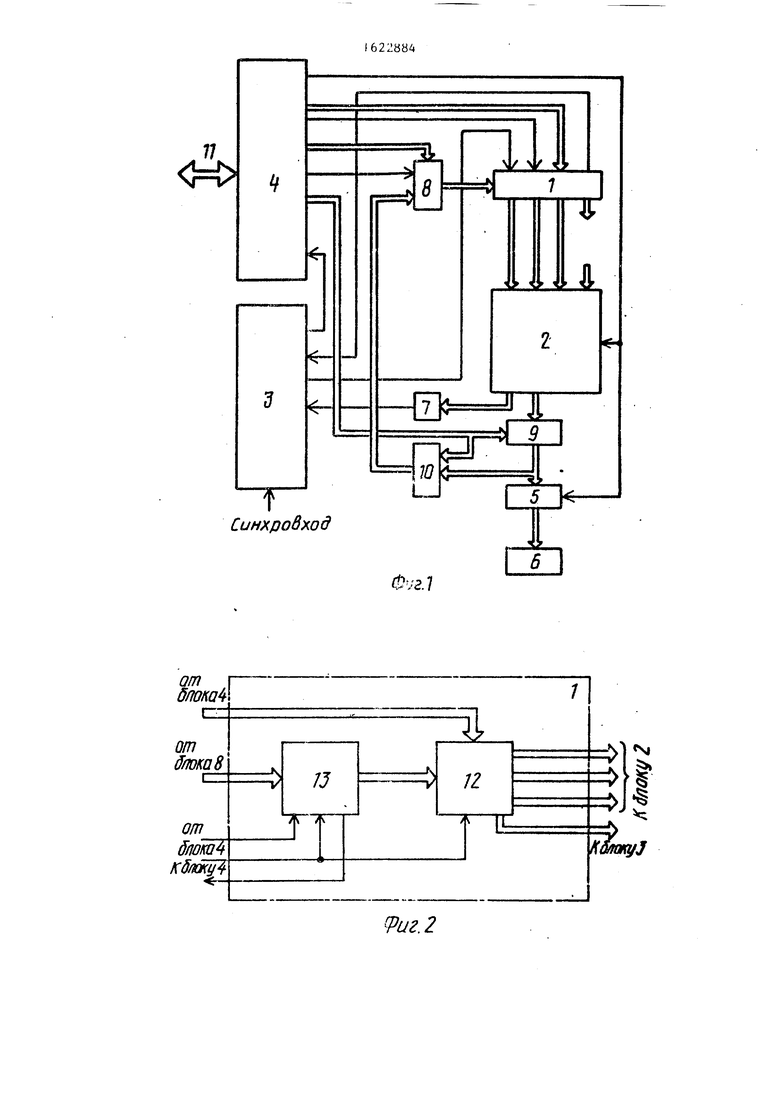

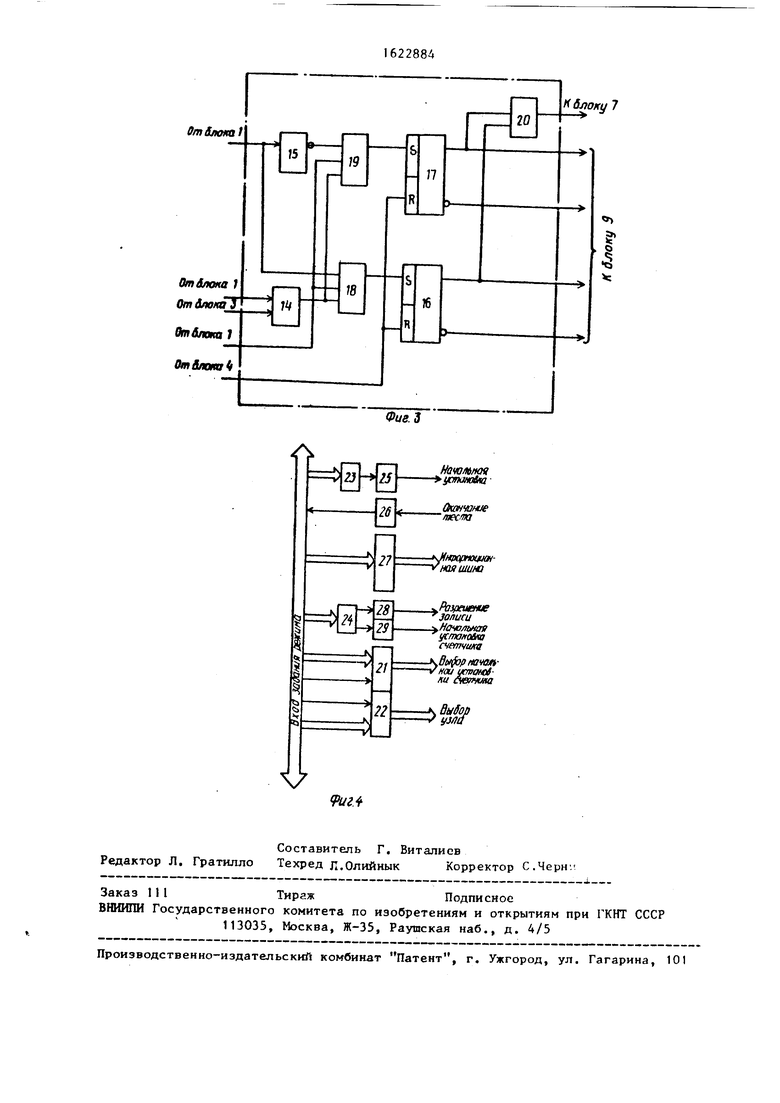

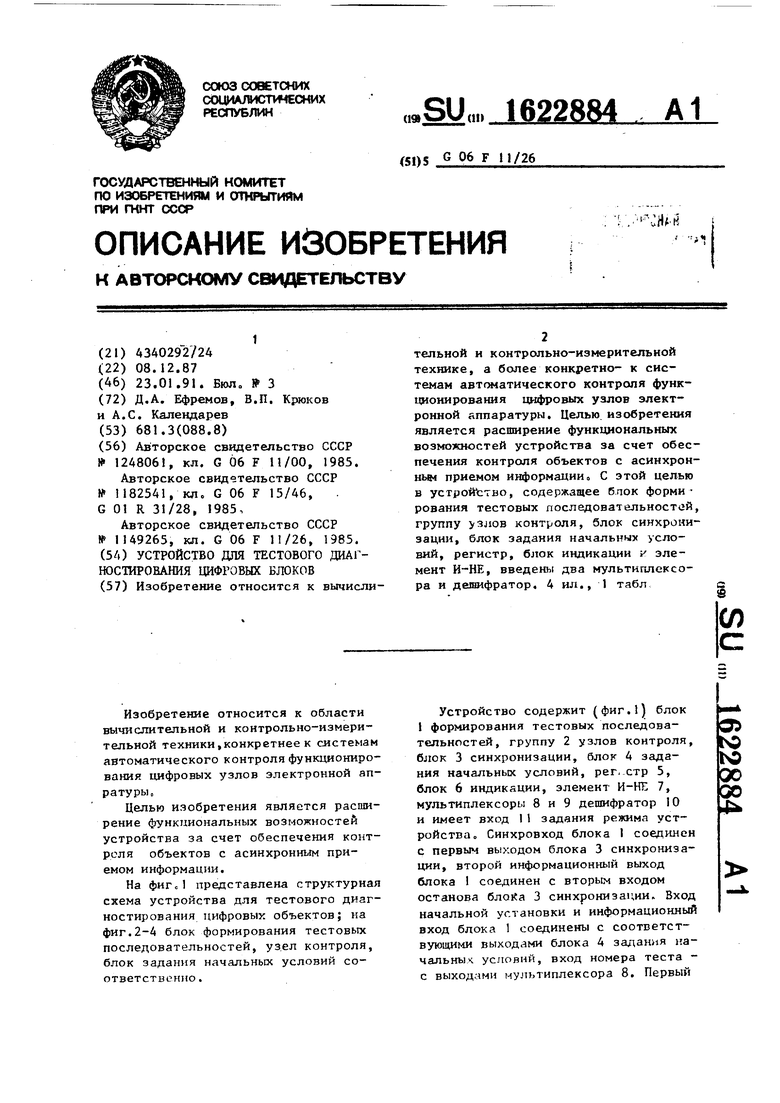

На фиг«1 представлена структурная схема устройства для тестового диагностирования цифровых объектов; на фиг.2-4 блок формирования тестовых последовательностей, узел контроля, блок задания начальных условий соответственно .

Устройство содержит (фиг.1) блок 1 формирования тестовых последовательностей, группу 2 узлов контроля, блок 3 синхронизации, блок 4 задания начальных условий, per- стр 5, блок 6 индикации, элемент И-НЕ 7, мультиплексоры 8 и 9 дешифратор 10 и имеет вход 11 задания режима устройства, Синхровход блока 1 соединен с первым выходом блока 3 синхронизации, второй информационный выход блока 1 соединен с вторым входом останова блока 3 синхронизации. Вход начальной установки и информационный вход блока 1 соединены с соответствующими выходами блока 4 задания начальны к условий, вход номера теста - с выходами мультиплексора 8. Первый

информационный выход блока 1 является выходом устройства для подключения объекта контроля, второй выход блока 1 соединен с входом блока 4. Входы устройства для подлкючения объекта контроль образуют первые информационные входы узлов 2 контроля, вторые, третьи и четвертые информационные входы которых раздельно соединены с третьими, четвертыми и пятыми информационными выходами блока 1„ Первые информационные выходы узлов 2 контроля соединены с входами элемента И- НЕ 7, выход которого соединен с входом блока 3 синхронизации. Четвертый и пятый выходы блока 4 подключены к информационному и управляющему входам мультиплексора 8, шестой блока 4 подключен к управляющему входу мультиплексора 9 и первому информационному входу дешифратора 10. Вторые информационные входы узлов 2 контроля соединены с информационным входом мультиплексора 9, выходы которого соединены с информационным входом регистра 5 и вторым информационным входом дешифратора 10. Выход регистра 5 соединен с вхоцом блока 6 индикации, а выход дешифратора 10 - с адресным входом мультиплексора 8. Третий выход блока 4 соединен с входами начальной установки узлов 2 контроля и регистра 5.

Блок 1 формирования тестовых последовательностей служит для выработки контрольных сигналов с заданным посредством блока 4 чередованием логических О и 1 для диагностируемого объекта, а также для формирэванил сигналов для узлов 2 ктнтрсо ч и сигнала окончания проверяющего теста для блока 4.

Блок 1 формирования тестовых последовательностей фиг.2) сосюит из блока 12 регистровой памяти и счетчика 13 импульсог. Блок 12 регистровой памяти выполнен на микросхемах К132РУБ, а счетчик 13 импулъсов - на микросхемах К155ИЕ7.

Группа узлов 2 контроля предназначена для обнаружения дефектных функциональных узлов в диагностируемом объекте по результатам прохождения проверяющего теста, а также для определения в выявленные дефектных узлах характера неисправности при прохождении диагностирующего пест . Характерными неигкрайностями являются

5

0

5

О

0

5

0

5

Константный ноль . Константная еди-| ница или Кратная неисправность. Количество узлов 2 контроля в группе определяется числом выводов диат- ностируемых объектов о

Функциональная схема одного из узлов 2 контроля представлена на фиг.З. Каждый из узлов контроля состоит из цифрового компаратора 14, элемента НЕ 15, двух RS-триггеров 16 и 17 и трех элементов И 18-20. Первый и второй входы цифрового компаратора 14 образуют одноименные входы соответствующего узла 2 контроля, вход элемента НЕ 15 является третьим входом узла 2 контроля, первые объединенные входы элементов И 18 и 19 образуют четвертый вход узла 2 контроля. Установочные (R) входы триггеров 16 и 17 образуют устэновочный вход узла 2 контроля. Выход элемента И 20 образует первый выход, а выходы RS- триггеров - второй выход узла 2 контроля, Выход цифрового компаратора 14 соединен с вторыми входами элементов И 18 и 19,вход элемента НЕ 15 соединен с третьим входом элемента П 18, а выход - с третьим входом эле- меи1а И 19. Выход элемента И 18 соединен с S-входом триггера 16, а выход элемента И 19 - с S-входом триггера 17. Прямые выходы RS-триггеров 16 и 17 соединены соответственно с первым и вторым входами элемента П 20„

Цифровой компаратор 14 предназначен для сравнения эталонной (ожидаемой) информации, поступающей из блока 12 регистровой памяти блока 1, с реально получаемой информацией, по- гтупающей с диагностируемого объек- iv, размещенного в контактном блоке 3. Компаратор 14 выполнен на микросхемах серий 500 и 597е Элемент IIE 15, RS-триггеры 16 и 17 и элементы И 18-20 совместно служат для организации работы устройства в режиме диагностирования, т.е, для выявления неисправностей Константный ьоль, Константная единица или Кратная неисправность при прохождении диагностирующего теста. Элемент НЕ 15, RS-триггеры 16 и 17 и лемьнты И 18-20 выполнены на микросхемах серии 155.

Блок 3 синхронизации представляет собой управляемые генератор импульсов с кварцевой стабилизацией

частоты, выполненный на микросхемах серии 1500. Внешнее управление устройством (пуск) осуществляется через синхровход генератора. Управление генератором осуществляется по двум входам от блока 1 формирования тестовых последовательностей и элемента И-НЕ 7 через трансляторы ТТЛ- ЭСЛ (К500ПУ124). Выходы блока 3 синхронизации подключены к синхровходу блока 1 (тактовые импульсы) и входу блока 4 задания начальных условий (окончание теста).

Блок 4 задания начальных условий служит для координации работы узлов и блоков устройства для тестового диагностирования цифровых объектов Блок 4 падания начальных условий

(фиг.4) состоит из двух регистров 21 и 22, двух дешифраторов 23 и 24 и буферных приемопередатчиков 25-29. Выход приемопередатчика 28 образует

первый выход, а выходы группы буферных приемопередатчиков 27 - второй выход блока 4 (информационную шину). Третий выход блока 4 образован выходом приемопередатчика 25, четвертый выход - выходом регистра 21, пятый выход - выходом приемопередатчнла 29, а шестой выход выходом регистра 22. вход приемопередатчика 26 является входом блока. Входы регистров 2 и 22, дешифраторов 23-24 и призмопер - датчика 27 образуют вхол задания режима устройства. Регистр 2 является буферным регистром, предназначеннь.м для приема из программатора и кратковременного хранения информации о -а- чальной установке счетчикл 1j импульсов и передачи этой информации на указанный счетчик через мугл пг и , . ор 8 Регистр 22 служит для пгиема из программатора, хранение и передачи информации о выборе диагностирующей программы в зависимости от результата происхождения проверяющей программы. Для каждого диагностируемого объекта предварительно при подготовке программы контроля определяются выходные состояния узлов контроля, соответствующие определенным видам отказг-п определенных узлов объекта. Этим состояниям соответствуют коды, заносимые в регистр 22, причем объем памяти и содержание регистра 22 определяют глубину диагностирования и направление поиска отказавшего узла объекта, т.е. количество точек диаг0

5

ностировяния . Выходная информация регистра 22 определяет номера и количество выходов узлов 2 контроля, подключаемых к входу дешифратора 10. Кроме того, она определяет значение выходного кода дешифратора 10, задающего новый адрес счетчика 13, по которому начинается прохождение дополнительного диагностирующего теста, уточняющего вид неисправности. Чем выше требуемый уровень диагностирования, тем большее количество адресов должен формировать дешифратор 10, 5 большую разрядность должен иметь

счетчик 13, больший объем памяти должен иметь блок 12 регистровой памяти. А в соответствии с этим большее количество комбинаций следует передавать через мультиплексор 9 в блок 1 формирования тестовых последовательностей с выходов регистра 22„ Регистры 2 1 и 22 выполнены на микросхемах К155ТМЗДешифратор 23 совместно с приемопередатчиком 25 служит для формирования из получяемых из программатора данных сигнала начальной установки узлов контроля и регистра 5, а чрн- емоп редг/тчик 26 - для передг чи в программатор сигнапа окончание теста с РЫХОДН олока „ Дешифрл а1 24 OBMtoTiio с приемпередатчикаь 28 и 29 служит дли формирования из получаемых с ььгхода программатор данных сигнала разрешения з шиси информации в б.чпк 12 памчти и сигнала начальной установки счетчи j 13 через мультиплексор 8). Дешифраторы 23 и 24 0 полноты на микросхемах К155ИДЗ, буферное приемопередатчики 25-29 - на микросхемах К559„

Регистр 5 является буферным регистром, предназначенным для кратко-временного хранения и передачи на входы блока 6 индикации и дешифратора 10 информации (результат контроля , поступающей на его входы через мультиплексор 9 с выбранного стяом блока А узла 2 контроля. Регистр 5 выполно-.н на микросхемах К155ТМ2Блок 6 индикации предназначен дл.1 отображения информации,получаемой с РЫХОДОВ регистра 5, и выполнен на индикаторных диодах АЛ307«

Мультиплексор 8 совместно с дешифратором 10 служит для выбора адреса начальной установки счетчика 13 им0

5

5

0

5

пульсов блока 1, причем в зависимости от режима работы устройства (проверяющий или диагностирующий тест) установка начального адреса счетчика 13 осуществляется или от блока 4, или от дешифратора 10 по результатам прохождения проверяющего теста Мультиплексор 8 и дешифратор 10 выполнены на микросхемах серии 155. Мультиплексор 9 предназначен для выбора узла 2 контроля, необходимого для диагностирования цифрового объекта и пропускания информации о результатах контроля с выбранного узла на регистр 5. Мультиплексор 9 такке выполнен НА микросхемах серии 155.

Устройство работает следующим об- разомс

Из программатор1 через буферные приемопередатчики и блок 12 памяти блока 1 записывается программа контроля - информация об условиях проведения контроля. Эта информация содержит в себе тестовую часть (входную информацию для объекта .диагностирования) , эталонную (.жил а ему ю информации. для цифровых комплр,- гор°и 14 узлов 2) 1 адресную ины рмацию (адрес проверяемого функционального узла в объекте ди-ai ностиро ч пия) , 1ю сигналу разрешения записи информации, формируемому в блохе 4 (из данных посредством дешифратора 24 и приемопередатчика 28), с выхода прнемочере- датчика 29 через мультиплексор 3 в счетчик 11 шосич я начачьныи адррг проверяющего теста. По .;i ri-n лм ронпзацип, поступающим с вых., a rnut ратора импульсов блок.1 3 на в,;,/, счетчика 13, происходи с гптычание информации и ч блока 12 вал часть информации nociynap r н ВУОДЫ соьектп ,;naj Нистирев Л ня . -палочная т.. г1- - из вхилм кг, - парат.v 1. 1 ; ) vio -t аллеей,- час ъ - па S-R- )Д-: триггеров ч и 17 ч., рез -. ric иы И Ьч и i° в cool ветс Bcni ii Aveci :i чип лнфс , мации o6. -i:e-i4iu 2 i гбор н.Н

К .- -КО.ТЬКИл ШОВ . 1ч Н ,1 1Л( ( i i-lBHсимости от трумуры 1 он jo- ля и лрпгра мы к.ггролл), уч i :i чукнч-м в процедуре Д II iio. i ров или :;;ufp.Rc- го объекта. Цифровые. - or ц тр.. горы 14 выбр iHiioix /н- -в . ov yi ir-c i вчя. г р rt- нение Э1 if i и i .iirlr рп т чг ( .:n. г реал.чо IHPHV KH - MI, i i yn in I .P вывод 1) дм 11 . i1 с 11 пин

5

0

5

0

5

0

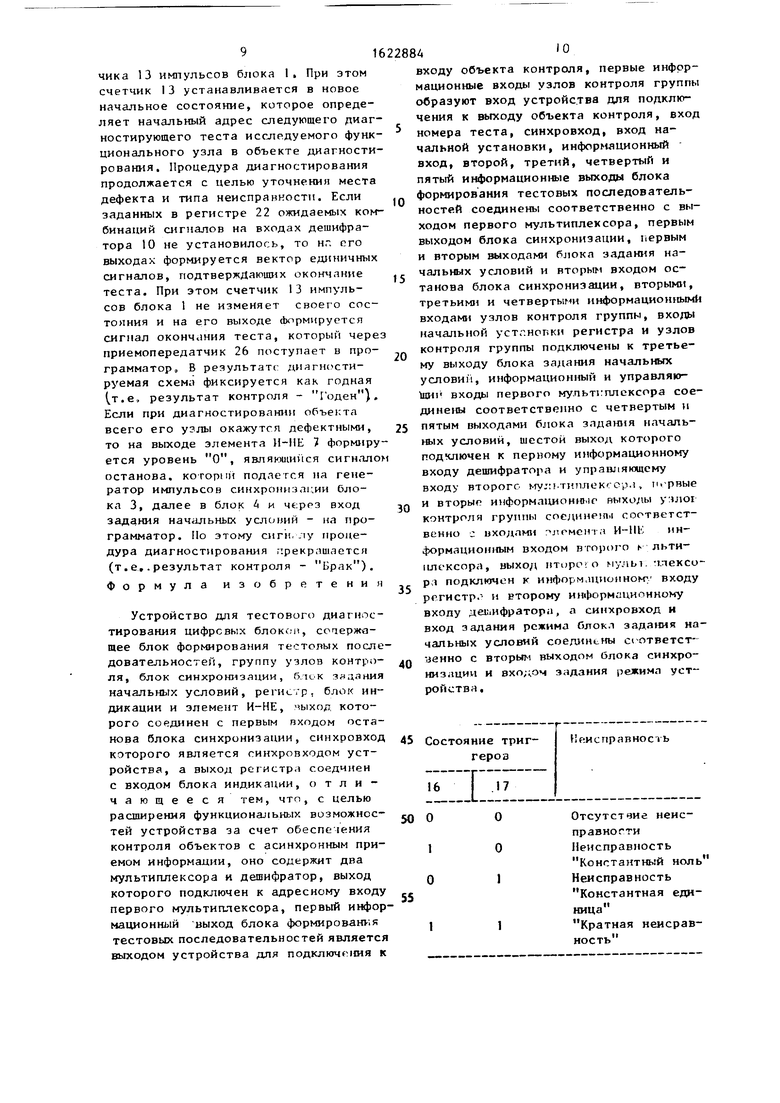

другие входы компараторов 14. При несовпадении сравниваемых сигналов на выходе соответствующего компаратора 14 формируется сигнал 1, который поступает на входы элементов И 18 и 19. Разрешающий сигнал, формируемый адресной частью информационного тестового слова в блоке 1, поступает на другие входы элементов И 18 и 19, а на их третьи входы с выхода блока 1 поступает эталонный сигнал Гна алемент К 18 - непосредственно, л на элемент Я 19 - через элемент HL 15), от значения которого зависит установка в единичное состояние триггеров 16 и 17, Триггер 16 устанавливается в единицу при условии несовт.адения сигналов на входе компаратора 14 (на его выходе устанавливается 1) и уровня 1 эталонного сигнала. Единичное состояние триггера 16 фиксирует неисправность Константный ноль 1. Триггер 17 устанавливается в состояние 1 при условие наличия в диагности- руеысм объекте неисправности Кон- стантная единица и уровня О эта- , онноге сигнала.При одновременном установлении триггеров 16 и 7 в юячие 1 на выходе элемента И 20 формируется уровень 1, что соответ- етву0 типу неисправности-диагности- туемог объекта Кратная неисправность. При совпадении сигналов на входах компар;тора 14 ча его выходе -, танавллвается уровень О, триггр- ,ы 1 б; и 17 также находятся в нулевом ттоинин, что свидетельствует об i сутсгь Ш дефекта L диагностируемом uubLKTc-, В аблнце отражаю состояние пи,. i r p.i 3 16 и 1 7 по прямому выходу i , uii -j ioc iM от xaraKrtpa неисправ- ни i, диагностируемого объекта,,

Резуль,а1Ы я;1агн . сткрования по ад- jjecdM, пос .-упаюишм на мультиплексора 9 и дешифратора 10 с выхода реги - ра 22 блока 4, передаются с вы- vonoii j па 2 контроля через мульти- лчексор 9 в регистр и дешифратор 10 Информация с выхг.да репи т- р.-3 Ь JT H.I вход блока 6 индИ к.-цни, итоб;. я ающий виды неиспран юс теи дипгностируемого объели. Если . тычодов учлсв 2 поступает ожидаемая информация, сведения о которой з intern- в регистр 22, то ь соответ- СГБИ. с кодол, поступаь.ашм с выхода ггуль Hi.j cKCi я 8, дешифратор (0 фор- мирует чопын ч л. адре. счетчика 13 импульсов блока 1. При этом счетчик I3 устанавливается в новое начальное состояние, которое определяет начальный адрес следующего диагностирующего теста иссле.дуемого функционального узла в объекте диагностирования. Процедура диагностирования продолжается с целью уточнения места дефекта и типа неисправности. Если заданных в регистре 22 ожидаемых комбинаций сигналов на входах дешифратора 10 не установилось, то нп его выходах формируется вектор единичных сигналов, подтверждающих окончание теста. При этом счетчик 13 импульсов блока 1 не изменяет своего состояния и на его выходе (Ьормнруетсл сигнал окончания теста, который чере приемопередатчик 26 поступает в программатор, В результате диагностируемая схема фиксируется как годная т.е, результат контроля - Годен). Если при диагностировании объекта всего его узлы окажутся дефектными, то на выходе элемента И-ИЕ 7 формируется уровень О, являющийся сигнало останова, который подается на генератор импульсов синхронизации блока 3, далее в блок А и ч€:роз вход задания начальных уелопий - на программатор. По этому снг н, лу процедура диагностирования прекращается (т.е..результат контроля - Брак). Формула изобретения

Устройство для тестового диагностирования цифровых блокол, соаержа- щее блок формирования тестовых последовательностей, группу узлов контроля, блок синхронизации, блик зддания начальных условий, регистр, блок индикации и элемент И-НЕ, чыход которого соединен с первым входом останова блока синхронизации, синхровход которого является синхровходом устройства, а выход регистр. соединен с входом блока индикации, отличающееся тем, чтп, с целью расширения функциональных возможностей устройства за счет обеспечения контроля объектов с асинхронным приемом информации, оно содержит два мультиплексора и дешифратор, выход которого подключен к адресному входу первого мультиплексора, первый информационный выход блока формирования тестовых последовательностей является выходом устройства для подключения к

5

0

5

0

входу объекта контроля, первые информационные входы узлов контроля группы образуют вход устройства для подключения к выходу объекта контроля, вход номера теста, синхровход, вход начальной установки, информационный вход, второй, третий, четвертый и пятый информационные выходы блока формирования тестовых последовательностей соединены соответственно с выходом первого мультиплексора, первым выходом блока синхронизации, первым и вторым выходами блока задания начальных условий и вторым входом останова блока синхронизации, вторыми, третьими и четвертыми информационными входами узлов контроля группы, входы начальной устг.нопкн регистра и узлов контроля группы подключены к третьему выходу блока задания начальных условии, информационный и управляющий входы первого мультиплексора соединены соответственно с четвертым и пятым выходами блока задания начальных условий, шестой выход которого подключен к первому информационному входу дешифратора и управляющему входу второго мультиплексор.), первые и вторыр информационные выходы контроля группы соединены соответственно с входами гмтомента И-П11 . информационным входом второго h льти- плексора, выход нтирсч о мулы, члексо- рл подключен к информационному входу рггистр.1 и второму информационному входу дешифратора, а синхровход и вход задания режима блокл задания начальных условий соединены соответственно с вторым выходом блока синхронизации и вхо;;оч задания режима устройства.

45

50

55

От&лона1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для диагностики неисправностей технических объектов | 1987 |

|

SU1515175A2 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике, а более конкретно- к системам автоматического контроля функционирования цифровых узлов электронной аппаратуры. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля объектов с асинхронным приемом информации о С этой целью в устройЬтво, содержащее бпок формирования тестовых последовательностей, группу злов контроля, блок синхронизации, блок задания начальных условий, регистр, блок индикации v элемент И-НЕ, введены два мультиплексора и дешифратор, 4 ил., 1 табл

Отвлеки 1 От&таПГ

От блат 1

18

От илот Ь

79

77

%

п

V

16

Начальная ьустякйю

Окончание /акт

bjfwxpnoeiuaf /АИ

ноя шина

Розреиение

записи -- Начальная ycma/rolm счетчика

л« ивVHOU ycmototки оетию

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля радиоэлектронной аппаратуры | 1984 |

|

SU1182541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-23—Публикация

1987-12-08—Подача