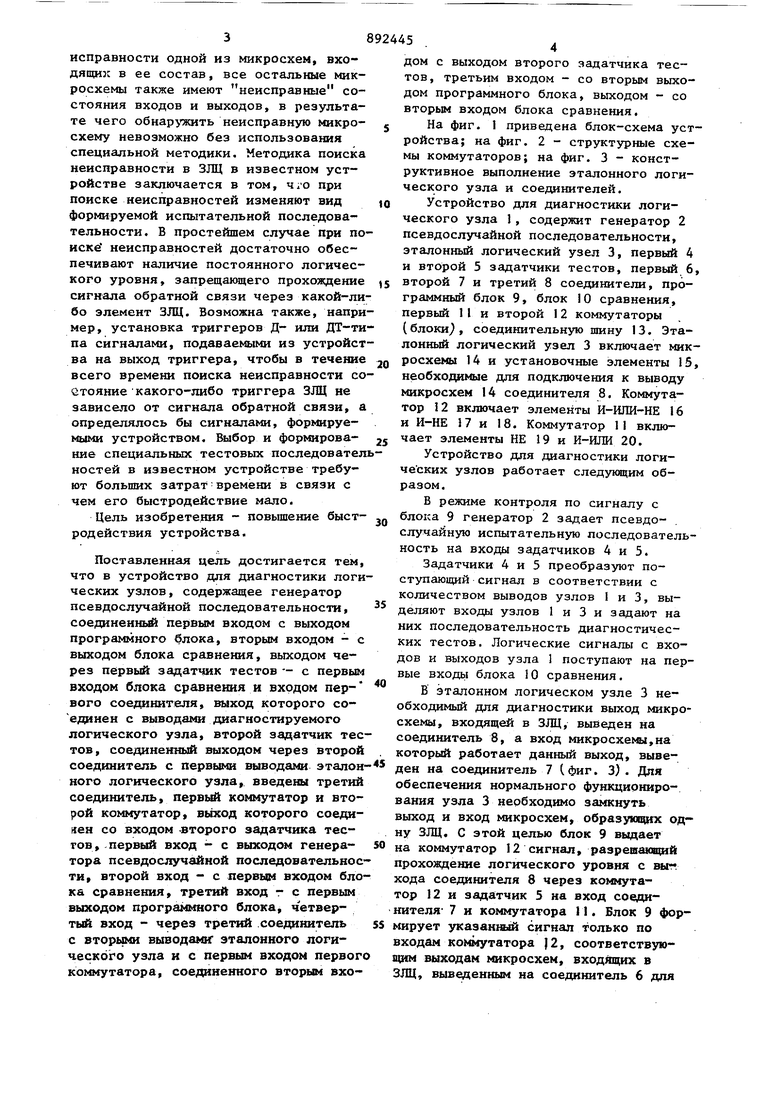

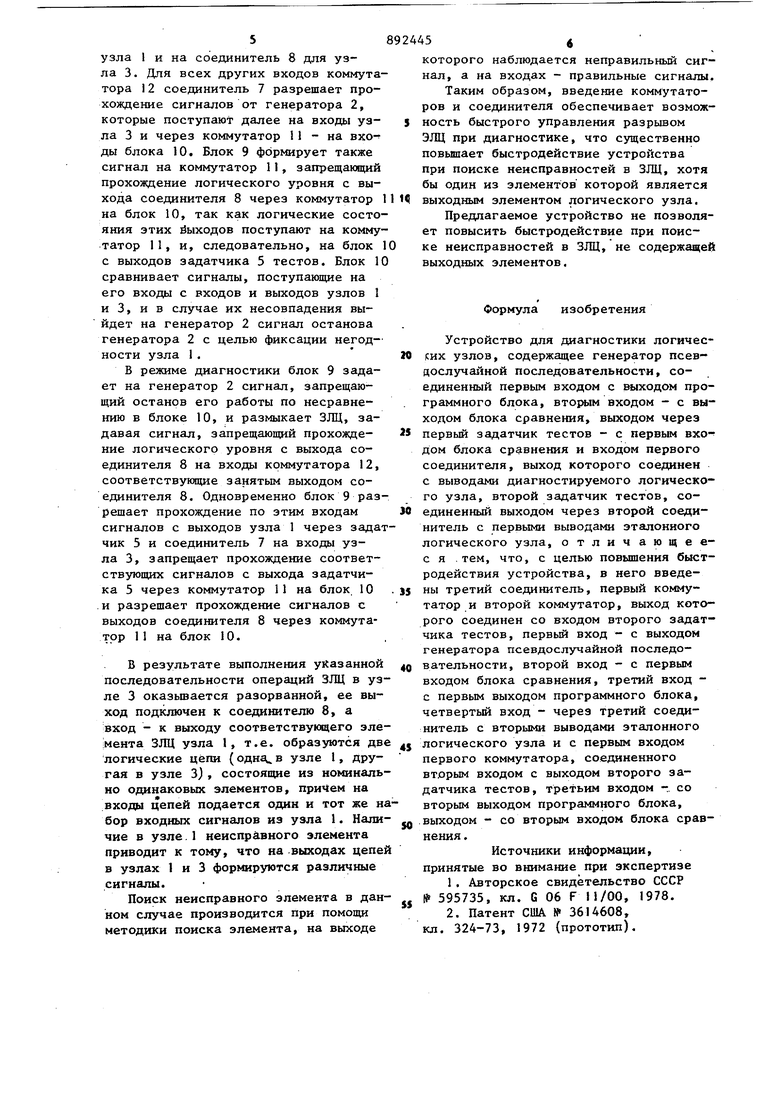

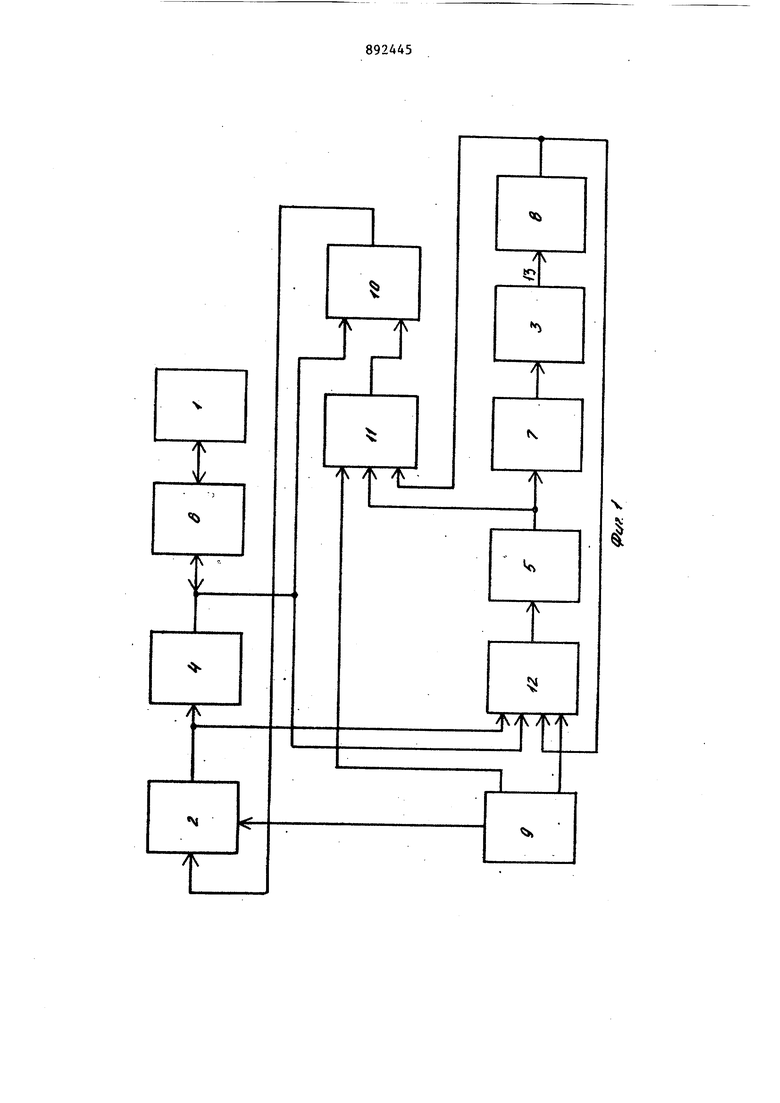

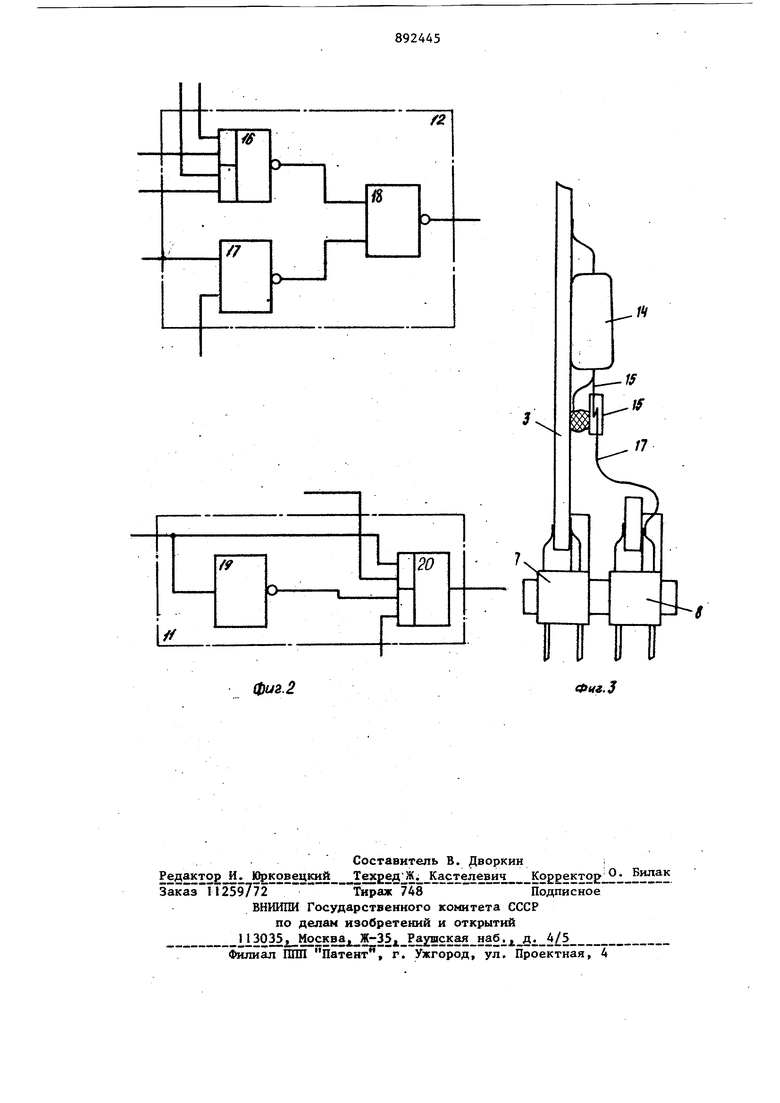

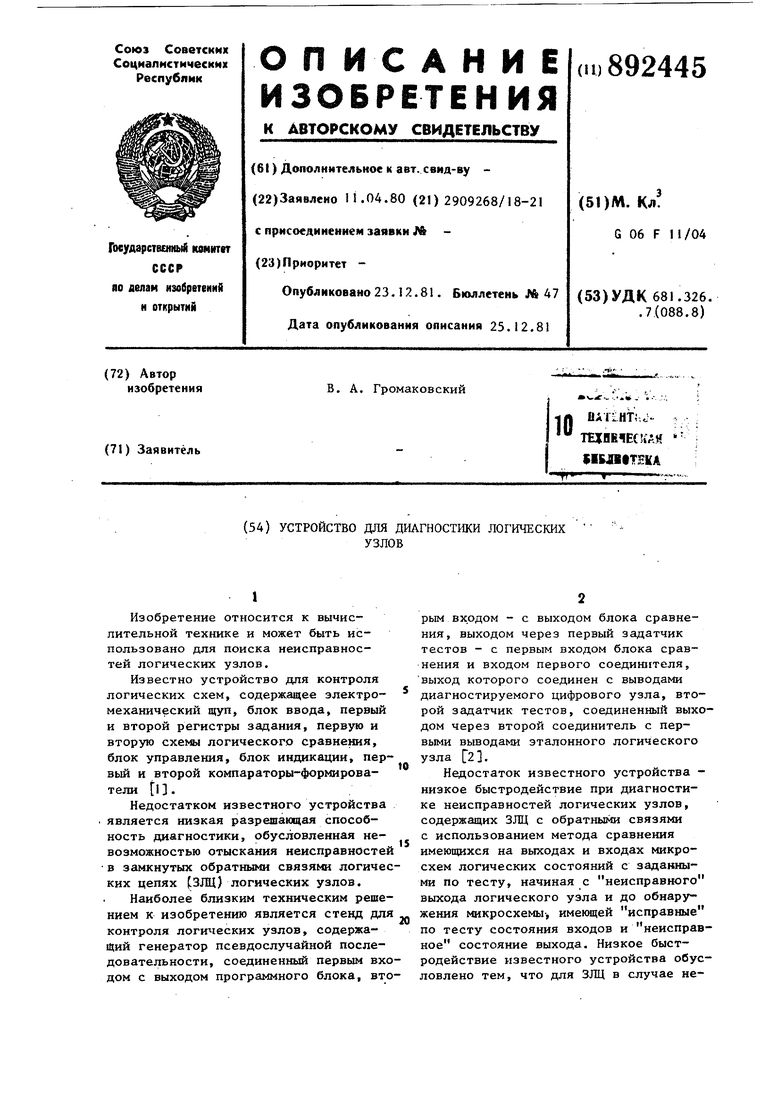

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей логических узлов. Известно устройство для контроля логических схем, содержащее электромеханический щуп, блок ввода, первый и второй регистры задания, первую и вторую схемы логического сравнения, блок управления, блок индикации, первый и второй компараторы-формирователи 1.. Недостатком известного устройства является низкая разрешающая способность диагностики, обусловленная невозможностью отыскания неисправностей в замкнутых обратшлми связями логичес ких цепях ЗЛЦ) логических узлов. Наиболее близким техническим решением к изобретению является стенд для контроля логических узлов, содержащий генератор псевдослучайной последовательности, соединенный первым вхо дом с выходом программного блока, вто рым входом - с выходом блока сравнения, выходом через первый задатчик тестов - с первым входом блока сравнения и входом первого соединителя, выход которого соединен с выводами диагностируемого цифрового узла, второй задатчик тестов, соединенный выходом через второй соединитель с первыми выводами эталонного логического узла 2. Недостаток известного устройства низкое быстродействие при диагностике неисправностей логических узлов, содержащих ЗЛЦ с обратными связями с использованием метода сравнения имеющихся на выходах и входах микросхем логических состояний с заданными по тесту, начиная с неисправного выхода логического узла и до обнаружения микросхемы, имеющей исправные по тесту состояния входов и неисправное состояние выхода. Низкое быстродействие известного устройства обусловлено тем, что для ЗЛЦ в случае неисправности одной из микросхем, входящих в ее состав, все остальные микросхемы также имеют неисправные состояния входов и выходов, в результате чего обнар -жить неисправную микросхему невозможно без использования специальной методики. Методика поиска неисправности в ЗЛЦ в известном устройстве заключается в том, ч/о при поиске неисправностей изменяют вид формируемой испытательной последовательности. В простейшем случае при поиске неисправностей достаточно обеспечивают наличие постоянного логического уровня, запрещающего прохождение сигнала обратной связи через какой-либо элемент ЗЛЦ. Возможна также, напри мер, установка триггеров Д- или ДТ-ти па сигналами, подаваемыми из устройст ва на выход триггера, чтобы в течение всего времени поиска неисправности со стояние какого-либо триггера ЗЛЦ не зависело от сигнала обратной связи, а определялось бы сигналами, формируемыми устройством. Выбор и формирование специальных тестовых последовател ностей в известном устройстве требуют больших затратвремени в связи с чем его быстродействие мало. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для диагностики логи ческих узлов, содержащее генератор псевдослучайной последовательности, соединенш перВ1Л4 входом с выходом программного блока, вторым входом - с выходом блока сравнения, выходом через Первый задатчик тестов - с первым входом блока сравнения и входом первого соединителя, выход которого соединен с выводами да1агностируемого логического узла, второй задатчик тес тов, соединенный выходом через второй соединитель с первыми выводами эталон ного логического узла, введены третий соединитель, нерв1й коммутатор и второй коммутатор, выход которого соединен со входом -второго задатчика тесгов,.первый вход - с выходом генератора псевдослучайной последовательнос ти, второй вход - с перв14М входом бло ка сравнения, третий вход г с первым выходом программного блока, четвертый вход - через третий .соединитель с вторыми выводам1Г эталонного логического узла и с первым входом первого коммутатора, соединенного вторым вхощкм выходам микросхем, входящих в ЗЛЦ, выведенным на соединитель 6 для дом с выходом второго задатчика тестов, третьим входом - со вторым выходом программного блока, выходом - со вторьв входом блока сравнения. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - структурные схемы коммутаторов; на фиг. 3 - конструктивное выполнение зталонного логического узла и соединителей. Устройство для диагностики логического узла 1, содержит генератор 2 псевдослучайной последовательности, эталонный логический узел 3, первый 4 и второй 5 задатчики тестов, первый 6, второй 7 и третий 8 соединители, программный блок 9, блок 10 сравнения, первый 1I и второй 12 коммутаторы {блоки, соединительную шину I3. Эталонный логический узел 3 включает микросхемы 14 и установочные элементы 15, необходашые для подключения к выводу микросхем 14 соединителя 8. Коммутатор 12 включает элементы И-ИЛИ-НЕ 16 и И-НЕ 57 и 18. Коммутатор 11 включает элементы НЕ 19 и И-ИЛИ 20. Устройство для диагностики логических узлов работает следукнцим образом. В режиме контроля по сигналу с блока 9 генератор 2 задает псевдослучайную испытательную последовательность на входы задатчиков 4 и 5. Задатчики 4 и 5 преобразуют поступающий сигнал в соответствии с количеством выводов узлов 1 и 3, выделяют входы узлов 1 и 3 и задают на них последовательность диагностических тестов. Логические сигналы с входов и выходов узла 1 поступают на первые входь блока 10 сравнения. В эталонном логическом узле 3 необходимый для диагностики выход микросхемы, входящей в ЗЛЦ, выведен на соединитель 8, а вход микросхемы,на который работает данный выход, выведен на соединитель 7 С фиг. 3). Для обеспечения нормального функционирования узла 3 необходимо замкнуть выход и вход микросхем, образующих одну ЗЛЦ. С этой целью блок 9 выдает на коммутатор 12 сигнал, разрешающий прохождение логического уровня с выг хода соединителя 8 через коммутатор 12 и задатчик 5 на вход соедиителя- 7 и коммутатора I1. Блок 9 форирует указан1глй сигнал только по ходам коммутатора |2, соответствую5узла I и на соединитель 8 для узла 3. Для всех других входов коммута тора 12 соединитель 7 разрешает прохождение сигналов от генератора 2, которые поступают далее на входы узла 3 и через коммутатор П - на вхо- ды блока 10. Блок 9 формирует также сигнал на коммутатор 11, запрещающий прохождение логического уровня с выхода соединителя 8 через коммутатор на блок 10, так как логические состо яния этих йыходов поступают на комму татор 11, и, следовательно, на блок с выходов задатчика 5 тестов. Блок 1 сравнивает сигналы, поступающие на его входы с входов и выходов узлов 1 и 3, и в случае их несовпадения выйдет на генератор 2 сигнал останова генератора 2 с целью фиксации негодности узла 1. В режиме диагностики блок 9 задает на генератор 2 сигнал, запрещающий останов его работы по несравнению в блоке 10, и размыкает ЗЛЦ, задавая сигнал, запрещающий прохождение логического уровня с выхода соединителя 8 на входы коммутатора 12, соответствующие занятым выходом соединителя 8. Одновременно блок 9 раз решает прохождение по этим входам сигналов с выходов узла 1 через зада чик 5 и соединитель 7 на входы узла 3, запрещает прохождение соответствующих сигналов с выхода задатчика 5 через коммутатор 11 на блок 10 и разрешает прохождение сигналов с выходов соединителя 8 через коммутатор 11 на блок 10. В результате выполнения указанной последовательности операций ЗЛЦ в уз ле 3 оказьшается разорванной, ее выход подключен к соединителю 8, а вход - к выходу соответствующего эле |Мента ЗЛЦ узла 1, т.е. образуются дв логические цепи ( узле 1, другая в узле 3), состоящие из номиналь но одинаковых элементов, причем на входы цепей подается один и тот же н бор входных сигналов из узла 1. Нали чие в узле.I неисправного элемента приводит к тому, что на выходах цепе в узлах 1 и 3 формируются различные сигналы. Поиск неисправного элемента в дан ном случае производится при помощи методики поиска элемента, на выходе 5 которого наблюдается неправильный сигнал, а на входах - правильные сигналы. Таким образом, введение коммутаторов и соединителя обеспечивает возможность быстрого управления разрывом ЭЛЦ при диагностике, что существенно повышает быстродействие устройства при поиске неисправностей в ЗЛЦ, хотя бы один из элементов которой является выходш 1м элементом логического узла, Предпагаемое устройство не позволяет повысить быстродействие при поиске неисправностей в ЗЛЦ, не содержащей выходных элементов. Формула изобретения Устройство для диагностики логичес|сих узлов, содержащее генератор псевдослучайной последовательности, соединенный первым входом с выходом программного блока, вторым входом - с выходом блока сравнения, выходом через первый задатчик тестов - с первым входом блока сравнения и входом первого соединителя, выход которого соединен с выводами диагностируемого логического узла, второй задатчик тестов, соединенный выходом через второй соединитель с первыми выводами эталонного логического узла, отличающеес я тем, что, с целью повышения быстродействия устройства, в него введены третий соединитель, первый коммутатор и второй коммутатор, выход которого соединен со входом второго задатчика тестов, первый вход - с выходом генератора псевдослучайной последовательности, второй вход - с первым входом блока сравнения, третий вход с первым выходом программного блока, четвертый вход - через третий соединитель с вторыми выводами эталонного логического узла и с первым входом первого коммутатора, соединенного вторым входом с выходом второго задатчика тестов, третьим входом - со вторым выходом программного блока. выходом - со вторым входом блока сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 595735, кл. G 06 F 11/00, 1978. 2.Патент США № 3614608, кл. 324-73, 1972 (прототип).

фиг.2

Фнг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| ПЕРЕНОСНОЙ ПРОГРАММНО-ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2007 |

|

RU2363975C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU993168A1 |

Авторы

Даты

1981-12-23—Публикация

1980-04-11—Подача