сравнения сигнатур, соединенного вторым входом с девятЕОм вьпсодом блока управления, третьими входами с выходами сигнатурного анализатора соединенного первым входом с четвертым выходом блока управления, вторым входом - с выхсяом щупа, третьим входом - с десятым выходом блока управления, соединенного седь мым входом с выходом блока сравнения сигнатур, одиннадцатым и двенс1Дцатым выходами - соответственно с первым и вторым входами блока памяти, соединенного первыми, вторыми, третьими и четвертыми выходалш соответственно с вторыми входами первого, второго, третьего и четвертого регистров, выходы первого регистра соединены с вторыми входаrviM блока сравнения адресов, с четвертыми входами мультиплексора и с первыми входами второго блока индикации , соединенного вторыми входами с выходами второго регистра, с третьими входами блока сравнения адресов и с вторыми входами ключевого элемента, соединенного выходами с вторыми входами второго регистра адреса, выходы которого соединены с четверты м .входами блока сравнения адресов, соединенного выходом с восьмым входом блока управления,

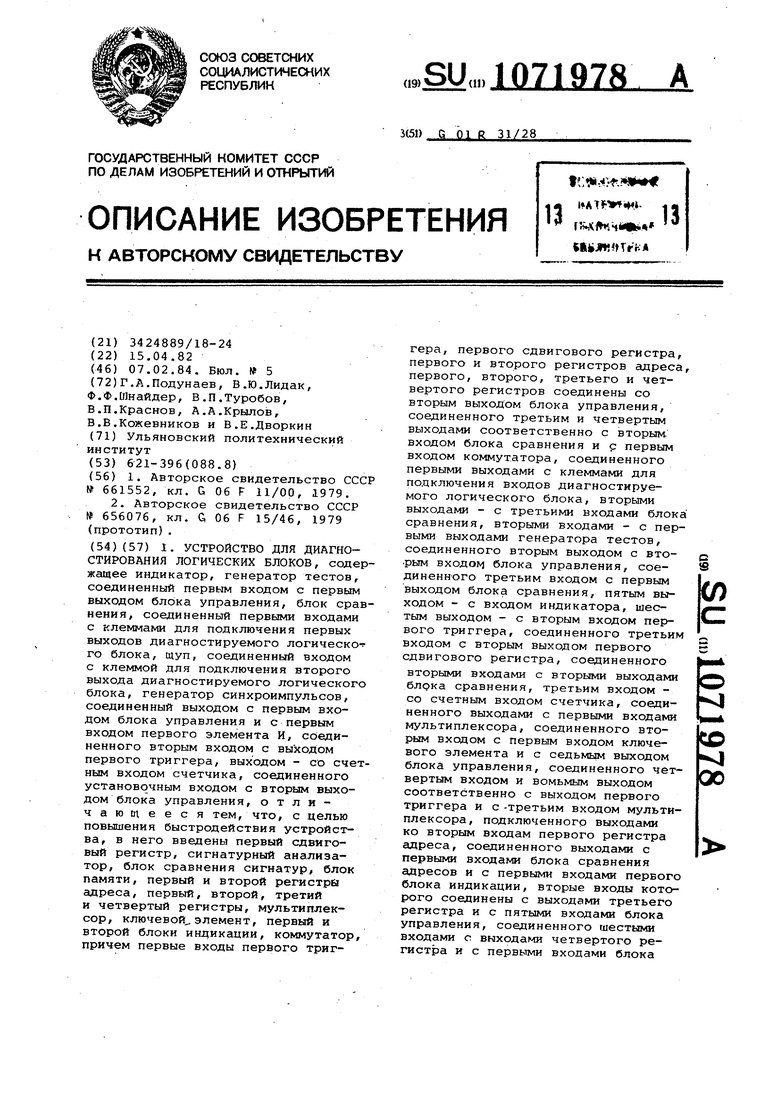

2. Устройство по п. 1, отлич а ю щ е е с я тем, Ч1 облок управления содержит шифратор, соединенный первым и вторым входами соответственно с четвертым и восьмым входами блока;, первым выходом - с шестЕлм выходом блока, третьим и четвертым входами-соответственно с выходами второго и третьего элементов И, входы которых соединены соответственно с пятыми и шестыми входами блока, пятый выход которого соединен с вторым выходом шифратора, третий и четвертый выходы которого соединены соответственно с первым и вторым входами второго сдвигового регистра, пятый выход с первыми входагЛи четвертого, пятого и шестого элементов И, шестой

выход - с первым и вторым входами лемента И-ЙЛИ-HEj пятый выход с вторым входом шестого элемента И и с первым выходом второго сдви-о гового регистра, соединенного вторым выходом с третьим входом элемента И-ИЛИ-НЕ, третьим выходом - с вторым входом пятого элемента И, четвертым выходом - с четвертым вхоом элемента И-ИЛИ-НЕ, пятым выхоом - с вторым входом четвертого элемента И, третьим входом - с шестым входом шифратора, с вторым выходом блока, с первым выводом первой кнопки и с первым R-входом второго триггера, соединенного вторым R-вхоом с третьим входом блока, е R-вхоом третьего триггера и с седьмым входом шифратора, соединенного восьмым входом с выходом седьмого элемента И, Соединенного Первым вхоом с седьмым входом блока, вторым входом - с девятым выходом блока, с третьим R-входом второго триггера и с первым выходом дешифратора, соединенного входом с вторым входом блока, вторым выходом - с десятым выходом блока и с первым входом восьмого элемента И, соединенного выхо дом . с третьим выходом блока, вторым входом - с выходом третьего триггера, соединенного S -входом с первым вывбдом первой кнопки, соединенной вторым выводом с первым входом блока, с первым входом девя- того элемента И, с седьмьлм выходом шифратора и с первым входом формирователя одиночных импульсов, соединенного вторым и третьим входами соответственно с первым и вторым выводами второй кнопки, выходом - с четBepTidM выходом блока и S -входом второго триггера, соединенного выходом с вторым входом девятого элемента И, подключенного выходом к первому выходу блока, восьмой, седьмой и двенадцатый выходы которого соединены соответственно с выходами четвертого, пятого и шестого элементов И, а одиннадцатый выход с выходом элемента И-ИЛИ-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

1. УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее индикатор, генератор тестов, соединенный первым входом с первым выходом блЬка управления, блок сравнения, соединенный первьами входами с клеммами для подключения первых выходов диагностируемого логического блока, щуп, соединенный входом с клеммой для подключения второго выхода диагностируемого логического блока, генератор синхроимпульсов, соединенный выходом с первым входом блока управления и с первым входом первого элемента И, соединенного вторым входом с выходом первого триггера, выходом - со счетным входом счетчика, соединенного установочным входом с вторым выходом блока управления, отличающееся тем, что, с целью повьошения быстродействия устройства, в него введены первый сдвиговый регистр, сигнатурный анализатор, блок сравнения сигнатур, блок памяти, первый и второй регистра адреса, первый, второй, третий и четвертый регистры, мультиплексор, ключевой элемент, первый и второй блоки индикации, коммутатор, причем первые входы первого триггера, первого сдвигового регистра, первого и второго регистров адреса, первого, второго, третьего и четвертого регистров соединены со вторым выходом блока управления, соединенного третьим и четвертым выходами соответственно с вторым, входом блока сравнения и с первым входом коммутатора, соединенного первыми выходами с клеммами для подключения входов диагностируемого логического блока, вторыми выходами - с третьими входами блока сравнения, вторыми входами - с первыми выходами генератора тестов, соединенного вторым выходом с втос рым входом блока управления, сое диненного третьим входом с первым выходом блока сравнения, пятым вы ходом - с входом индикатора, шестым выходом - с вторым входом первого триггера, соединенного третьим входом с вторым выходом первого сдвигового регистра, соединенного вторыми входами с вторыми выходами блока сравнения, третьим входом со счетным входом счетчика, соединенного выходами с первыми входами мультиплексора, соединенного втосо рым вхсдом с первым входом ключевого элемента и с седьмьгм выходом блока управления, соединенного четСХ) вертым входом и вомьмым выходом соответственно с выходом первого триггера и с -третьим входом мультиплексора, подключенного выходами ко вторым входам первого регистра адреса, соединенного выходами с первыми входами блока сравнения адресов и с первыми входами первого блока индикации, вторые входы которого соединены с выходами третьего регистра и с пятыми входами блока управления, соединенного шестыми входами с выходами четвертого регистра и с первьтми входами блока

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре тесто вого контроля, диагноситики и настройки логических блоков.

Известно устройство для ди гнос.тярования логических схем и блоков.

содержащее блок входных сигналов, блок эталонных сигналов, блок сравнения, бдок ввода данных, , блок коммутации, блок памяти, блок 5 индикации, блок управления, щуп 1,

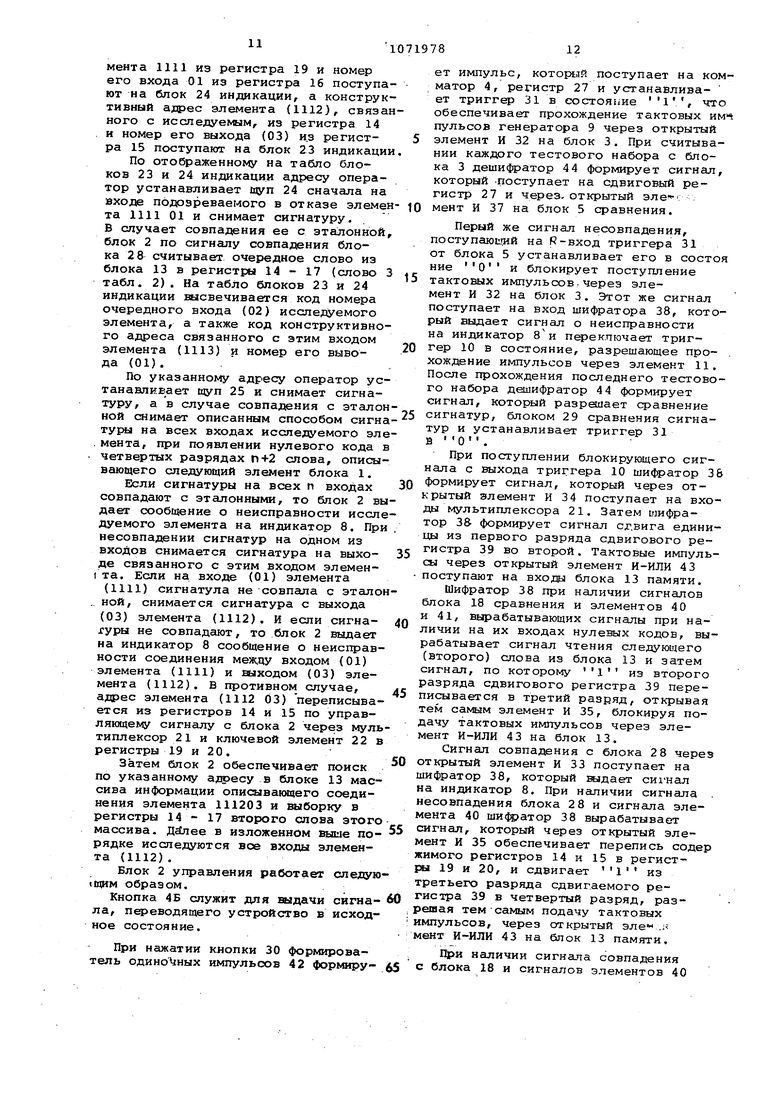

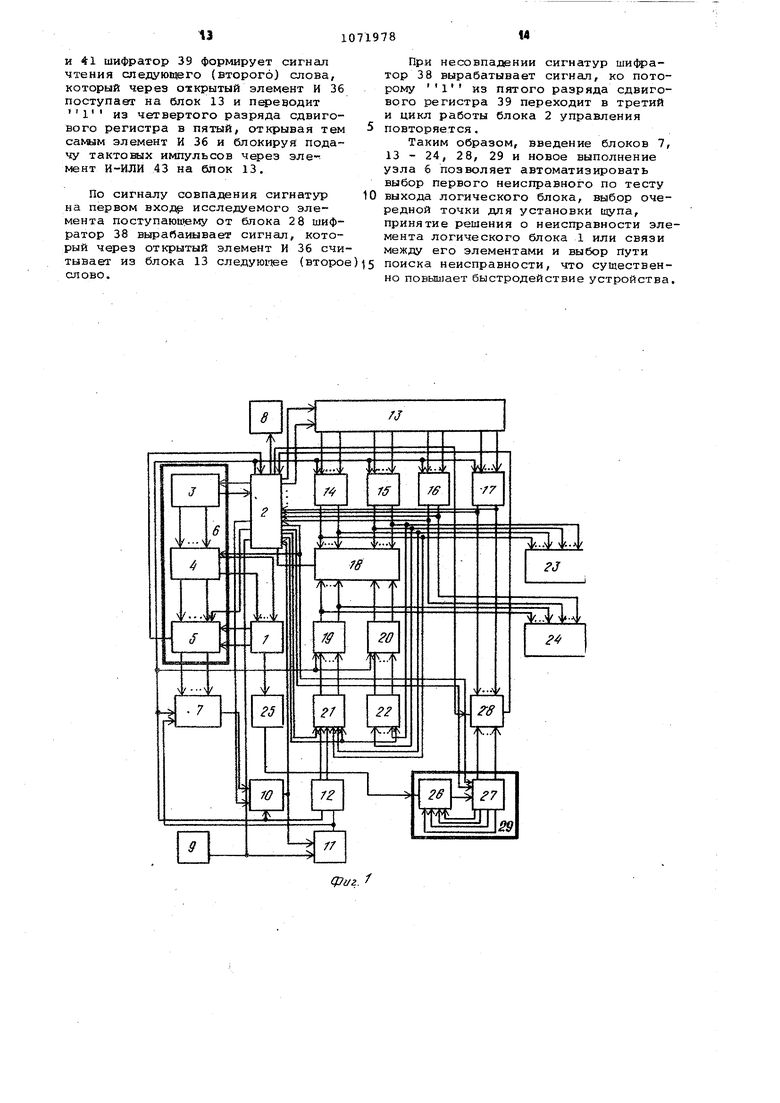

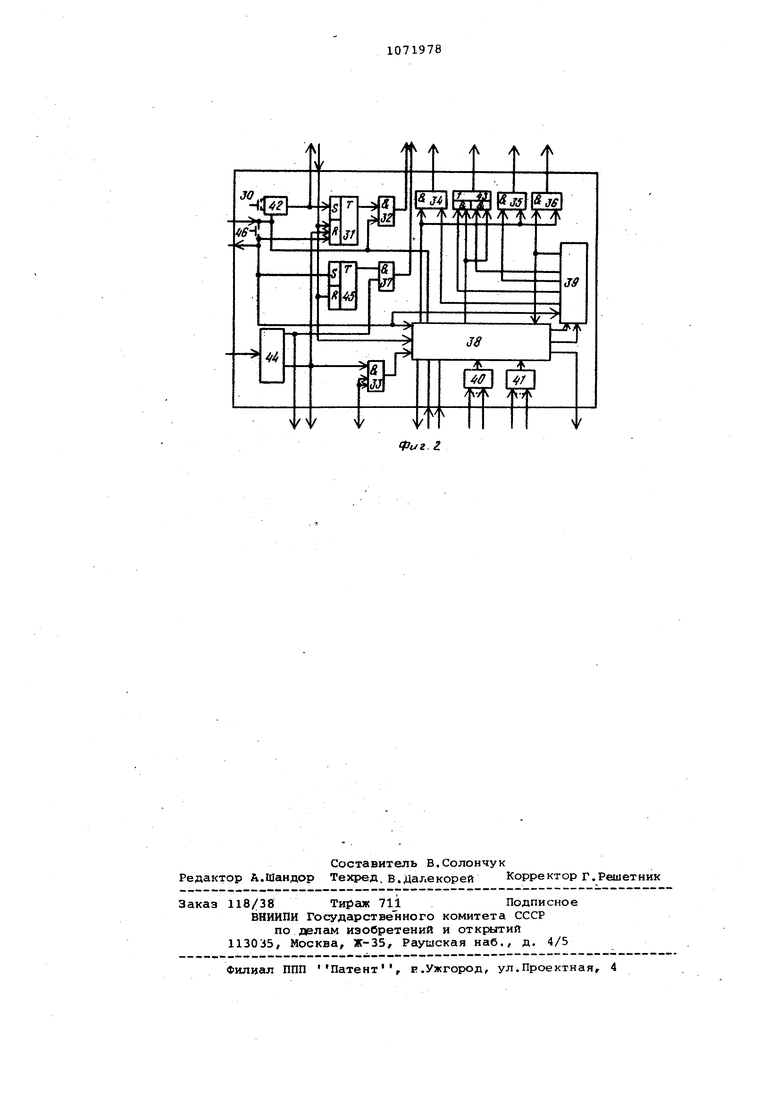

Недостатком устройства является низкое быстродействие из-за больших временных затрат на определение места неисправности, связанных с отсутствием автоматизации процес са диагностирования. Наиболее близким техническим решением к изобретению является ус ройство для поиска неисправностей в дискретных объектах, содержащее индикатор, генератор тестов, соединенный первым входом с первым выходом блока.управления, блок сра нения, соединенный первыми входами с клеммами для подключения первых выходов диагностируемого логическо блока, щуп, соединенный входом с клеммой для подключения второго хода диагностируемого логического блока, генератор синхроимпульсов, соединенный выходом с первым входом блока управления и с первым вх дом первого элемента И, соединенно вторым входом с выходом первого триггера, выходом - со счетным вхо дом счетчика, соединенного установочным входом со вторым выходом блока управления C2J. Недостатком известного устройст является низкое быстродействие обусловленное тем, что выбор перво го неисправного по тесту выхода логического блока для-обеспечения начала поиска неисправности осущес ляется оператором неавтоматически; выбор очередной точки для установки щупа осуществляется оператором по электрической схеме логического блока, т.е. также неавтоматически, принятие решения о неисправности д ного элемента или электрической связи между элементами осуществляется оператором, т.е. неавтоматически f выбор пути поиска неисправности также неавтоматизирован. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для диагностирования логических блоков, содер жащее индикатор, генератор тестов, соединенный первым входом с первым выходом блока управления, блоки сравнения, соединенный первыми входами с клеммами для подключения первых выходов диагностируемого логического блока, щуп, соединенный входом с клеммой для подключения второго выхода диагностируемог логического блока, генератор синхр импульсов, соединенный выходом с первым входом блока управления и с первым входом первого элемента И соединенного вторым входом с выходом первого триггера, выходом - со счетным входом счетчика, соединенного установоыным входом с вторым выходом блока управления, введены первый сдвиговый регистр, сигнатур ный анализатор, блок сравнения сигнатур, блок сравнения адресов, блок памяти, первый и второй регистры, адреса, первый, второй, .третий и четвертый регистры, мультиплексор, ключевой элемент, первый и второй блоки индикации, коммутатор, причем первые входы первого триггера, первого сдвигового регистра, первого и второго регистров адреса, первого, второго, третьего и четвертого регистров соединены с вторым выходом блока управления, соединенного третьим и четвертым выходами соответственно с вторым входом блока сравнения и с первым входом коммутатора, соединенного первыми выходами с клеммами для подключения входов диагностируемого.логического блока, вторыми выходамичс третьими входами блока сравнения, вторыми входа ш - с первыми выходами генератора тестов, соединенного вторым выходом с вторым входом блока управления, воединенного третьим входом с первым выходом блока сравнения, пятым выходом - с входом индикатора, шестым выходом - с вторым входом первого триггера, соединенного третьим входом с вторым выходом первого сдвигового регистра, соединенного вторы и входами с вторыми выходами блока сравнения, третьим входом - со счетным входом счетчика, соединенного выходами с первыми входами мультиплексора, соединенного вторым входом с первым входом ключевого элемента и с седьмым выходом блока управления, соединенного четвертым входом и восьмым выходом соответственно с выходом первого триггера и с третьим входом мультиплексора, подключенного выходами к вторым входам первого регистра адреса, соединенного выходами с первыми входами блока сравнения адресов и с первыми входами первого блока индикации, вторые входы которого соединены с выходами третьего регистра и с пятыми входами блока управления, соединенного шестыми входами с выходами четвертого регистра и с первыми входами блока сравнения сигнатур, соединенного вторым входом с девятым выходом блока управления, третьими входами - с выходами сигнатурного анализатора, соединенного первым входом с четвертым выходом блока управления, вторым входом с выходом щупа, третьим входом - с десятым выходом блока управления, соединенного седьмым входом с выходом блока сравнения сигнатур, и одиннадцатым и двенадцатым выхода - ми - соответственно с первым.и йторым входами блока памяти, соединенного первыми, вторыми, третьими ..и четвертьши выходами соответственно с вторыми входами первого, второго, третьего и четвертого регистров, выходы первого регистра соединены с вторыми входами блока сравнения адресов, с четвертыми входами муль™ типлексора, и с первыми входами второго блока индикации, соединенного вторыми входами с выходами второго регистра, с третьими входам рлока сравнения адресов и с вторыми входами ключевого .элемента, соединенного выходами с ВТО1Ж1МИ входами второго регистра адреса, выходы которого соединены с четвертыми входами блока сравнения адресов, соединенного выходом с входом блока управления. Кроме того, блок управления содержит шифратор, соединенный первым и вторым входами соответственно с четвертым и восьмым входами блока, первым выходом - с шестым выходом блока, третьим и четвертым входами соответственно с выходами второго и третьего элементов И, входы которых соединены соответственно с пяты ми и шестыми входами блока, пятый выход которого соединен с вторым выходом шифратора, третий и четвертый выходы которого соединены соответственно с первым и Яторым входам второго сдвигового регистра, пятый выход - с первыми входами четвертог пятого и шестого элементов И, шесто выход - с первым и вторым входами элемента И-ИЛИ-НЕ, пятый выход - с вторым входом шестого элемента И и с первым выходом второго сдвигово го регистра, соединенного вторым выходом с третьим входом элемента И-ИЛИ-НЕ, третьим выходом - с вт рым входом пятого элемента И, четвертым выходом - с четвертым входом элемента И-ИЛИ-НЕ, пятым выходом с вторым входом четвертого элемента И, третьим входом - с шестым вхо дом шифратора с-вторым выходом блока, с первым выводом первой кнопки и с первым R -входом второго триггера, соединенного вторым 1 -входом с третьим входом блока, с R -входом третьего триггера и с седьмым входом шифратора, соединенного восьмым входом с выходом седьмого элемента И, соединенного первым входом с седьмым входом блока, вторым входом - с девятым выходом блока, с трет|.им R -входом второго триггера и с первым выходом дешифратора, сое диненного входом с вторым входом блока, вторым выходом - с десятым выходом блока и с первым входом восьмого элемента И, соединенного выходом с третьим выходомблока, вторым входом - с выходом третьего триггера, соединенного 5-входом с ервкм выводом первой кнопки,соеиненной вторым выводом с первым входом блока, с первым входом девятого элемента И, с седьмым выходом ифратора и с первым входом формирователя одиночных импульсов, соединенного вторым и третьим входами соответственно с первым и вторым выводами второй кнопки, выходом - с четвертым выходом блока и / -входом второго триггера, соединенного выходом с вторым входом Девятого элемента И, подключенного выходом к первому выходу блока, восьмой, седьмой, и двенадцатый выходы которого соединены соответственно с выходами четвертого, пятого и шестого элементов И, а одиннадцатый выход с выходом элемента И-ИЛИ-НБ, На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок схема блока управления. Устройство,для контроля логического блока 1 содержит блок 2 управ ления, генератор 3 тестов, коммутатор 4, блок 5 сравнения, узел 6 контроля, первый сдвигоазй регистр 7, индикатор 8, генератор 9 синхроимпульсов, первый триггер 1-0, первый элемент И 11, счетчик 12, блок 13 памяти, первый 14, второй 15, третий 16, четвертый 17 регистры, блок 18 сравнения адресов, первый 19 и второй 20 регистры адреса, мультиплексор 21, ключевой элемент 22, второй 23 и первый 24 блоки индикации, шуп 25, сумматор 26 по модулю два, третий сдвиговый регистр 27, блок 28 сравнения сигнатур, сигнатурный анализатор 29. Блок 2 управления содержит вторую кнопку 30, втоЕЮй триггер 31, девятый 32, седьмой 33, четвертый 34, пятый 35, шестой 36, восьмой 37 элементы И, шифратор 38, второй сдвиговый регистр 39, второй 40 и третий 41 элементы И, формирователь 42 одиночных и myльcoв, элемент И-ИЛИ-НЕ 43, дешифратор 44, третий триггер 45, первую кнопку 46. Устройство работает сле,1|уюш.им образом, Под воздействием управляющего сигнала с блока 2 блоки устройства устанавливаются в исходное состояние после чего устройство осуществляет режим контроля. Генератор 3 тестов задает слова контрсэлирующей тестовой последова- . тельности. В каждом из слов, начиная с первого содержится информация о . воздействиях, задаваемых на входы блока 1 и о соответствуккцих выходных реакциях. В нулевом слове содержится информация, определяющая принадлея сность

каждого из выводов блока 1 к входам или выходам.

1 оммутатор 4 в зависимости от информации нулевого слова соединяет разряды генератора 3, содержащие информацию о входных воздействиях, с входами блока 1, а разряда генератора 3, содержащие информацию о выходных реакциях исправного блока 1, с входами блока сравнения 5.

Блок 2 стробирует сраба-павание генератора 3 и ксйдалутатора 4 в нужные моменты времени согласно временной диаграмме работы устройства, обеспечивает тем самым подачу тестов на блок 1.

Блок 5 сравнения сравнивает эталонные логические состояния выходов блока 1, поступающие с коммутатора 4 с реальными, поступающими с выходов блока 1, раздельно по каждому из выходов и выдает по сигналу с блока 2, результат сравнения в сдвиговый регистр 7. В случае несовпадения на одном из .илходов блока 1 в разряд сдвигового .регистра 7, соответствующий данному выходу поступает логическая единица.

Одновременно блок 5 выдает сигнал оценки годности блока 1 на блок.2. В случае получения сигнала Годен с блока 5, блок 2 выдает сигнал годности на индикатор 8, индицируюьий

Годен

транспарант

10001

1

1111 1112 1113

В случае получения сигнала Негоден с блока 5, возникающего при несовпадении эталонной и реальной реакций блока 1, хотя бы в одном разряде, блок 2 сигналом на индикатор В

включает транспорант Негоден

и

переводит устройство в режим диагностики.

Блок 2 выдает управляющий сигнал на вход триггера ГО, переводя его в

0 состояние, при котором выходной уровень этого триггера разрешает прохождение тактовых импульсов с генератора 9 через элемент И 11 на вход счетчика 12 и сдвигового регистра 7. Тактовые импульсы обеспечивают работу

5 счетчика 12 и поразрядную подачу содержимого сдвигового регистра 7 на второй вход триггед а 10. Первая же единица со сдвигового регистра 7 переводит триггер 10 в состояние, при

0 котором выходной уровень триггера 7 блокирует подачу тактовых импульсов через элемент И 11 на счетчик 12 и сдвиговый регистр 7.

В результате, количество подсчи5танных двоично-десятичным счетчиком 12 тактовых импульсов -соответствует номеру первого неисправного вы«. хода блока 1, записанному в двоичнодесятичном коде;

0

Указанный код служит для автоматического поиска диагностической информации в блоке 13. Диагностическая информация в блоке 13 хранится в виде, показанном в табл. 1 и 2.

Таблица,

ш

1У

0000

00

00

5Н97

Таблица2

Я1

1У 00 01

0000 2361 02

542

1119

+8 Информация первого вида (табл.) записывается для каждого из выходов блока 1 и состоит из двух слов, для каждого из выходов блока 1. В первых разрядах первого слова записан номер выхода блока 1. В остальных разрядах - нулевая комбинация Второ слово содержит следующую информацию: в первых разрядах код конструктивного адреса элеме)К1та блока 1, связан ного с выходом, Номер которого записан в первом слове; во вторых разрядах - код номера выходного,вывода этого злемента; в третьих разрядах - нулевой код; в четвед)Тых разрядах - сигнатура (шестнадцатиразряд ная свертка двоичной последовательности) на выходе элемента. Информация второго вида (табл.2) записывается для каждого элемента блока 1 и содержит П4-1 cjfoB (г -количество входов этого элемента). Первое слово содержит в первых разрядах код конструктивного адреса элемента; во вторых - код конструктивно го адреса его выходного вывода; в третьей и четвертой колонках - нуле вой код. Остальные и слов содержат в первых разрядах код конструктивного адреса элемента, связанного с одним из входов элемента, код адреса кото рого хранится в Первом слове; во вторых разрядах -. код номера его вы ходного ил вода; в третьих - код номера входного вывода код адреса которого хранитсй в слове эл мента; в четвертых - сигнатуру для этого последнего вывода. По управляющим сигналам с блока ном выхода из счетчика 12 поступа через мультиплексор 21 в регистр 19 в регистры 14 - 17 пословно в виде, соответствующем табл. 1 и 2 поступа из блока 13 диагностическая информация. Причем номера 1, 11, 111 и 1 колонок табл. 1 и 2 соответствуют номерам 14, 15, 16, 17 регистров, хранящих соответствующую информацию Елок 18 сравнения адреса обеспеч вает сравнение кода выхода, записанного в регистр 19 с кодом, поступающих в регистр 14 и в момент совпадения выдает сигнал о совпаде0(п+1)

1269 НИИ в блок 2. На блок 2 поступает также и информация с регистров 16 и 17, соответствуюшая колонкам 111 и 1У табл. 1 и 2. При наличии Логических нулей в регистрах 16 и 17 и сигнала совпадения от блока 18, блок 2 вырабатывает управляющий сигнал, по которому следующее слово из блока 13 считывается в регистры 14 - 17. В результате на указанных регистрах окажется запи санным второй слово табл. 1. Номед выхода блока 1, записанный в регистр 19 отображается на табло блока 24 индикации. элемента (1111) с регистра 14 и номер его выхода (02) отображается на табло блока 23 индикации. По указанному адресу элемента 111102 устанавливает щуп 25 на блок 1, после чего блок 2 осуществляет повторый пуск тестовой последовательности с узла 6 на блок 1. Снимаемая с выхода выбранного элемента блока 1 двоичная последовательность поступает через щуп 25 на сигнатурный анализатор 29, где после преобразования на сумматоре 26 записывается поразрядно F сдвиговый регистр 27. Сформированная в регистре 27 сигнатура по сигналу с блока 2 сравнивается с эталонной, постуг пающей с регистра 17, блоком 28 сравнения сигнатур. По сигналу совпадения с блока 28 блок 2 выдает сигнал о неисправности соединения между нлходом блока 1 и элементом 1111 на индикатор 8, В случае несовпадения сигнатур блок 2 вырабатывает сигнал, по которому информация из регистров 14 и 15 через мультиплексор 21 и ключевой элемент 22 поступает в регистры адреса 19 и 20 и служит адресом для выборки очередного слова из блока 13. Блок 2 обеспечивает поиск указанного в регистрах 19 и 20 адреса 111102 в блоке 13 с нулевым кодом в четвер тых разрядах (слово 1 табл. 2) и считывание, после обнаружения следую1цего слова в регистры 14 - 17 (слово 2 табл, 2). В результате код конструктивного адреса подозреваемого в отказе злемента 1111 из регистра 19 и номер его входа 01 из регистра 16 поступа ют на блок 24 индикации, а конструк тивный адрес элемента (1112), связа ного с исследуемым, из регистра 14 и номер его выхода (03) и.з регистра 15 поступают на блок 23 индикаци По отображенному на табло блоков 23 и 24 индикации адресу оператор устанавливает щуп 24 сначала на входе подозреваемого в отказе элеме та 1111 01 и снимает сигнатуру. В случает совпадения ее с эталонной блок 2 по сигналу совпадения блока 28 считывает очередное слово из блока 13 в регистры 14 - 17 (слово табл. 2). На табло блоков 23 и 24 индикации высвечивается код номера очередного входа (02) исследуемого элемента, а также код конструктивно го адреса связанного с этим входом элемента (1113) и номер его вывода (01). По указанному адресу оператор ус танавливает щуп 25 и снимает сигнатуру, а в случае совпадения с этало ной снимает описанным способом сигн туры на всех входах исследуемого эл , мента, при появлении нулевого кода четвертых разрядах п+2 слова, описы вающего следующий элемент блока 1. Если сигнатуры на всех п входах совпадают с эталонными, то блок 2 вы дает сообщение о неисправности иссл дуемого элемента на индикатор 8. При несовпадении сигнатур на одном из входов снимается сигнатура на выходе связанного с этим входом элеменI та. Если на входе (01) элемента (1111) сигнатула не совпала с этало . ной, снимается сигнатура с выхода (03) элемента (1112). И если сигнагуры не совпадецот, то блок 2 выдает на индикатор 8 сообщение о неисправности соединения меж,цу входом (01) элемента (1111) и выходом (03) элемента (1112). В противном случае, адрес элемента (1112 ОЗ) переписывается из регистров 14 и 15 по управляющему сигналу с блока 2 через муль типлексор 21 и ключевой элемент 22 в регистры 19 и 20. Затем блок 2 обеспечивает поиск по указанному ajspecy в блоке 13 массива информации описыванвдего соединения элемента 111203 и выборку в регистры 14 - 17 второго слова этого массива. ДгСлее в изложенном выше порядке исследуются вое входы элемента (1112). Блок 2 управления работает следую |щим образом.; Кнопка 4Б служит для нлдачи сигнала, переводящего устройство в исходное состояние. При нажатии кнопки 30 формирователь одиночных импульсов 42 формирует импульс, поступает на комматор 4, регистр 27 и устанавливает триггер 31 в состояние , что обеспечивает прохождение тактовых имч пульсов генератора 9 через открытый элемент И 32 на блок 3. При считывании каждого тестового набора с блока 3 дешифратор 44 формирует сигнал, который -поступает на сдвиговый регистр 27 и через-открытый , мент И 37 на блок 5 сравнения. Перый же сигнал несовпадения, поступающий на R-вход триггера 31 от блока 5 устанавливает его в состоя ние О и блокирует поступление тактовых импульсов.Через элемент И 32 на блок 3. Этот же сигнал поступает на вход шифратора 38, который выдает сигнал о неисправности на индикатор Ви переключает триггер 10 в состояние, разрешающее про- , хождение импульсов через элемент 11. После прохождения последнего тестового набора дешифратор 44 формирует сигнал. Который разроаает сравнение сигнатур, блоком 29 сравнения сигнатур и устанавливает триггер 31 В О . При поступлении блокирующего сигнала с выхода триггера 10 шифратор 38 формирует сигнал, который через открытый элемент И 34 поступает на входы мультиплексора 21. Затем шифратор 38- формирует сигнал сдвига единицы из первого разряда сдвигового регистра 39 во второй. Тактовые импульсы через открытый элемент И-ИЛИ 43 поступают на входы блока 13 памяти. Шифратор 38 при наличии сигналов блока 18 сравнения и элементов 40 и 41, вырабатывающих сигналы при наличии на их входах нулевых кодов, вырабатывает сигнал чтения следующего (второго) слова из блока 13 и затем сигнал, по которому из второго разряда сдвигового регистра 39 переписывается в третий разряд, открывая тем самым элемент И 35, блокируя подачу тактовых импульсов через элемент И-ИЛИ 43 на блок 13. Сигнал совпадения с блока 28 через открытый элемент И 33 поступает на шифратор 38, который алдает сигнал на индикатор 8. При наличии сигнала . несовпадения блока 28 и сигнала элемента 40 щи(й)атор 38 вырабатывает сигнал, который через открытый элемент И 35 обеспечивает перепись содер жимого регистров 14 и 15 в регистра 19 и 20, и сдвигает Ч из третьего разряда сдвигаемого регистра 39 в Четвертый разряд, разешая тем самым подачу тактовых импульсов, через открытый эле« . мент И-ИЛИ 43 на блок 13 памяти. Цри наличии сигнала совпадения с блока 18 и сигнсшов элементов 40

и 41 шифратор 39 формирует сигнал чтения спедуюидаго (второго) слова, который через оккрытый элемент И 36 поступает на блок 13 и пед ееодит из четвертого разряда сдвигового регистра в пятый, открывая тем caNMM элемент И 36 и блокируя подачу тактовых импульсов через элемент И-ИЛИ 43 на блок 13.

По сигналу совпадения сигнатур

на первом вход исследуемого элемента поступаюи ему от блока 28 шифратор 38 вырабаиывает сигнал, который через открытый элемент И 36 считывает из блока 13 следуюпее (второе слово.

фиг,

При несовпадении сигнатур шисй атор 38 вырабатывает сигнал, ко потоиз пятого разряда сдвигорому

вого регистра 39 переходит в третий и цикл работы блока 2 управления повторяется.

Таким образом, введение блоков 7, 13 - 24, 28, 29 и новое выполнение узла 6 позволяет автоматизировать выбор первого неисправного по тесту выхода логического блока, выбор очередной точки для установки шупа, принятие решения о неисправности элемента логического блока 1 или связи между его элементами и выбор пути поиска неисправности, что существенно повышает быстродействие устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для поиска неисправностей в дискретных объектах | 1976 |

|

SU656076A1 |

| G, 06 F 15/46, 1979 (прототип). | |||

Авторы

Даты

1984-02-07—Публикация

1982-04-15—Подача