При работе г 6o,ni,fnn.i iraoop

ропства, т. к. iicirjncciно. клкок отбрасываемая гасть iipoiiJise.iciinH при умножении целого .та иа в ное, разрядпоеть мантнееы резуль-.а меняться в iiee( раз).

При матричных дтетодах умножения труд юетп фор 11 ровання коптролыюго кода отбрасываемой части нропзведсния увс.И читаются, т. к. не все частичные ироизведепня сдвигаются н сдвиг прн этом нроиззоднтся грхннамн разрядов пл;; нозтщии (нолггния - ко;г ;чест о разрядо. на кот.)рое исоблодамо сдвннуть iuiHTHccy, чтобы изменить норядокна единицу), а отбрасываемая часть произиедеНИЯ может кончиться в любой НОЗГ1Н.;Н. Б ЭТНХ

сл чаях контрольные коды резлльтата н отбрасываелгой асти нроизведения можно сформировать линк; иосле пормал гзации рез;/льтата. Для этого необхо. на:юмн ггь вее разряды ироизБСдсння, а онерацпп контроля проводить носле умножения чисел, что значительно увел1 чнваст контрольное оборудованнс н время вынолнеиня всей оиераннн.

Целью данного изобретения являетея HOBF Iшенне бь.1стродейет -ня и иадежност.п работы устройства.

Поставлеггная цель нзобретсиня достигается тем, что в устройстг«) кведе1;Ы б;гокн свертки порядков множимого I: миожитстя и формнровате.П) контрольного кодд порядка, рс зультата, иричем входы блоков п ерткн лорядков множ 1мого н ,:1и явля1г/г(я еедьмым и восьмым вхо.тамн стр01 ст; а, а ; ЛХ071Ь соедниеиы еоответст1.(М1Но с ;-ретьимн входами формирователей контрольных кодов мантиес множимого и множителя н со входами формирователя контрольного кода иорядка результата, третий вход KOTopoiO является девятым входом -етройства. а выход соедннеи с четверты.м входом формирователя когггрольHoio кода результата, пятый вход которого соедииеи со вторым выходо.м блока формирования контрольного кода отбргдсываемой част г произведения, а также тем, что б;(ок формирования коитрольного кода отбрасываемой чаети нроизведения содержнгт зел анализа, узел свертки, коммутатор, рег-нстр свертк :, регистр кода, вычитатель, формирователь . узел управления и фор.1нрова1тель кода граничной но.знцин, нрнчем три входа блока соедииеиы еоответетвенио со входом узла анализа и с первыми входами узла свертки, коммутатора и 3,1а унрасвлеиия, узла аиализа соедннеи со втopы f входом комл1утатора, выход которого соедииен с нервым входом регистра Ko/ia. выход р(1те-т)а кода гс)ед;;неи со вторым входом узла уа)авлек :я. с нервы.; входом форлл1роватс;|5; кода граничной нозиЦ1И1, через ИлЧнтajeл;J е третьнм входом кo тмутатора г: через формирователь маски со вторым входом узла све)тки, иервый выход которого соединен с нервы.м входом pericrpa сверткн. а второй выход --- со вторым входом

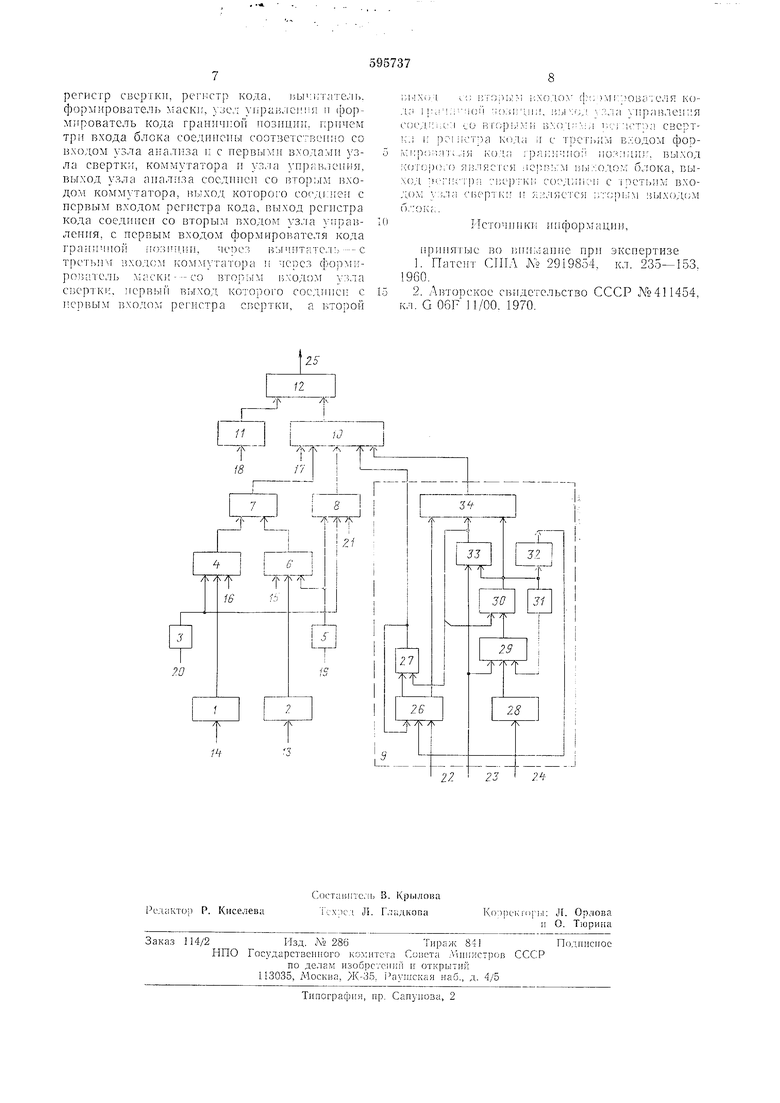

Она со.;ержит ре:-;1ст;)

,. рСМНСТП 1 КОН

. блок П сг;ертк ; : сЬ(.1р.;мроз;;те. I, 4 контро. t) ллкзжнтел :, б:ок 5 сверичп нирядка l;oжндюго, формнровател ; б ко ггрол,исго кода ма Г1ч;есы множнмо-о, блок 7 неремножения контрольиых кодов лгаитнес. формирователь 8 контрольного кода порядка резу.л/гата, блок 9 (ЬормироваГИЯ к()нгро.льиого кода огбрае лпаодой нрон31;сде1;н5:;, форм -ро ;атель 10 контрО:Тьиою кода ата, блок П еверткн результата, схема срависнггя 12, 13-24

кода

анализа, коммутатор 29, регистр читатель 31. формиротиггель 32 33 у равле :Ия, формирователь ного кода г ;:а ичиой .позиции.

Устройство эабо1ает с.ле;Г.то1н;

Через вход 14 на региетр рольный КО.Т множлеля. а региетр 2 i:((: .мого. Блоки 3 Н о рядков еоот15ететвеиио мпожнтедя и миожимоIO. приходянсне ко входам 19 н 20. Д.тя целых п(еел бере-1ея норядок ire,:oro чнела, иоетунающин 10 тем же входам 19, 20. Форл)рователи 4 и 6 дейетвуют одинаково. хаждый из iuix из коитрольного кода своего ог ераида, иост Ч1аюш,его с регистра 1 или 2, вычитает контрольный код иорядка, иостунаюмций с блока 3 или 5 и коитрольиые коды 31-:ака порядка и мантиееы, которые ;остуиают е входа 16 или 15. Вг 1Ч еленные форм грователями 4, G KOirrpo.ibHbie кодтл маитнес множителя и множимого иеремножа отея но М()ду,т1о в блоке 7. Контрольные коды норядков. ностуиаюнне с блоков 3, о в формирователе 8 алгебра1 чеекн екладываютсу: но модулю. Формироватс; Ь 8 складываег нли BBicjiTaer их согласно )0 :1мади, иоетуиаюндей но зхол;у 21 об О1 ерациях над иорядкамн к контро,1ируемо:и ус:тро11етве. По эго- г же входу иоплнает ин(|)ор:-:а 1,ня о иормализа ииь При иорма,тизации рез Л15тата li коитро лп уемо; хчтройетве норядок коррск131руст(У и с(;гл;;сио этОл;у кор|1ект1:р ттся ,ЛзНЬЛ1 код норядка результата в формирователе 8. Блок 9 вырабаiHJBaci контрольный код отбрасываемой части нролзведенпя н всех ее нознцнй.

л 1ладшне разряды частичного нроизведения, иолучеииые i; к(н;гро,Л1руемом етрцистве, ноступают через вход 22 на узел 26, образующий коптро.мьпыс коды no3 :ui:fl, KOTOpi.ie может добаьиГ1 к отбрасываелю11 части произведения одна итерация. Контрольные коды позиций поступают в формирователь 34, для выделения контрольного кода граничной позиции. Кроме того, они в узле 26 сворачиваются вместе с контрольным кодом отбрасываемой части произведете, полученным от предыдущих итераций и заиомненного регистром 27. При этом сворачиваются контрольные коды лишь тех позиций, которые пропускают формирователь маскн 32. Полученный результат запоминается регистром 2/ и участвует в подсуммированин к контрольным кодам нового участка отбрасываемся части произведения, образуемого при последующих итерациях. Формирователь маски 32 определяет, какие позиции относятся к неучитываемой части произведения. Для этого, по входу 24 на узел анализа 28 поступают форматы сомножителей и выдаваемого результата. Узел анализа 28 образует код длины отбрасываемой части произведения путем сложепня форматов сомножителей и вычитания формата выдаваемого результата. Полученный код нропускается коммутатором 29 на регистр кода 30, где и запоминается вначале операцин. Вычитатель 31 уменьшает код на количество нозиций, которое может добавить к отбрасываелюй части нроизведения одна итерация, ноэтому результат вычитания нронускается коммутатором 29 на регистр 30 только носле итераций, увеличивающих отбрасывае.мую часть нроизведения. Как только на регистре 30 окажется код, меньший или равный коду количества позиций, которое добавляет к отбрасываемой части ироизведеиия одна нтерация, узел унравления 33 вырабатывает сигнал, запрещающий последующие приемы (до конца операции) регистрами 27, 30, и результат иа них сохраняется до конца онерацпи. Ио этому же сигпалу формирователь 34 запоминает контро.шный код граничной позиции, иричем помером ее является код, запомиеппый регистром 30. По коду регистра 30 формирователь 34 выбирает из числа принятых контрольных кодов позиций с узла 26 контрольный код грапичпой позиции и выдает его на формирователь 10. По этому же коду формирователь маски 32 вырабатывает сигналы, маскирующие в узле 2о позиции, не относящнеся к отбрасываемой части нроизведения. По входу иоступает сигнал начала операции и сигналы итераций, увеличивающие отбрасываемую часть ироизведения. Этн сигналы узлом управления 33 пропускаются на управляющие входы регистров 27, 30, пока узел 33 не выработает сигнал, запрещающпй последующие ирпемы этими регистрами. При этом иа регистр 27 узел 33 выдает сигналы с задержкой, необходимой для согласовання приема регистра 27 с временем прохождения сигналов через регистр 30, узел 26 и формирователь 32. По входу 17 на формнрователь 10 поступают контрольные коды знаков норядка

и мантиссы рез льтата, пиформацпя о тппе );ыдаБ;1емого результата (целый, веществспиый; и о налнчни нормализацпи. Формирователь 10 складывает но модулю контрольные коды отбрасываемой части произведения, мантиссы рез}льтата и ее знака. Если произведение -- вещественное число, то к результату сложсиия кодов добавляется контрольный код норядка результата и его знака. В случае пормаллзации из нолученного кода вычитается контрольный код граннчной позицни.

ilo входу 18 в блоке 11 поступают разряды нроизведения, где они сворачиваются, а результат сравниваегся в схеме сравнения 12

с контрОьТьным КОДОЛ1, полученным в формирователе 10. В случае их несовнадения, схема сравпеппя 12 вырабатывает сигпал ошибки и выдает его на выход 25.

Формула изобретения

1.Устройство для контроля умноження но модулю, содержащее регнстры контрольных кодов множнлюго и множнтеля, входы которых являются нервым и вторым входами устpoiicTBa, а выходы соединены соответственно с нервыми входами формирователей контрольных кодов мантнсс множимого и множителя, вторые входы которых являются третьим и четвертым входами устройства, а выходы

соединены со входами блока перемножения контрольных кодов мантнсс, выход которого соедннен с первым входом формнрователя контрольного кода результата, второй вход которого является пятым входом устройства,

третий вход соедииен с первым выходом блока формирования контрольного кода отбрасываемой нроизведення, а выход - соединен с нервым входом схемы сравнения, второй вход которой соединен с выходом блока свертки результата, а выход является выходом устройства, вход блока свертки результата является шестым входом }стройства, отл и ч а ю щ е е с я тем, что, с целью иовышения быстродействия и )1адежности работы, в устройстзо введены блоки свертки иорядков множимого и .1я н формирователь контролыюго кода норядка результата, причем входы блоков свертки иорядков множимого и М11ожителя являюгся седьл1ы: 1 и восьмым входа.мн устройства, а выходы соединены соответственно с трстьн:.1И входами фор: 1нрователеГ1

КОиГрОЛЬНЫХ кодов мантисс МНОЖИМ01-О и МИОЖ1гге,1я и со входами формнрователя контрольного кода иорядка результата, третий

вход которого является девятым входом устpoiicTBa, а выход соедннен с четвертым входо.м формирователя контрольного кода рсзультаи, нятын вход которого соедииеи со вторым выходом блока формирования коитрольиого кода оторасываемой части ироизведения.

2. стройс1во jiO и. 1, отличающееся , что олок фор.аировання контро.тьного кода отСрасываемон части нроизведен11я содержит зсл анализа, узел сверткн, коммутатор. регистр свертки, ретистр кода, i;bii:i;T;rre.Ti), формирователь ,таски, y;jc,4 yji)ai-ioTci::i i ii (юрмпроватеоТЬ кода грангппюй позиции, гфпчсм три входа блока соединены соотзетствеиио со вхоЛцОМ узла анализа и с первыми входами узла сверткм, коммутатора и уз,1а упрг:кления, выход узла анализа соедннеп со вторым входом коммутатора, выход которого со(и:ие1 с первым входом регистра кода, втлход регнстра кода соединен со вторым входом уз.та лчтравлеи1гя. с иервым входом формирователя кода граничной позшпи, чепез вычитатель--с третьим входом коммутатора и через формирожггель маскн--со вторым входом узла cnepTKii, нервыи выход которого сосдииси с neiMibiM входом регистра сверткн, а гггорои ;;: 1;т:);)Ь:м i;xoл,C) (1м; )М1::ОБУ;еля кола i (;i озии:;:, .1 - з:;а c(}(.vU:i:e:i вг{;р,п:н вход;,:Л in;; чгт;); евертк.; i; )счист)а кода ii с третьим входом (;3;ri445i кода ;р;и:;;чно: нозлци;. выход :(ото)(),о яв/1яетги :1ерв:::м иылодом блока, выход ЧЧЧстрп risepTKi; соедлигн е ipeTijiiM входом .ла (ч;ертк;; и я ЛлСтся ;rrc;r)i:.ni :5Ых()Д(;м блок;.. Источник1ч информации. 2. Авторское свидетельство СССР .Yo411454, кл. G 06F 11/00, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Устройство для контроля по модулю @ умножения матриц чисел | 1984 |

|

SU1297053A1 |

| Устройство для контроля по модулю умножения комплексных чисел | 1985 |

|

SU1285479A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для контроля по модулю умножения комплексных чисел | 1986 |

|

SU1386997A1 |

| Устройство для временного уплотнения асинхронных каналов | 1977 |

|

SU641669A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для контроля умножения двоичных чисел по модулю три | 1988 |

|

SU1774337A1 |

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

12

Г

J

//

l

Авторы

Даты

1978-02-28—Публикация

1975-12-18—Подача