Три узла 10-13 свертки по модулю три, узел 1А инвертирования по модулю три и первый сумматор 17 по модулю три формируют в каждом такте умножения код свертки по модулю три поразрядных переносов, младшей части произведения и поразрядных сумм, который записывается в третий регистр 3, выходы первого и второго регистров 1, 2 соединены с входами узла 15 умножения по модулю три, выход которого и выход пятого регистра 5 соединены с входами третьего сумматора 19 по модулю три, выход которого соединен с входом пятого регистра 5,

1

Изобретение относится к вычислительной технике и может быть в составе арифметических устройств быстродействующих ЭВМ.

Целью изобретения является повышение достоверности контроля устройства .

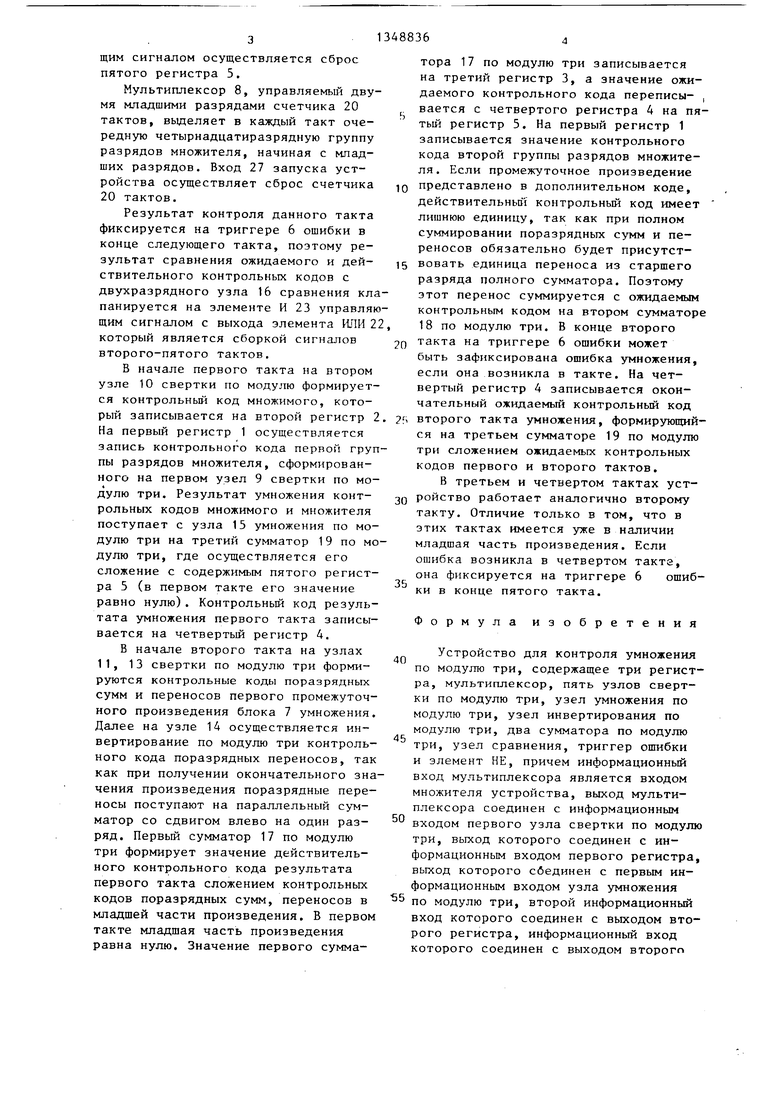

На чертеже приведена функциональная схема устройства.

Схема содержит регистры 1-5, триггер 6 ошибки, блок 7 умножения (не входит в состав устройства) , муль - типлексор В, узлы 9-13 свертки по модулю три, узел 14 инвертирования по модулю три, узел 15 умножения по модулю три, узел 16 сравнения, сумматоры 17-19 по модулю три, счетчик 20 тактов, дешифратор 21, элемент ИЛИ 22, элемент И 23, элемент НЕ 24, входы 25, 26 множителя и множимого устройства, вход 27 запуска и выход 28 ошибки устройства.

Устройство для контроля умножения по модулю три работает следующим образом.

Блок 7 умножения, реализованньп в операционном устройстве как мультиплексор ЕС2665, осуществляет в каждой итерации умножения множимого на очередные четырнадцать разрядов множителя и получение промежуточного произведения на двухрядном виде (поразрядных сумм и переносов). Кроме того, на параллельном сумматоре блока умножения формируется полная сумВыход регистра 5 и вход переноса устройства соединены с соответствующими входами второго суммато1 а 18 по модулю три. Содержимое регистра 3 и сумматора 18 по модулю три сравнивается узлом 16 сравнения, выход которого через элемент НЕ 2А поступает н соответствующий вход элемента И 23, который стробируется сигналом с выхода элемента ИЛИ 22, входы которого соединены с выходами дешифратора 21. Выход элемента И 23 поступает на информационный вход триггера 6 ошибки, выход которого соединен с выходом 28 ошибки устройства. 1 ил.

ма от поразрядных сумм и переносов предыдущей итерации. В конце каждой итерации на соответствующие регистры блока умножения записываются поразрядные суммы и переносы промежуточного произведения и очередные четырнадцать разрядов полной суммы младшей части произведения, сформированные на параллельном сумматоре. Очередное промежуточное произведение получается путем сложения на пирамиде сумматоров поразрядных сумм и переносов, полученных в предыдущей итерации, с результатом умножения данной итерации.

5

0

Рассмотрим работу устройства при 56-ти разрядной мантиссе. При этом операция умножения выполняется за четыре итерации (такта). Все регистры содержат два разряда, так как используются для хранения двухразрядных контрольных кодов. На первый 1, третий 3 и пятый 5 регистры осуществляется запись информации в начале каждого такта, на четвертый регистр 4 и регистр 6 ошибки - в конце каж-. дого такта, второй регистр 2 сохраняет информацию, которая записьшает- ся на него вначале первого такта, до конца операции. Режим хранения организуется клапанированием синхросигнала, поступающего на этот регистр, управляющим сигналом первого такта с 5 дешифратора тактов; этим же управляющим сигналом осуществляется сброс пятого регистра 5.

Мультиплексор 8, управляемый двумя младшими разрядами счетчика 20 тактов, выделяет в каждый такт очередную четырнадцатиразрядную группу разрядов множителя, начиная с младших разрядов. Вход 27 запуска устройства осуществляет сброс счетчика 20 тактов.

Результат контроля данного такта фиксируется на триггере 6 ошибки в конце следующего такта, поэтому результат сравнения ожидаемого и действительного контрольных кодов с двухразрядного узла 16 сравнения кла панируется на элементе И 23 управляющим сигналом с выхода элемента ИЛИ 22 который является сборкой сигналов второго-пятого тактов.

В начале первого такта на втором узле 10 свертки по модулю формируется контрольный код множимого, который записывается на второй регистр 2 На первый регистр 1 осуществляется запись контрольного кода первой группы разрядов множителя, сформированного на первом узел 9 свертки по модулю три. Результат умножения конт- рольньгх кодов множимого и множителя поступает с узла 15 умножения по модулю три на третий сумматор 19 по модулю три, где осуществляется его сложение с содержимым пятого регистра 5 (в первом такте его значение равно нулю). Контрольный код результата умножения первого такта записывается на четвертый регистр 4.

В начале второго такта на узлах 11, 13 свертки по модулю три формируются контрольные коды поразрядных сумм и переносов первого промежуточного произведения блока 7 умножения. Далее на узле 14 осуществляется инвертирование по модулю три контрольного кода поразрядных переносов, так как при получении окончательного значения произведения поразрядные переносы поступают на параллельный сумматор со сдвигом влево на один разряд. Первый сумматор 17 по модулю три формирует значение действительного контрольного кода результата первого такта сложением контрольных кодов поразрядных сумм, переносов в младшей части произведения. В первом такте младшая часть произведения равна нулю. Значение первого сумма

5

0

S

0

5

тора 17 по модулю три записывается на третий регистр 3, а значение ожидаемого контрольного кода переписи- , вается с четвертого регистра 4 на пятый регистр 5. На первый регистр 1 записывается значение контрольного кода второй группы разрядов множителя. Если промежуточное произведение представлено в дополнительном коде, действительньп контрольный код имеет лишнюю единицу, так как при полном суммировании поразрядных сумм и переносов обязательно будет присутствовать единица переноса из старшего разряда полного сумматора. Поэтому этот перенос суммируется с ожидаемым контрольньгм кодом на втором сумматоре 18 по модулю три. В конце второго такта на триггере 6 ошибки может быть зафиксирована ошибка умножения, если она возникла в такте. На четвертый регистр 4 записывается окончательный ожидаемый контрольный код второго такта умножения, формируюпшй- ся на третьем сумматоре 19 по модулю три сложением ожидаемых контрольных кодов первого и второго тактов.

В третьем и четвертом тактах устройство работает аналогично второму такту. Отличие только в том, что в этих тактах имеется уже в наличии младшая часть произведения. Если ошибка возникла в четвертом такта, она фиксируется на триггере 6 ошибки в конце пятого такта.

Формула изобретения

40

45

Устройство для контроля умножения по модулю три, содержащее три регистра, мультиплексор, пять узлов свертки по модулю три, узел умножения по модулю три, узел инвертирования по модулю три, два сумматора по модулю три, узел сравнения, триггер сшибки и элемент НЕ, причем информационный вход мультиплексора является входом множителя устройства, выход мультиплексора соединен с информационным входом первого узла свертки по модул три, выход которого соединен с информационным входом первого регистра выход которого соединен с первым информационным входом узла умножения 5 по модулю три, второй информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом второго

50

узла свертки по модулю три, информационный вход которого является входом множимого устройства, информационный вход третьего узла свертки по модулю три является входом поразрядных сумм устройства, информационный вход четвертого узла свертки по модулю три является входом младшей части произведения устройства, информационный вход пятого узла свертки по модулю три является входом поразрядных переносов устройства, выход пятого узла свертки по модулю три соединен

с информационным входом узла инверти- ,g входом четвертого регистра, выход которого соединен с информационным входом пятого регистра, выход которого соединен с вторым информационным входом третьего сумматора по модулю три и первым информационным вхо- дом второго сумматора по модулю три, второй информационный вход которого является входом переноса устройства, первый выход дешифратора соединен с

рования по модулю три, выход которого и выходы третьего и четвертого узлов свертки по модулю три соединены с соответствующими информационными входам первого сумматора по модулю три, выход которого соединен с информационным входом третьего регистра, выход которого соединен с первым информационным входом узла сравнения.

выход которого соединен с входом эле- 25 тактовым входом второго регистра и

мента НЕ, второй информационный вход узла сравнения соединен с выходом второго сумматора по модулю три, выход триггера ошибки является выходом ошибки устройства, отличающееся тем, что, с целью повьше- ния достоверности контроля, в него введены четвертьш и пятый регистры, счетчик тактов, дешифратор, элемент

30

установочным входом пятого регистра второй, третий, четвертый и пятый выходы дешифратора соединены с соот ветствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом триггера ошибки, выход элемента НЕ соединен с вторым входом элемента И

Редактор Н.Слободяник

Составитель В.Гречнев Техред А.Кравчук

Заказ 4803/49Тираж 670

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ИЛИ, третий сумматор по модулю три, элемент И, причем вход запуска счетчика тактов является входом запуска устройства, информационные выходы двух младших разрядов счетчика тактов соединены с управляющими входами мультиплексора, группа информационных выходов счетчика тактов соединена с группой входов дешифратора, выход узла умножения по модулю три соединен с первым информационным входом третьего сумматора по модулю три, выход которого соединен с информационным

входом четвертого регистра, выход ко

торого соединен с информационным входом пятого регистра, выход которого соединен с вторым информационным входом третьего сумматора по модулю три и первым информационным вхо- дом второго сумматора по модулю три, второй информационный вход которого является входом переноса устройства, первый выход дешифратора соединен с

0

установочным входом пятого регистра, второй, третий, четвертый и пятый выходы дешифратора соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом триггера ошибки, выход элемента НЕ соединен с вторым входом элемента И.

Корректор В.Бутяга Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1975 |

|

SU555401A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Арифметическое устройство цифрового вычислителя для самонастраивающихся систем автоматического управления | 1981 |

|

SU1004973A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе арифметических устройств быстродействующих ЭВМ. Цель изобретения - повышение достоверности контроля. Сигнал по входу 27 запуска устройства устанавливает в исходное состояние счетчик 20 тактов, который начинает считать. Дешифратор 21 управляет записью кода свертки множимого, образованного вторым узлом 10 свертки по модулю три на второй регистр 2. Мультиплексор 8, уп- равляемьй выходом счетчика 20 тактов, пропускает на вход первого узла 9 свертки по модулю три составляющие кода множителя. Код свертки множителя записывается в первый регистр 1. со 4 00 00 со 05

| Устройство для контроля умножения по модулю | 1975 |

|

SU595737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Бетонный полый камень | 1925 |

|

SU2366A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

Авторы

Даты

1987-10-30—Публикация

1986-03-25—Подача