1

Изобретение относится к технике связи и может использоваться в устройствах для устранения временных сдвигов данных, прннимаемых но двум линиям связи.

Известны устройства для регулировання передачи данных.

Однако из известных устройств для регулирования .ачи данных содержит в каждой линии буферные накопители на полный кадр информации н линию задержки цикловых импульсов, выходной сигнал которой считывает данные одиовременно со всех накопителей 1.

Однако использование накопителей с большим объемом памяти приводит к задержке сигнала н усложняет аппаратуру.

Наиболее близким техническим решением к изобретению является устройство для регулирования передачи данных, содержащее генератор сигналов считывания, выход которого через блок буферной задержки считывания подключен к входу первого индикатора резерва памяти и через первый элемент ИЛИ - к входу разрешения сдвига регистра памяти, выход которого подключен к сигнальному входу блока выравниваюшей задержки непосредственно, а к сигнальному входу регистра памяти - через коммутатор записи, иричем вход записи блока выравниваюш,ей задержки соединен с выходом блока буферной

задержки считывания, а вход считывания-с выходом генератора сигналов считывания 2.

Иаиболее сушественным недостатком такого устройства является большая задержка данных, поступающих в намять при регулн юваннп.

Цель изобретения - сокращение времени задержки данных при регулированнн.

Для достнжспня поставленной цепи в устройство для регулирования передачи данных, содержащее генератор снгналов счнтывання, выход которого через блок буферной задержки счнтывания нодключен к входу первого индикатора резерва памяти и через первый элемент ИЛИ - к входу разрешения сдвига регистра памяти, выход которого подключен к сигнальному входу блока выравнНБаюн;ей задержки непосредственно, а к сигнальному входу регистра намяти - через коммутатор запнсн, причем вход записи блока выравннвающей задержки соединен с выходом блока буферной задержкн счнтывания, а вход счнтывания- с выходом генератора сигналов считывания, введены коммутатор линий связи, блок буферной задержки четных кадрон, блок буферной задержки нечетных кадров, триггер коммутации каналов запнсн, элемент И, второй н третий элементы ИЛИ, коммутатор сигнала цнклической перезаписи, индикаТО) конца цикла, коммутатор установлен, второй индикатор резерва памяти и блок циклической перезаписи, при этом выход сигналов записи иачетиых кадров коммутатора липий связи подключсп к первому входу блока буферной задержки нечетных кадров и через торой элемент Р1ЛИ - к второму входу блока буферной задержки четиых кадров, а выход сигналов записи четных кадров коммутатора линий связи подключеи к первому вход блока буферной задержки четпых кадров, выход которого и ВВ1ХОД блока буферной задержки нечетпых кадров соединены с н.ходами блока циклической церсзаписи п с входами триггера коммутации каналов записи, выход которого соединен с управляюн1им входом ксПШутатора сигнала циклической перезаписи, сигнальный вход которого соединен с первым выходом блока циклической псрезапнс 1, а выходы подключены к вторым входам и второго индикаторов резерва памяти, выход сигнала никла коммутатора линии связи соединен с первым установочным г)ходом индикатора конца цикла, выход которого подключен к установочным входам иидиx.iTopa резерва памяти через последовательiio соединенные элемент PI и коммутатор установки, управляющий вход которого соеди;iOf; с соответствующим выходом коммутатора линий , а выходы спгиалов даппых коммутг.тора линий связи подключены к коммутлтогу запис, управляюн1ие входы которого соединены с выходами иидикаторов резерва TPMSiTii, нодключсиными Т1у;-тнй элемент . к третьему управляющему входу коммутатора запиеи и к; другому входу элемента И, выход которого подключен к входу управлегия фазой генератора сигналов считывания, к другому входу которого подключеи второй выход блока циклической перезаписи, нсг-вый выход которого подключен к вторым входам блока буфер; ой задержки считывания, блока буферной задержки нечетных кадров, другому входу второго элемента ИЛИ, к :,торому ВХОД} индикатора конца цикла и к npyiOMy входу первого элемента ИЛИ, а третн выход блока цикличеекой пер-езапиеи сос-дпнеи с Т1)етьими входами блоков буферной зад-ржки четиых и нечетных кадров и блока буфер11ой задержки считывания, четвор-тый ВВ1ХОД блока циклической перезаписи подключен к т)етьему входу иидикатора конца цикла, а вход второго ипдикатора резерва памяти сосдииеп с соответствующим входом icpiioro индикатора резерва памяти.

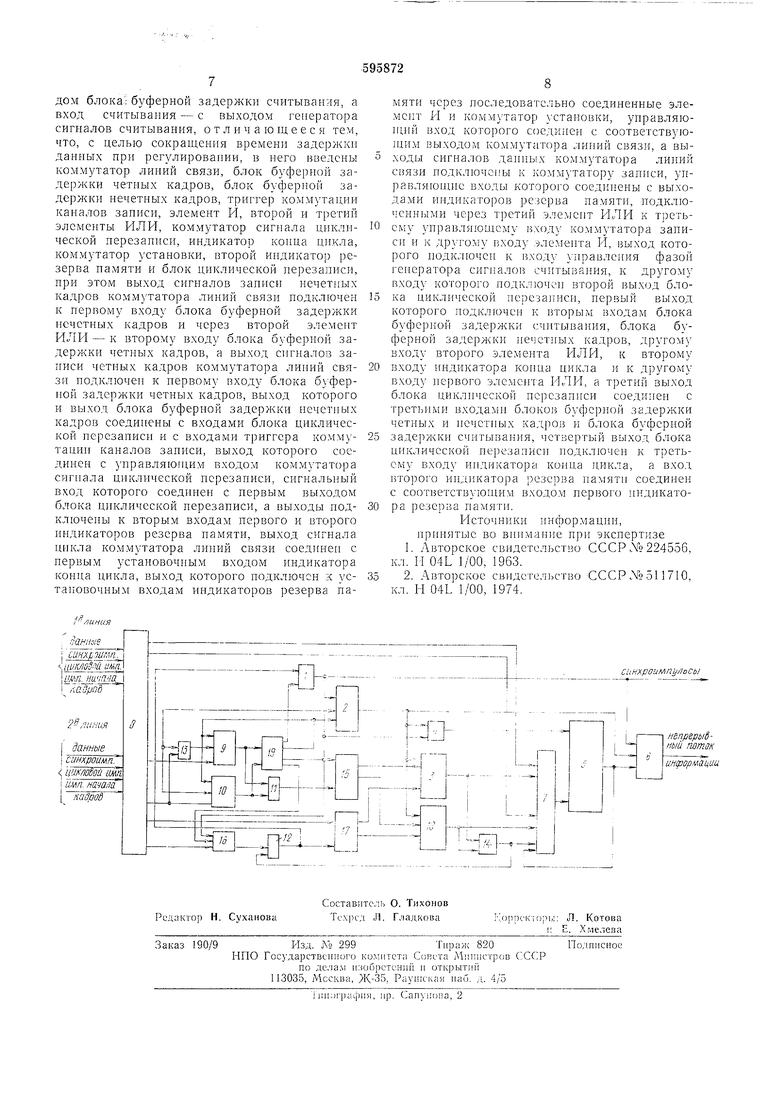

На чертеже приведена ст)уктурпая электрическая схема предложс1и- ого устройства .тля регулирования передачи данных.

Устройство для регулнровапия передачи данных содержит генер;/гор 1 сигиалов счи;Ы1;а/1Ия, выход которого через блок 2 буферной задс|)-:(н считьгзакия подключен к входу первого индикатора 3 резерва памяти и через первый элемент Р1ЛИ 4 - к входу разоещелия двига регистра 5 памяти, вь;ход которого

подключен к еигнальному входу блока 6 выравнивающей задержки нeпocjJeдcтвeинo, а к сигнальному входу регистра 5 памяти - через коммутатор 7 записи, прггчем вход записи блока 6 выравнивающей заде)жки соедииеи с выходом блока 2 буферной задержки считываиия, а вход считывания - с выходом геие)атора 1 сигиалов считывания, коммутатор 8 линий связи, на входы которого ПОСТУпают две группы сигпалов с двух линий связи, блок 9 буферной .задержки четных кадров, блок 10 буферной задсрж;ки печетиьгх кадров, триггер П коммутации каиалов зациси, элемент И 12, второй элемеит PI Л И 13, треяий

элемеит ИЛИ 14, коммутатор 15 сигнала цнклической персзапиеи, индикатор 16 копца цикла, коммутатор 17 установки, второй иидикатор 18 резерва памяти и блок 19 циклической перезаписи, при этом выход енгпалов

записи нечетных кадров коммутатора 8 линий евязи под,ключен к первому входу блока 10 буферпой задержки псчетпых кадров п через второй элемеит ИЛИ 13 - к второ.му входу блока 9 буферпой задержки четных кадров.

му входу блока 9 буферной задержки четных кадров, выход которого и выход блока 10 буферной за.гтержки печетных кадров еоединены

е входами блока 19 никлической пе|)езапнсн и е входами триггер.а 1 ком.тутаг1ии каналов запиеи, 15ыход которого еосдииеп с упоавляюП1,им входом коммутатора 15 сщиала цик.чической перезаписи, сигнальный вход которого

соедннен с первым выходом блока 19 ц 1клической перезапиеи, а выходы подключеиы к вторым входам первого ппдикатора 3 резерва памяти и второго индикатора 18 резерва памяти, выход сигиала цик;1а коммутатора 8 шпий связи соедииеи е первым устаповочпым

входом ипдикатора 16 конца цикла, выход которого подключен к устаповочиым входам первого иидикатора 3 р езерва памяти и второго индикато)а 18 резерва памяти через иоеледовательно соедипепные эле.мент PI 12 н коммутатор 17 устаповилн, унравляюнхий 13ХОД которого соеди)-:еп е соо1ветствуюлнм выходом коммутатора 8 линий связи, а выходы сигналов даппых коммутатора 8 липий

евязи но.тключены к ко.ммутатору 7 , уиравляющие входы которого соедииеиы с выходами первого иидикатора 3 резерва памяти н второго ипдпкатора 18 резерва памяти, подключенными через третий элемсп 14 к

третьему управляющему входу коммутато1)а 7 запиеи и к другому входу элемента И 12, выход которого подключеп к входу управления коррекцией фазы генератора 1 сигналов считывання, к другому входу которого подключей второй выход блока 19 цикличес :ой нерезаииси, нервыii выход которого подключен к второму входу первого элемента 11ЛИ 4 и к вторым входам блока 2 буферпой задерЖки считывания, блока 10 буферной задержки

нечетных кадров и другому входу второго элемента ИЛИ 13, а третий выход блока 19 циклической перезаписи соединен с третьими входами блока 2 буферной задержки считывания, блока 9 буферной задержки четных кадров и блока 10 буферной задержки нечетных кадров, четвертый выход блока 19 циклической перезаписи подключен к третьему входу индикатора 16 конца цикла, а вход второго индикатора резерва памяти соединен с соответствующим входом первого индикатора резерва памяти.

Устройство для регулирования передачи данных работает следующим образом.

На вход устройства с двух линий связи поступают сигналы данных, представляющие собой последовательность кадров длительностью TK, которые могут следовать друг за другом с паузой длительностью не более Гп, когда кадр данных в одной линии оканчивается раньще пли позже, чем начинается кадр в другой линии.

Одновременно на вход коммутатора 8 поступают синхроимпульсы, цикловые импульсы и импульсы начала кадра. На выходе устройства имеется при этом непрерывный поток информации, синфазный с синхроимпульсами.

2Т,

Регистр 5 имеет

разрядов, где т длительность единичного интервала. Входные сигналы данных через коммутаторы 7 и 8 вводятся в регистр Бис помощью генератора 1 считываются на выход устройства «непрерывный поток информации. Считывание данных производится начиная со старщего разряда регистра 5, при этом, если кадры данных не перекрываются, то запись в первых W ячейках всегда отсутствует, а л-W ячеек занято. Занись производится в W-ый разряд, поэтому данные в регистре 5 циклически перезаписываются с его выхода через коммутатор 7 на вход первого разряда. Циклическая перезапись осуществляется в течение интервала , где А - период высокочастотного сигнала тактовой синхронизации, а интервал Гц формируется блоком 19 при поступлении единичного элемента, запись которого в регистр 5 производится в момент, задержанный относительно начала интервала перезаписи па Бремя Wf. Величипа W вычисляется и хранится в индикаторах 3 и 18. Для того чтобы операции считывания и записи не накладывались друг на друга по времени используется блок 2. При этом, если импульс считывания появляется на выходе генератора 1 в момент интервала перезаписи, то он задерживается в блоке 2 до конца интервала на время не более лА. Для компенсации флуктуации момента считывания и получения равномерного сигнала данных между выходом регистра 5 и выходом всего устройства включен блок 6. Для записи данных в регистр 5 одновременно с двух линий при перекрытии кадров используются два канала записи с индикаторами 3 и 18. В момент прпхода первого единичного элемента последуюп1его кадра резерв памяти в индикаторе, соответствующем текущему кадру, составляет We и до конца кадра остается М единичных элементов. Тогда первый едиипчпый элемент последующего кадра записывается в (We-Л)-ую ячейку, а L-ый в (We- -М-L+ 1)-ую ячейку.

Номер ячейки, в которую доллчсн записываться очередной единичпый элемент текущего кадра, хранптся в основном индикаторе 3, а последующего кадра - в пндекаторе 18. Причем величина А выбирается из условия .

Для исключения потерь бита текущего пли

последующего кадра, которому соответствует синхроимпульс записи, приходяп1,ий во время циклической перезаписи по последующему или текущему кадру, с выхода коммутатора 8 указанпый синхроимпульс записи поступает

в блок 19 через блоки 9 и 10. Начальное число в индикатор 18 записывается в соответствии с числом, находящимся в индикаторе 3, и числом еп1,е не принятых бит текущего кадра. Для этого служит индикатор 16.

Переключение каналов записи производится коммутатором 8. Нечетные кадры заппсываются по капалу, включающему в себя коммутатор 8, блок 10, блок 19, индикатор 3 и верхнюю ячейку коммутатора 7. Четные кадры заипсываются по каналу, включающему в себя коммутатор 8, блок 9, блок 19, индикатор 18 и среднюю ячейку коммутатора 7. Подключепие выхода блока 19 к соответствующему индикатору осуществляется

коммутатором 15, управляемым триггером 11, состояние которого зависит от появления сиихроимпульса заппсп на выходе блока 9 пли 10. Выбор дополшггсльпого индикатора резерва памяти, соответств ющего последнему кадру, в который устапавливается начальный сигнал, осуществляется коммутатором 17, управляемым сигналом с выхода коммутатора 8. Выход элемента НЛН -1 подключен к входу регпстра 5, а выход э.юмеита Р-1ЛР1 13 -к входу блока 9. Элемент HЛPi 14 подключен выходом к входу комм татора 7 и входу элемента Н 12.

Такое устройство обеспечивает сокращение времени задержки данных при регулировании

II повыщает надежность путем уменьшения объема пакопителя.

Формула и 3 о б р е т е п п я

Устройство для регулировапия передачи данных, содержаи,ее генератор сигналов считывания, выход которого через блок буферной задержки считывания подключен к входу первого индикатора резерва памяти и через первый элемент НЛН - к входу разрспюпия сднпга регпстра памяти, выход которого подключен к с гп;,л Л10му блока вырапниваюп1,ей задержки пспосредствонпо, а к сигпальпому регпстра памяти -- чсре: коммутатор записи, причем вход заппсп блока выравпиваюпдей задержки соединен с выхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования структуры дискретной информации | 1974 |

|

SU511710A1 |

| Устройство для определения мест повреждения напорного трубопровода | 1988 |

|

SU1681140A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для преобразования Адамара цифровой последовательности | 1987 |

|

SU1462355A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

| Устройство для формирования бинарных телевизионных сигналов | 1991 |

|

SU1818707A1 |

| Телевизионное устройство для формирования двухградационного сигнала графических изображений | 1986 |

|

SU1356260A1 |

| Спектроанализатор | 1979 |

|

SU866494A1 |

| Устройство памяти на телевизионный кадр | 1987 |

|

SU1559430A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

Авторы

Даты

1978-02-28—Публикация

1975-02-03—Подача