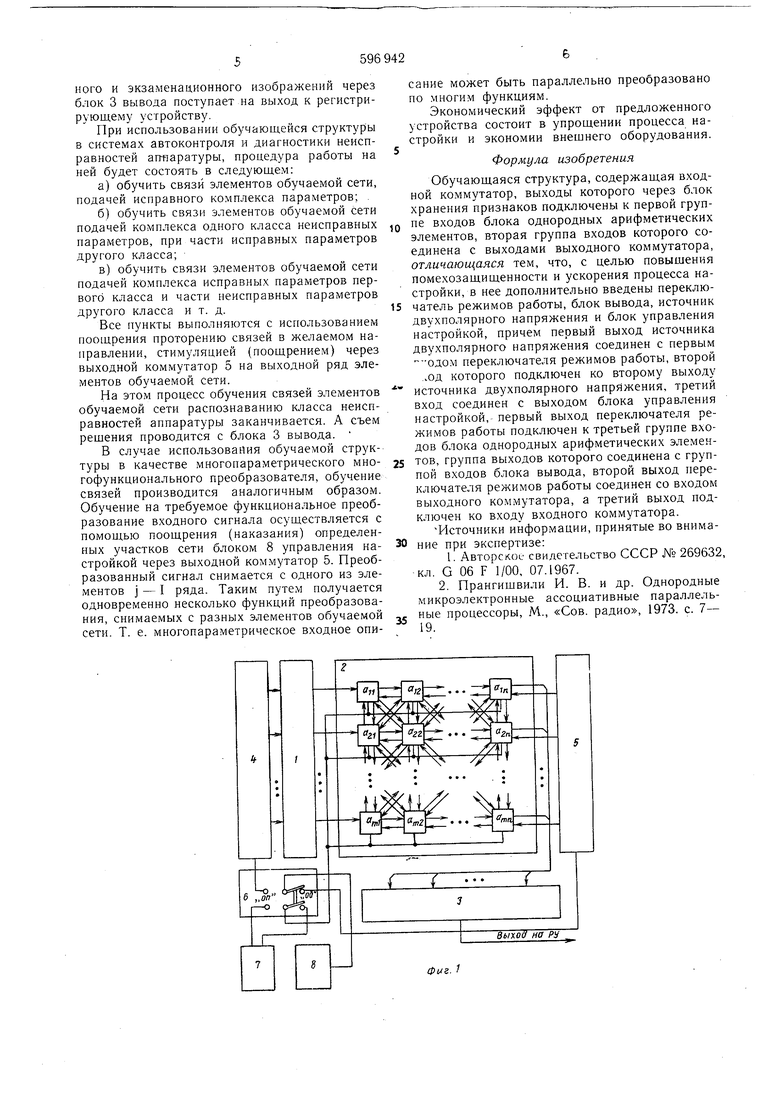

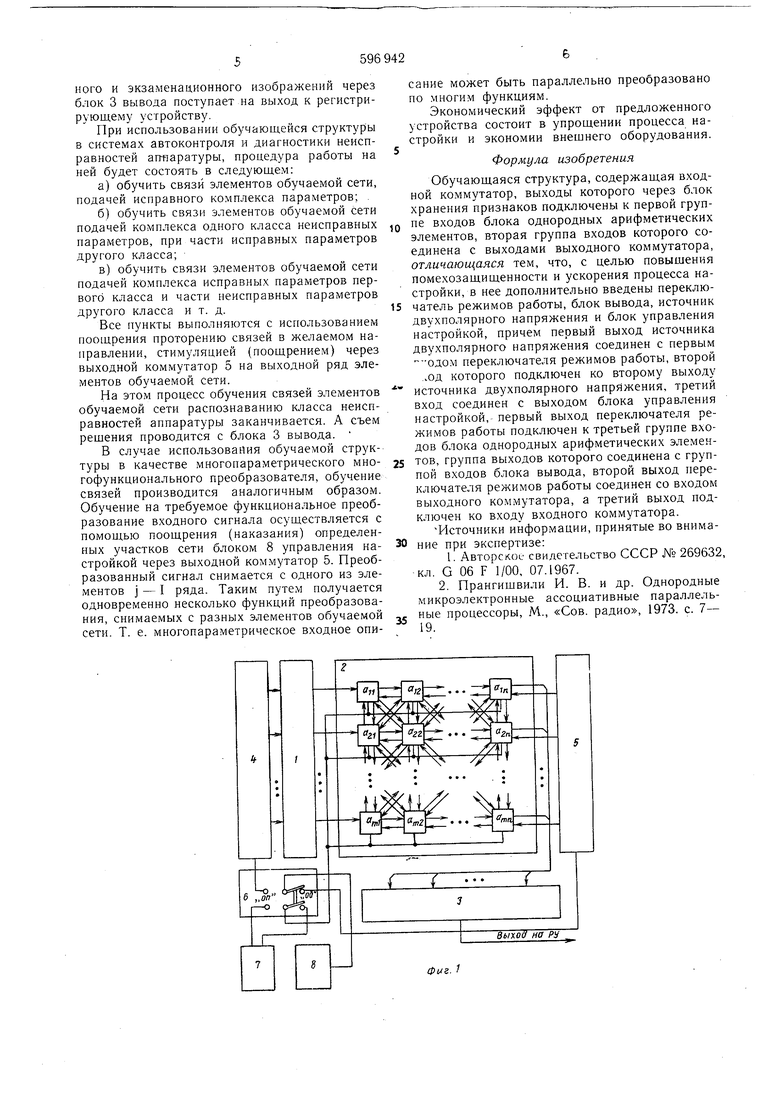

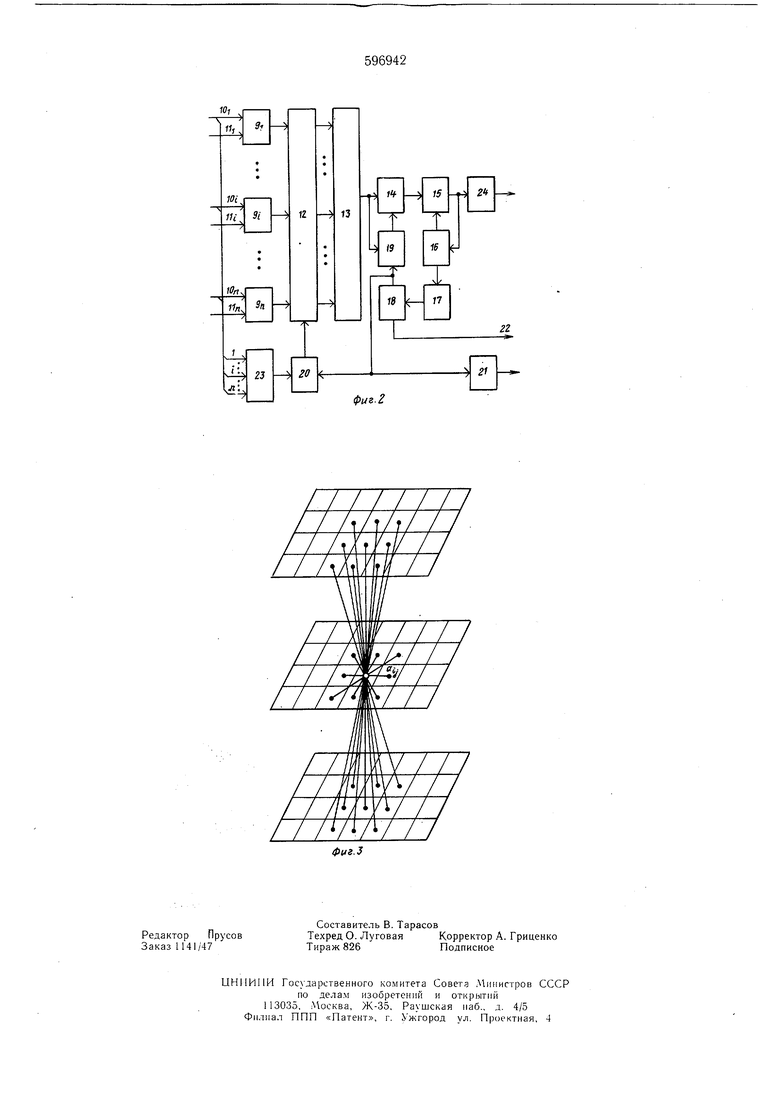

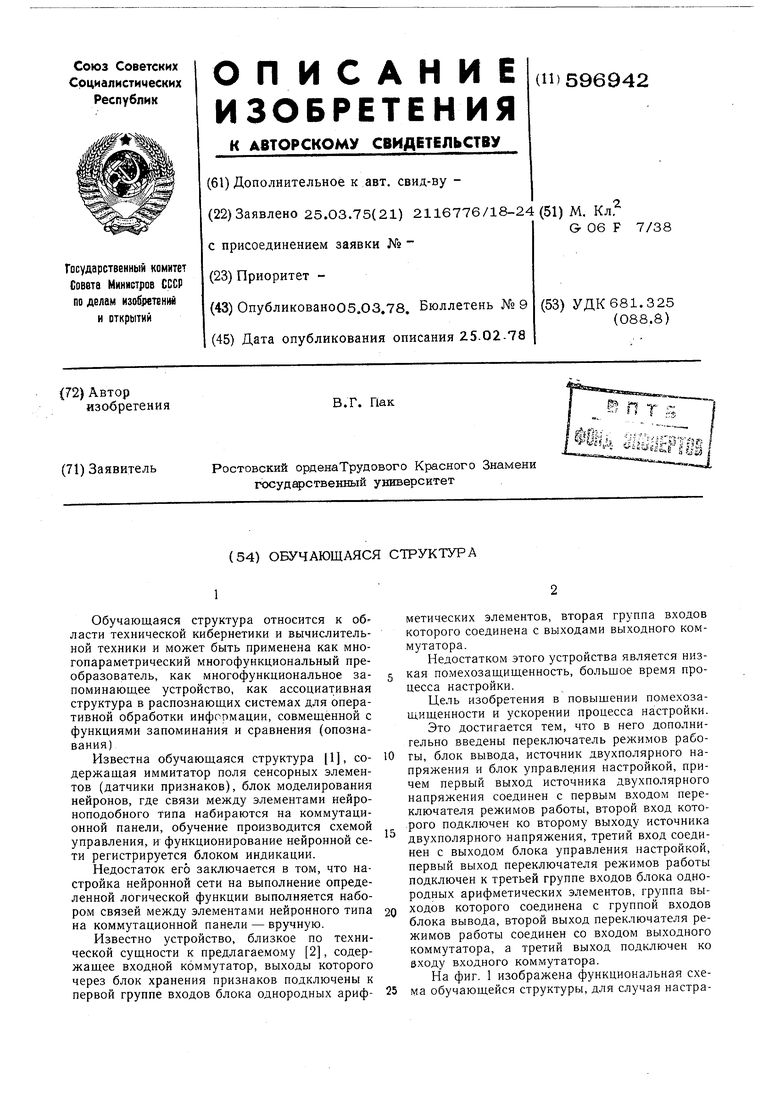

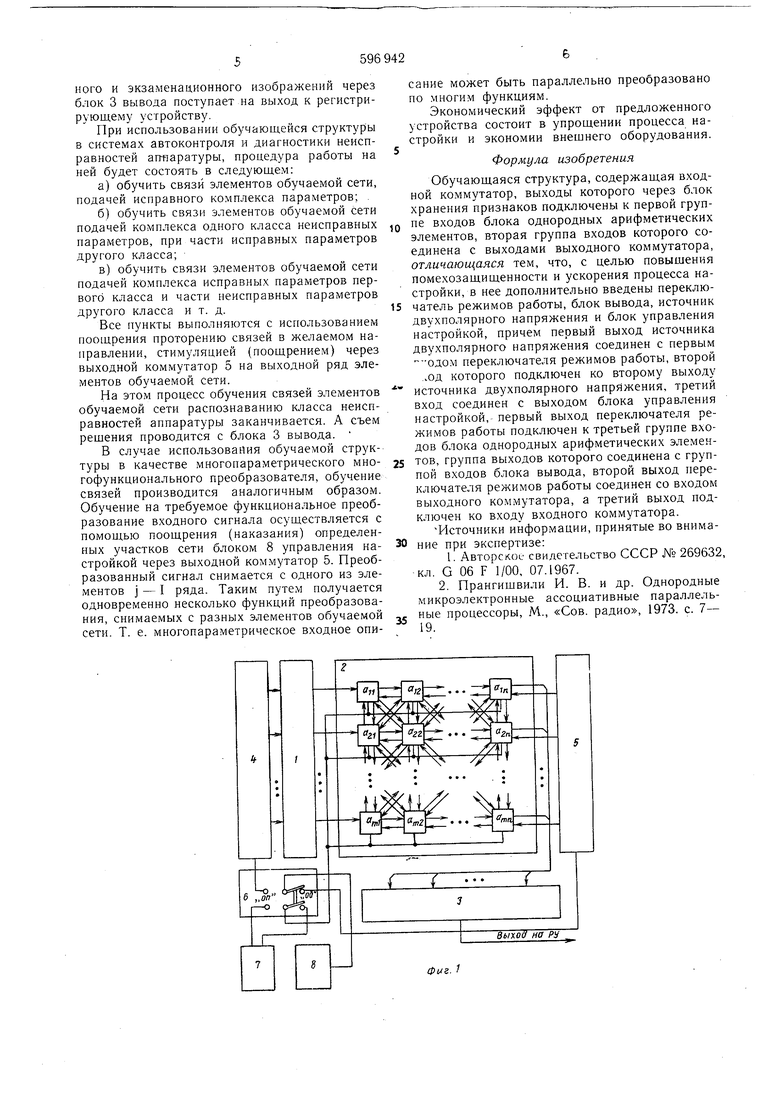

(54) ОБУЧАЮЩАЯСЯ СТРУКТУРА иваемой опознающей структуры; на фиг. 2 - блок-схема элемента; на фиг. 3 - многоэтажный вариант обучающейся структуры с межрядовыми и межэлементными связями. Обучающаяся структура состоит из блока 1 хранения признаков, блока 2 однородных арифметических эле.ментов, блока 3 вывода, входного 4 и выходного 5 коммутаторов, переключателя 6 режимов работы, источника 7 двухполярного напряжения и блока 8 управления настройкой. Блок однородных арифметических элементов состоит из элементов обучаю,цей сети ajj , содержанхих блоки 9у весового умножения на входе с сигнальным входом 0ij и управляющим входом 1 l,j , где i , 2, ..., m; j l, 2, ..., п. Выходы блоков весового умножения 9 через блок 12 выделения каналов с максимальными сигналами соединены со входами сумматора 13. С сумматором 13 соединены последовательно блок 14 сравнения, преобразователь 15 напряжения в частоту, первый и второй интеграторы 16 и 17, блок 18 аналогового запоминающего устройства (АЗУ) и блок 19 управления порогом. Второй вход блока 19 управления порогом подключен к выходу сумматора 13, а выход его - со вторы.м входом блока 14 сравнения. Выход блока АЗУ 18 соединен с усилителем 20 и с блоком 21 управления весом связи, выход которого является аналоговым элемента. Другой вход блока АЗУ 18 соединен с коммутирующей щиной 22, управляемого извне режи.мом «обучение или «опознавание. Выход усилителя 20 соединен со вторым вычитающим входом блока 12 выделения каналов с максимаоТьными сигналами, а вход подключен к выходу дополнительного сумматора 23, входы которого подключены к сигнальным импульсным входам элемента. Работает устройство следующим образом. Рассмотрим работу элемента обучаюп1ейся сети а,, . Входные и.мпульсы с других элементов обучающейся сети поступают на сигнальные входы 10у блоков 9jj весового умножения, а управляющие весовые потенциалы - на аналоговые входы 1 Ijj . В блоке весового умножения происходит детектирование входной последовательности импульсов по интенсивности (частоте) и умножение его огибающей на значение веса связи, поступающего в виде потенциала напряжения на управляющий вход П.-у . Далее продетектированный и помноженный на коэффициент веса связи аналоговый сигнал поступает в блок 12 выделения каналов с максимальными сигналами. С другой стороны входные импульсные последовательности со всех сигнальных в.кодов элемента суммируются в дополнительном сумматоре 23 и через усилитель 20, аналоговое значение напряжения общей интенсивности входного потока импульсов поступает на второй вычитающий вход блока 12 выделения каналов с максимальными сигналами. Выделенные по амплитуде максимальные сигналы поступают далее через сумматор на первые входы блока 14 сравнения и блока 9 управления порогом. Проинтегрированное значение его в блоке 19 управления порогом, с некоторой постоянной времени, поступает на второй вход блока 14 сравнения. Постоянная времени его управляется с блока АЗУ 18. Разностное напряжение с блока 14 сравнения преобразовывается в частоту импульсов и через формирователь 24 стандартных импульсов поступает на сигнальный выход элемента. Во втором интеграторе 17 происходит накопление частоты периодической активации элемента, который с увеличением числа мощных серий импульсации элемента (активности данного элемента в сети), увеличивает заряд, накапливающийся в запоминающе.м устройстве блока АЗУ 18. Соответственно оно увеличивает коэффициент усиления усилителя 20, становится жестче режим выделения каналов с максимальными сигналами. Так происходит обучение элемента, когда по ко.ммутирующей щине 22 поступает потенциал « + Е и блок АЗУ 18 находится в режиме «слежения за входной информацией. В режиме «опознавания, когда по коммутирующей шине 22 поступает потенциал «- Е, блок АЗУ 18 переводится в режим «хранения и на запоминающее устройство не действуют флюктуации напряжения, поступающего со второго интегратора 17. Эта связь выключена. Тогда выходной потенциал памяти, и соответственно, потенциал на аналоговом выходе элемента с блока 21 управления весом связи будет также неизменным. Это соответствует постоянной установке весов связей между эле.ментами сети, настройке среды на решение определеиной вычислительной функции. Процесс обучения обучающейся структуры происходит следующим образом. Переключатель режима работы 6 находится в положении «обучение. При этом выход блока 8 управления настройкой подключен к выходному коммутатору 5, общая коммутирующая щина 22 подключена к. источнику двухполярного напряжения, полюсом « + Ё. Тоглта запоминающие устройства в АЗУ 18 всех элементов обучаемой сети будут находиться в режиме «слежения за входным напряжением, поступающими со вторых интеграторов 17. На первый ряд элементов агг,, обучающейся сети поступают входные сигналы о входном изображении с блока 1 хранения признаков. При N такте показа обучающейся последовательности обучается (изменяется или настраивается вес связей) определенная часть элементов сети на этот образ или формируется цепочка «понятия. ГIpotopeнию путей в желаемом направлении по.могает блок 8 управления настройкой, а участок настройки (поощрения)- выбирается с помощ,ью выходного коммутатора 5 по соответствующей коорди {ате. Это позволяет задать каждому местоположению элемента в сети -«признаки или элементарные поиятия образа. Итак, полное установление конфигурации связей между элементами и будет соответствовать обучению структуры. Пepeключaтev ь 6 режима работы переводится в положение «опознавание и на вход обучаемой сети блока 2 с блока 1 хранения признаков подается экза.менационная последовательность изображения. Результат сравнения запомненного и экзаменационного изображений через блок 3 вывода поступает на выход к регистрирующему устройству.

При использовании обучающейся структуры в системах автоконтроля и диагностики неисправностей аппаратуры, процедура работы на ней будет состоять в следующем:

а)обучить связи элементов обучаемой сети, подачей исправного комплекса параметров; .

б)обучить связи элементов обучаемой сети подачей комплекса одного класса неисправных параметров, при части исправных параметров другого класса;

в)обучить связи элементов обучаемой сети подачей комплекса исправных параметров первого класса и части неисправных параметров другого класса и т. д.

Все пункты выполняются с использованием поощрения проторению связей в желаемом направлении, стимуляцией (поощрением) через выходной коммутатор 5 на выходной ряд элементов обучаемой сети.

На этом процесс обучения связей элементов обучаемой сети распознаванию класса неисправностей аппаратуры заканчивается. А съем решения проводится с блока 3 вывода.

В случае использования обучаемой структуры в качестве многопараметрического многофункционального преобразователя, обучение связей производится аналогичным образом. Обучение на требуемое функциональное преобразование входного сигнала осуществляется с помоц№ю поощрения (наказания) определенных участков сети блоком 8 управления настройкой через выходной коммутатор 5. Преобразованный сигнал снимается с одного из элементов j - I ряда. Таким путем получается одновременно несколько функций преобразования, снимаемых с разных элементов обучаемой сети. Т. е. многопараметрическое входное описание может быть параллельно преобразовано по .многим функциям.

Экономический эффект от предложенного устройства состоит в упрощении процесса настройки и экономии внещнего оборудования.

Формула изобретения

Обучающаяся структура, содержащая входной коммутатор, выходы которого через блок хранения признаков подключены к первой групне входов блока однородных арифметических элементов, вторая группа входов которого соединена с выходами выходного коммутатора, отличающаяся тем, что, с целью повышения помехозащищенности и ускорения процесса настройки, в нее дополнительно введены переключатель режимов работы, блок вывода, источник двухполярного напряжения и блок управления настройкой, причем первый выход источника двухполярного напряжения соединен с первым одом переключателя режимов работы, второй .хОд которого подключен ко второму выходу

источника двухполярного напряжения, третий вход соединен с выходом блока управления настройкой, первый выход переключателя режимов работы подключен к третьей группе входов блока однородных арифметических элементов, группа выходов которого соединена с группой входов блока вывода, второй выход переключателя режимов работы соединен со входом выходного коммутатора, а третий выход подключен ко входу входного коммутатора.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 269632, кл. G 06 F 1/00, 07.1967.

2. Прангищвили И. В. и др. Однородные микроэлектронные ассоциативные параллельные процессоры, М., «Сов. радио, 1973. с. 7- 19.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ГЕОЭЛЕКТРИЧЕСКОЙ РАЗВЕДКИ | 1987 |

|

RU2018884C1 |

| Обучающее устройство | 1984 |

|

SU1249566A1 |

| Устройство для обучения операторов | 1985 |

|

SU1312631A1 |

| Устройство для обучения операторов грузоподъемных машин | 1982 |

|

SU1035635A1 |

| Устройство для сейсмической разведки | 1988 |

|

SU1548759A1 |

| Устройство для группового обучения водителей транспортных средств | 1983 |

|

SU1170487A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Тренажер для обучения водителей транспортных средств | 1985 |

|

SU1257694A1 |

| Тренажер для обучения сварщиков | 1986 |

|

SU1441446A1 |

| Инструментальный способ обучения избирательной нейронной сети без математики и без учителя с использованием самоорганизации | 2019 |

|

RU2729878C2 |

1J /X

«

«

Ц

.

/ / / / / / / / / / A/T/r/ //

LTIi

/

/ / /f dA/ / / / / / /

/ /

TTJ

7

/// /

V ///

VT7

//7

Авторы

Даты

1978-03-05—Публикация

1975-03-25—Подача