1

Изобретение относится к системам передачи дискретных сообпдений и использоваться при работе по спутниковым каналам связи.

Известен цифровой фазовый демодулятор, содержащий последовательно -соединенные задающий генератор, управляемый делитель, неуправляемый делитель, фазовый дискриминатор и блок устранения относительности, причем другой вход фазового дискриминатора соединен с выходом формирователя входного сигнала, а выход подключен к другому входу блока устранения относительности через последовательно соединенные выделитель импульсов подстройки тактовой частоты и формирователь тактовой частоты, на другой вход которого подан сигнал опорной тактовой частоты, при этом второй вход управляемого делителя соединен с выходом блока управления узла подстройки по фазе, третий вход - с другим выходом неуправляемого делителя через носледовательно соединенные формирователь импульсов подстройки опорного напряжения по частоте и реверсивный коммутатор узла подстройки частоты, а второй выход управляемого делителя частоты подключен к носледовательно соединенным фазовому детектору узла нодстройки по фазе и реверсивному счетчику узла подстройки частоты.

2

Однако известное устройство обладает большим временем вхождения в синхронизм по несущей частоте и пониженной устойчивостью демодуляции.

Цель изобретения - повышение устойчивости демодуляции и уменьшение времени вхождения в синхронизм.

Для этого в цифровой фазовый демодулятор введены выделитель нуля несущей, блок управления скоростью подстройки и блок определения качества синхронизации, состоящий из последовательно соединенных дополнительного фазового детектора и порогового блока, нричем выход формирователя входного сигнала подключен к входу выделителя нуля несущей, другой вход которого соединен с дополнительным выходом формирователя тактовой частоты, а выход - к другому входу фазового детектора и входу дополнительного фазового детектора, другой вход которого соединен с дополнительным выходом управляемого делителя, при этом выход порогового блока подключен к первому входу блока управления скоростью подстройки, второй вход которого соедииен с выходом реверсивного счетчика, третий вход - с выходом фазового детектора, а выход подключен к другому входу реверсивного коммутатора и входу блока управлення узла подстройки по фазе.

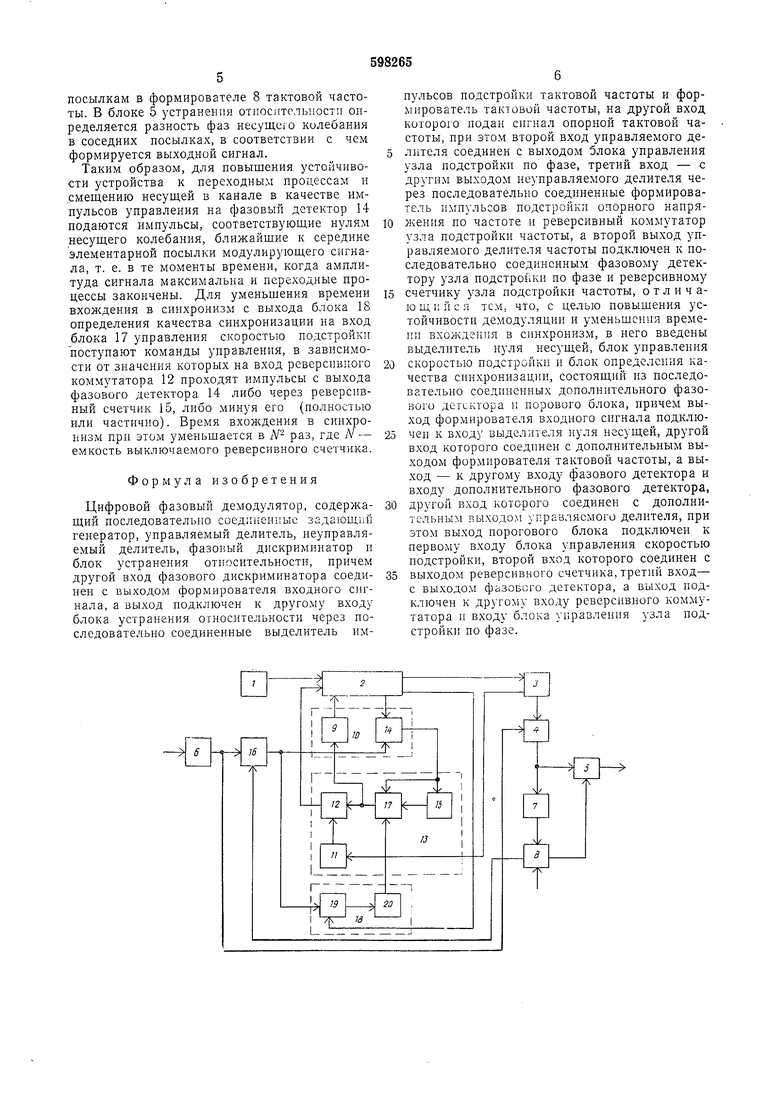

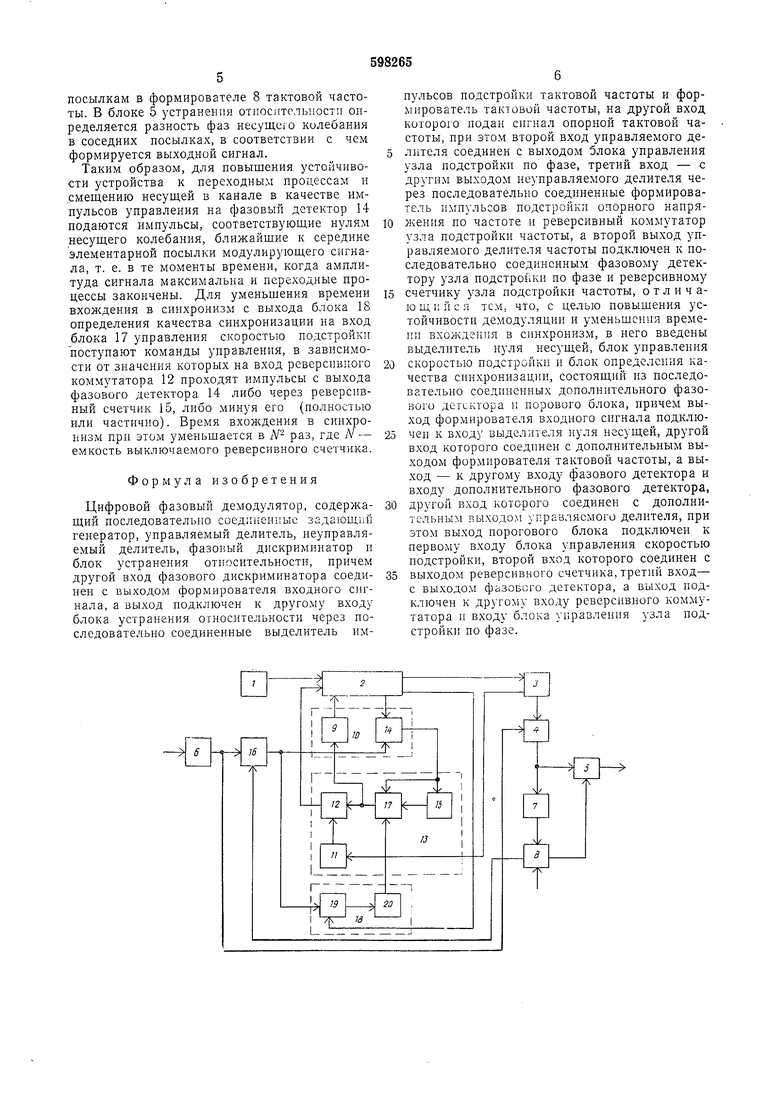

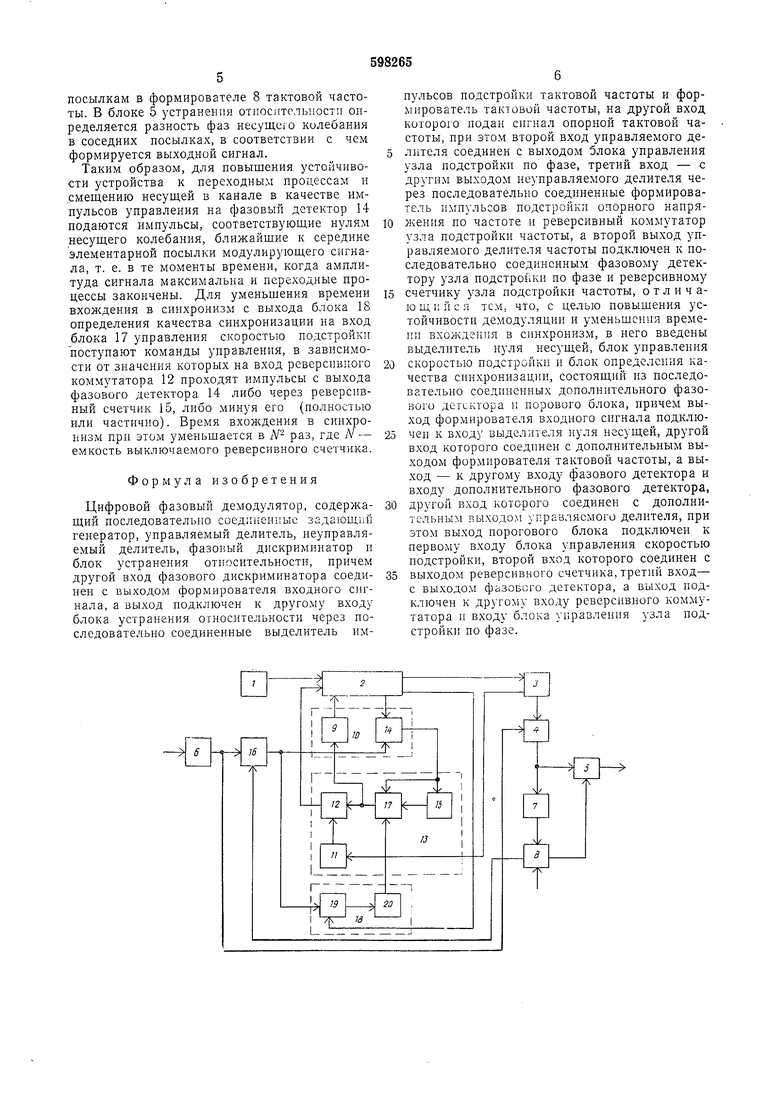

На чертеже приведена структурная электрическая схема цифрового фазового демодулятора.

Цифровой фазовый демодялятор содержит последовательно соединенные задающий генератор 1, управляемый делитель 2, неуправляемый делитель 3, фазовый дискриминатор 4 и блок 5 устранения относительности, нричем другой вход фазового дискриминатора 4 соединен с выходом формирователя 6 входного сигнала, а выход - подключен к другому входу блока 5 устранения относительности через последовательно соединенные выделитель 7 импульсов подстройки тактовой частоты и формирователь 8 тактовой частоты, на другой вход которого подан сигнал опорной тактовой частоты, при этом второй вход управляемого делителя 2 соединен с выходом блока 9 управления узла 10 подстройки по фазе, третий вход - с другим выходом неуправляемого делителя 3 через последовательно соединенные формирователь 11 импульсов подстройки опорного напрял :ения по частоте и реверсивный коммутатор 12 узла 13 подстройки частоты, а второй выход управляемого делителя 2 частоты подключен к последовательно соеди.ненным фазовому детектору 14 узла 10 подстройки по фазе и реверсивному счетчику 15 узла 13 подстройки частоты, выделитель 16 пуля несущей, блок 17 управления скоростью подстройки и блок 18 определения качества синхронизации, состоящий из последовательно соединенных дополнительного фазового детектора 19 и порогового блока 20, причем выход формирователя 6 входного сигнала подключен к входу выделителя 16 нуля несущей, другой вход которого соединен с дополнительным выходом формирователя 8 тактовой частоты, а выход - с другим входом фазового детектора 14 и входом дополнительного фазового детектора 19, другой его вход соединен с дополнительным выходом управляемого делителя 2, при этом выход порогового блока 20 подключен к первому входу блока 17 управления скоростью подстройки, второй вход этого блока соединен с выходом реверсивного счетчика 15, третий вход - с выходом фазового детектора 14, а выход подключен к другому входу реверсивного коммутатора 12 и входу блока 9 управления узла 10 подстройки по фазе.

Устройство работает следующим образом.

На вход формирователя 6 входного сигнала поступает модулированное по фазе несущее колебание, с его выхода импульсы, соответствующие переходам через нуль несущего колебания, поступают па вход выделителя 16 нуля несущей, а на второй вход выделителя 16 подаются импульсы, соответствующие серединам посылок модулирующего колебания со второго выхода формирователя 8 тактовой частоты. Выделитель 16 разрешает прохождение одному импульсу положительного перехода через нуль несущего колебания, ближайшему к середине посылки. На фазовом детекторе 14

фаза несущего колебания в середине посылки сравнивается с фазой опорного напряжения боп частоты /оп 2 -/ыес. ном (где k - кратность манипуляции, /пес. ном - номинальная частота несущего колебания). Импульсы, соответствующие результату сравнения, поступают на реверсивный счетчик 15 и блок 17 управления скоростью подстройки. Подстройка опорного напряжения по фазе производится импульсами, поступающими с выхода блока 17 на управляемый делитель 2 через блок 9 управления. Подстройка опорного напряжения по частоте производится при помощи управляемого делителя 2 импульсами с выхода формирователя 11 через реверсивный коммутатор 12.

Импульс, соответствующий нулю несущего колебания в середине посылки, подается также на дополнительный фазовый детектор 19 блока 18 определения качества сипхронизации, на второй вход которого с выхода управляемого делителя 2 поступает онорпое напряжение Uon. с частотой /ош длительностью импульсов т и смещенное по фазе относительно UOIL- Импульсы, прощедшие через фазовый детектор 19, подаются на вход порогового блока 20, порог которого зависит от длительности импульсов т опорного напряжепия U и количества импульсов, поступающих с дополнительного фазового детектора 19 в единицу

времени. Если это количество превышает заданное число А1, то с выхода порогового блока 20 на вход блока Г/ подается команда, по которой импульсы с выхода фазового детектора 14 поступают па реверсивный ко.ммутатор 12 и блок 9 управления, минуя реверсивный счетчик 15. Скорость вхождения в синхронизм при этом увеличивается в jV- раз, где VV - емкость реверсивного счетчика 15. Как только количество импульсов станет меньше

М, т. е. система вошла в синхронизм, или близка к моменту синхронизма, команда управления меняется на противоположную, и к входам реверсивного коммутатора 12 и блока 9 управления через блок Г/ подключается реверсивный счетчик 15, обеспечивая заданную точность синхронизации.

С выхода управляемого делителя 2 опорное напряжение, подстроенное по фазе и частоте

под несущее колебание, подается на неуправляемый делитель 3.

Неуправляемый делитель 3 формирует сигнал нужной частоты, необходимый для полу.чеиия импульсов подстройки оиорного напря-жения по частоте при помощи формирователя И, а также опорное напряжение для фазового дискриминатора 4.

При помощи фазового дискриминатора 4 определяется абсолютное значение фазы несущего колебания. При помощи выделителя 7 импульсов подстройки тактовой частоты формируется сигнал, соответствующий границам посылок модулирующего колебания (моментам манипуляции), по которому производится

подстройка опорного напряжения t/on. такт, по

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой когерентный демодулятор сигналов относительной фазовой модуляции | 1975 |

|

SU557508A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Цифровой демодулятор сигналов с фазовой манипуляцией | 1983 |

|

SU1124447A1 |

| Цифровой демодулятор сигналов с относительно фазовой модуляцией | 1977 |

|

SU657656A1 |

| Устройство синхронизации с М-последовательностью | 1985 |

|

SU1312750A2 |

| Устройство приема зондирующего сигнала | 1987 |

|

SU1566495A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство асинхронного сопряжения дискретных сигналов | 1974 |

|

SU519871A1 |

| Устройство синхронизации | 1977 |

|

SU658762A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

Авторы

Даты

1978-03-15—Публикация

1976-04-05—Подача