1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретных сообщений с асинхронным вводом информации.

Известно устройство асинхронного сопряжения дискретных сигналов, содержащее в передающей части последовательно соединенные управляемый делитель частоты, подключенный через узел выделения фронтов и фазовый дискриминатор к входу усредняющего узла, и формирователь опорных сигналов, выходы которого соответственно подключены к второму входу фазового дискриминатора, а через первый узел регистрации, соединенный с информационным входом узла выделения фронтов, - к первому входу второго узла регистрации, па второй вход которого подана синхронная тактовая частота, а в приемной части - последовательно соединенные управляемый делитель частоты и формирователь опорных сигналов, выходы которого подключены соответственно через фазовый дискриминатор, соединенный с узлом выделения фронтов, к первому входу управляемого делителя частоты и к входу узла регистрации, второй вход которого соединен с входом узла выделения фронтов.

Однако известное устройство имеет сравнительно большие фазовые флюктуации фронтов посылок принятого сигнала, малую величину допустимой нестабильности тактовой частоты передаваемого сигнала и зависимость этих характеристик от статистических свойств сигнала.

Цель изобретения - повышение помехоустойчивости.

Для этого в передаюшую часть введены формирователь импульсов границ «окна, схема И, запоминающий узел, узел записи и сумматор по модулю два, при этом выход усредняющего узла через последовательно соединенные запоминающий узел и схему И подключен к второму входу управляемого делителя частоты, выход которого через формирователь импульсов границ «окна подключен к первому входу схемы И, выход которой подключен соответственно к второму входу запоминающего узла и через узел записи к одному из входов сумматора по модулю два, другой вход которого соединен с выходом второго узла регистрации, а на третий вход схемы И и второй вход узла записи подана синхронная тактовая частота. В приемную часть введены узел запрета, формирователь зоны нечувствительности, узел определения направления подстройки, пороговый узел, делитель частоты и узел индикации, причем второй выход фазового дискриминатора через узел запрета подключен к другому входу управляемого делителя частоты, выход которого через формирователь зоны нечувствительности подключен к третьему входу фазового дискриминатора, второй выход которого подключен к первому входу узла определения направления подстройки, соединенного вторым входом с первым входом управляемого делителя частоты, а первый выход узла определения направления подстройки через делитель частоты, пороговый узел, соединенный также и с вторым выходом узла определения направления подстройки, и узел индикации подключен к управляющему входу узла запрета, при этом на первый вход узла индикации, третий вход порогового узла и второй вход делителя частоты поданы хронирующие такты.

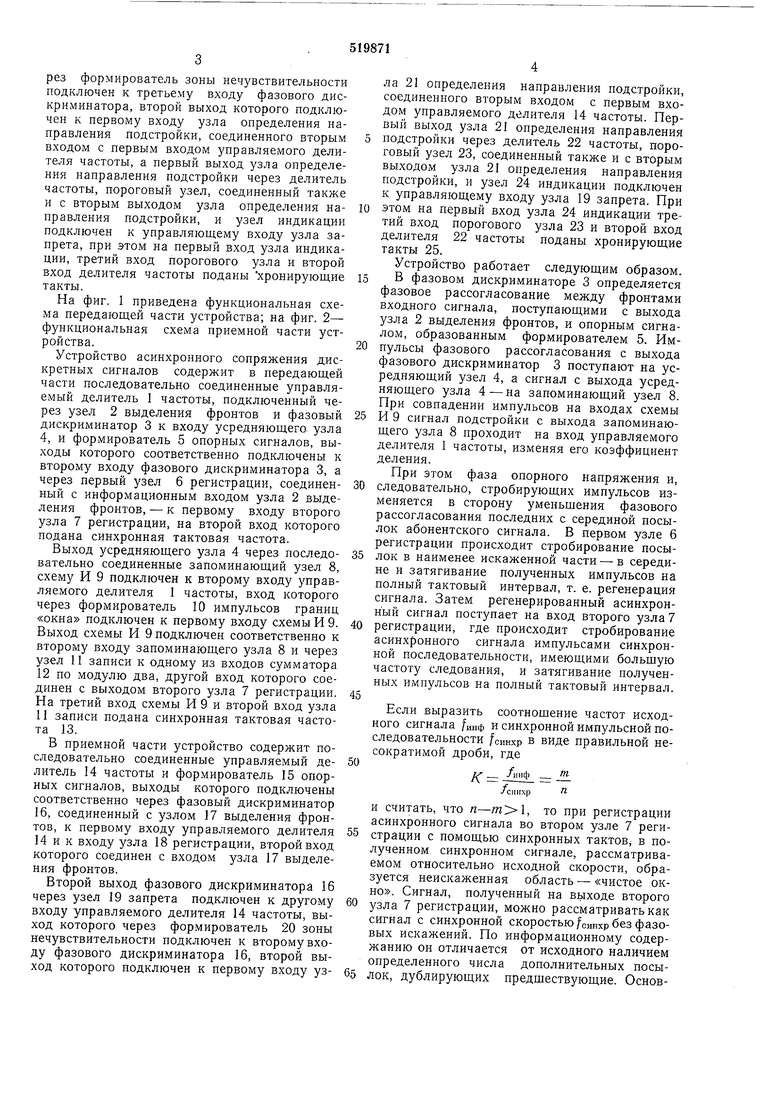

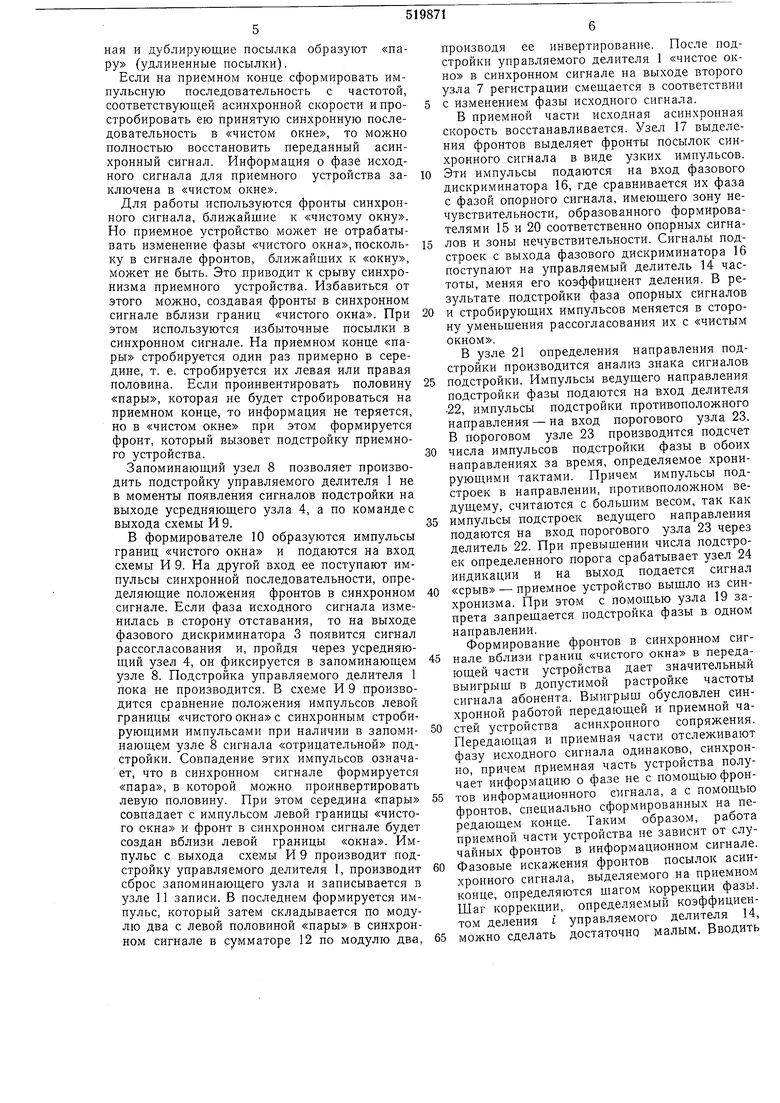

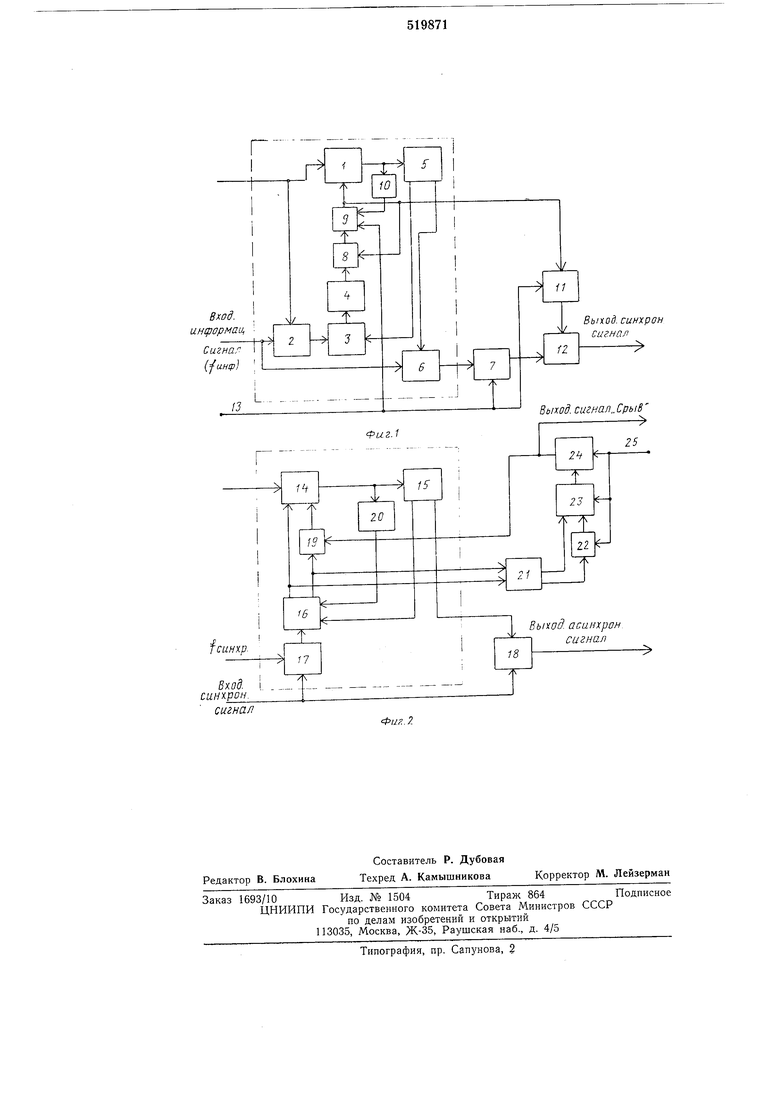

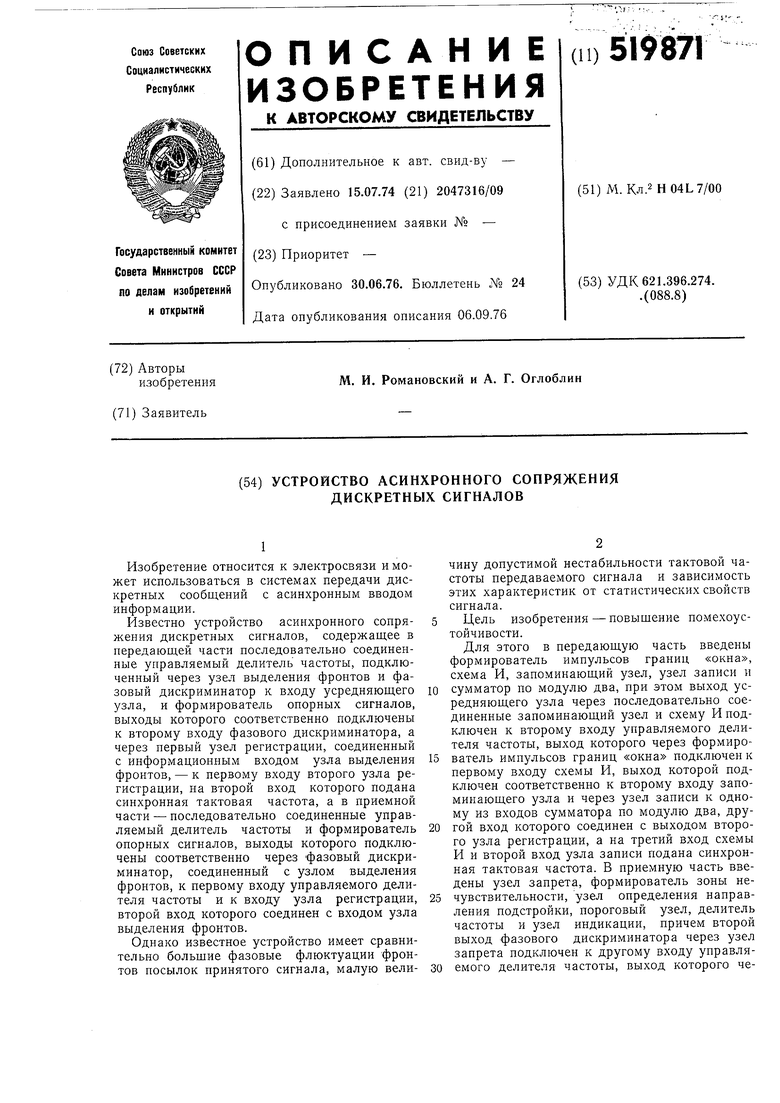

На фиг. 1 приведена функциональная схема передающей части устройства; на фиг. 2- функциональная схема приемной части устройства.

Устройство асинхронного сопряжения дискретных сигналов содержит в передающей части последовательно соединенные управляемый делитель 1 частоты, подключенный через узел 2 выделения фронтов и фазовый дискриминатор 3 к входу усредняющего, узла 4, и формирователь 5 опорных сигналов, выходы которого соответственно подключены к второму входу фазового дискриминатора 3, а через первый узел 6 регистрации, соединенный с информационным входом узла 2 выделения фронтов, - к первому входу второго узла 7 регистрации, на второй вход которого подана синхронная тактовая частота.

Выход усредняющего узла 4 через последовательно соединенные запоминающий узел 8, схему И 9 подключен к второму входу управляемого делителя 1 частоты, вход которого через формирователь 10 импульсов границ «окна подключен к первому входу схемы И 9. Выход схемы И 9 подключен соответственно к второму входу запоминающего узла 8 и через узел 11 записи к одному из входов сумматора 12 по модулю два, другой вход которого соединен с выходом второго узла 7 регистрации. На третий вход схемы И 9 и второй вход узла 11 записи подана синхронная тактовая частота 13.

В приемной части устройство содержит последовательно соединенные управляемый делитель 14 частоты и формирователь 15 опорных сигналов, выходы которого подключены соответственно через фазовый дискриминатор 16, соединенный с узлом 17 выделения фронтов, к первому входу управляемого делителя 14 и к входу узла 18 регистрации, второй вход которого соединен с входом узла 17 выделения фронтов.

Второй выход фазового дискриминатора 16 через узел 19 запрета подключен к другому входу управляемого делителя 14 частоты, выход которого через формирователь 20 зоны нечувствительности подключен к второму входу фазового дискриминатора 16, второй выход которого подключен к первому входу узла 21 определения направления подстройки, соединенного вторым входом с первым входом управляемого делителя 14 частоты. Первый выход узла 21 определения направления

подстройки через делитель 22 частоты, пороговый узел 23, соединенный также и с вторым выходо.м узла 21 определения направления подстройки, и узел 24 индикации подключен к управляющему входу узла 19 запрета. При

этом на первый вход узла 24 индикации третий вход порогового узла 23 и второй вход делителя 22 частоты поданы хронирующие такты 25. Устройство работает следующим образом.

В фазовом дискриминаторе 3 определяется фазовое рассогласование между фронтами входного сигнала, поступающими с выхода узла 2 выделения фронтов, и опорным сигналом, образованным формирователем 5. Импульсы фазового рассогласования с выхода фазового дискриминатор 3 поступают на усредняющий узел 4, а сигнал с выхода усредняющего узла 4 - на запоминающий узел 8. При совпадении импульсов на входах схемы

И 9 сигнал подстройки с выхода запоминающего узла 8 проходит на вход управляемого делителя 1 частоты, изменяя его коэффициент деления.

При этом фаза опорного напряжения и,

следовательно, стробирующих импульсов изменяется в сторону уменьщения фазового рассогласования последних с серединой посылок абонентского сигнала. В первом узле 6 регистрации происходит стробирование посылок в наименее искаженной части - в середине и затягивание полученных импульсов на полный тактовый интервал, т. е. регенерация сигнала. Затем регенерированный асинхронный сигнал поступает на вход второго узла 7

регистрации, где происходит стробирование асинхронного сигнала импульсами синхронной последовательности, имеющими большую частоту следования, и затягивание полученных импульсов на полный тактовый интервал.

Если выразить соотнощение частот исходного сигнала /инф и синхронной импульсной последовательности fcHHxp в виде правильной несократимой дроби, где

(v- /ииф fH

/синхр

и считать, что , то при регистрации асинхронного сигнала во втором узле 7 регистрации с помощью синхронных тактов, в полученном синхронном сигнале, рассматриваемом относительно исходной скорости, образуется неискаженная область - «чистое окно. Сигнал, полученный на вьгходе второго

узла 7 регистрации, можно рассматривать как сигнал с синхронной скоростью/сшхр без фазовых искал ений. По информационному содержанию он отличается от исходного наличием определенного числа дополнительных посылок, дублирующих предшествующие. Основная и дублирующие посылка образуют «пару (удлиненные посылки). Если на приемном конце сформировать импульсную последовательность с частотой, соответствующей асинхронной скорости и простробировать ею принятую синхронную последовательность в «чистом окне, то можно полностью восстановить переданный асинхронный сигнал. Информация о фазе исходного сигнала для приемного устройства заключена в «чистом окне. Для работы используются фронты синхронного сигнала, ближайшие к «чистому окну. Но приемное устройство молсет не отрабатывать изменение фазы «чистого окна, поскольку в сигнале фронтов, ближайших к «окну, может не быть. Это приводит к срыву синхронизма приемного устройства. Избавиться от этого можно, создавая фронты в синхронном сигнале вблизи границ «чистого окна. При этом используются избыточные посылки в синхронном сигнале. На приемном конце «пары стробируется один раз примерно в середине, т. е. стробируется их левая или правая половина. Если проинвентировать половину .пары, которая не будет стробироваться на .у F F приемном конце, то информация не теряется, но в «чистом окне при этом формируется фронт, который вызовет подстройку приемного устройства. Запоминающий узел 8 позволяет производить подстройку управляемого делителя 1 не в моменты появления сигналов подстройки на выходе усредняющего узла 4, а по команде с выхода схемы И 9. В формирователе 10 образуются импульсы границ «чистого окна и подаются на вход схемы И 9. На другой вход ее поступают импульсы синхронной последовательности, опре«ел„к щ.е положения фронтов в синхронном сигнале. Если фаза исходного сигнала изменилась в сторону отставания, то на выходе фазового дискриминатора 3 появится сигнал рассогласования и, пройдя через усредняющий узел 4, он фиксируется в запоминающем узле 8. Подстройка управляемого д елителя 1 пока не производится. В схеме И 9 производится сравнение положения импульсов левой границы «чистого окна с синхронным стробирующими импульсами при наличии в запоминающем узле 8 сигнала «отрицательной подстройки. Совпадение этих импульсов означает, что в синхроппом сигнале формируется «пара, в которой можно проинвертировать левую половину. При этом середина «пары совпадает с импульсом левой границы «чистого окна и фронт в синхронном сигнале будет создан вблизи левой границы «окна. Импульс с выхода схемы И 9 производит подстройку управляемого делителя 1, производит сброс запоминающего узла и записывается в узле 11 записи. В последнем формируется им пульс, который затем складывается по моду лю два с левой половиной «нары в синхрон ном сигнале в сумматоре 12 по модулю два После подроизводя ее инвертирование, тройки уиравляемого делителя 1 «чистое око в синхронном сигнале на выходе второго зла 7 регистрации смещается в соответствии изменением фазы исходного сигнала. В нриемной части исходная асинхронная корость восстанавливается. Узел 17 выделеия фронтов выделяет фронты посылок синронного сигнала в виде узких имнульсов. ти имиульсы подаются на вход фазового искриминатора 16, где сравнивается их фаза с фазой опорного сигнала, имеющего зону нечувствительности, образованного формирователями 15 и 20 соответственно опорных сигна.-.„лов и зоны нечувствительности. Сигналы под JJUB и C5U«I 1 ПСЧ .,. ... , ., строек с выхода фазового дискриминатора 16 поступают на управляемый делитель 14 частоты, меняя его коэффициент деления. В результате подстройки фаза опорных сигналов и стробирующих импульсов меняется в сторону уменьшения рассогласования их с «чистым окном. В узле 21 определения направления подстройки производится анализ знака сигналов -,. ,„„глопп ма п-пг тГ1ГТТХОГ5ТТЛТЛЛС1 подстройки. Импульсы ведущего « правления подстройки фазы подаются на вход делителя 22 импульсы подстройки противоположного направления -на вход порогового узла 23. В пороговом узле 23 производится подсчет числа импульсов подстройки фазы в обоих паправлениях за время, определяемое хронирующими тактами. Причем импульсы подстроек в направлении, противоположном ведущему считаются с больщим весом, так как импульсы подстроек ведущего направления подаются на вход порогового узла 16 через делитель 22. При превышении числа подстроек определенного порога срабатывает узел 24 индикации и на выход подается сигнал ТрГ о77°-ьюу а / ,,,,„ Л, п ПТТНПМ прета запрещается подстройка фазы в одном направлении. Формирование фронтов в синхронном сигнале вблизи сТойсГа а ет зн читеГнь 1 д устимой растройке частоты UU1,-. ..„ ..„, ,..,,.., сигнала абонента. Выигрыш обусловлен синхронной работой передающей и приемной частей устройства асинхронного сопряжения. Передающая и приемная части отслеживают фазу исходного сигнала одинаково, синхронно, причем приемная часть устройства получает информацию о фазе не с помощью фронтов информационного е - гнала, а с помощью фронтов, специально сформированных на передающем конце. Таким образом, работа приемпой части устройства пе зависит от случайных фронтов в информационном сигнале. Фазовые искажения фронтов посылок асинхронного сигнала, выделяемого на приемном конце, определяются шагом коррекции фазы. Шаг коррекции, определяемый коэффициентом деления i управляемого делителя 14, можно сделать достаточно малым. Вводить

расстройку тактовой частоты сигнала относительно ее номинального значения не требуется, так как в приемной части отслеживается фаза в обоих направлениях. Соотношение частот информации /инф и синхронной импульсной последовательности /«гахр

/инф Ш

/синхр

может меняться в очень широких пределах, причем, чем больше разница п-т, тем легче условия работы приемного устройства.

Узел 24 индикации выхода приемной части из синхронизма дает возможность легко контролировать ее исправность и уменьшает время вхождения в синхронизм.

Формула изобретения

Устройство асинхронного сопряжения дискретных сигналов, содержашее в передающей части последовательно соединенные управляемый делитель частоты, подключенный через узел выделения фронтов и фазовый дискриминатор к входу усредняющего узла, и формирователь опорных сигналов, выходы которого соответственно подключены к второму входу фазового дискриминатора, а через первый узел регистрации, соединенный с информационным входом узла выделения фронтов,- к первому входу второго узла регистрации, на второй вход которого подана синхронная тактовая частота, а в приемной части - последовательно соединенные управляемый делитель частоты и формирователь опорных сигналов, выходы которого подключены соответственно через фазовый дискриминатор, соединенный с узлом выделения фронтов, к первому входу управляемого делителя частоты и к входу узла регистрации, второй вход которого соединен с входом узла

выделения фронтов, отличающееся тем, что, с целью повышения помехоустойчивости, в передающую часть введены формирователь импульсов границ «окна, схема И, запоминающий узел, узел записи и сумматор по модулю два, при этом выход усредняющего узла через последовательно соединенные запоминающий узел и схему И подключен к второму входу управляемого делителя частоты, выход

которого через формирователь импульсов границ «окна подключен к первому входу схемы И, выход которой подключен соответственно к второму входу запоминающего узла и через узел записи к одному из входов сумматора по модулю два, второй вход которого соединен с выходом второго узла регистрации, а на третий вход схемы И и второй вход узла записи подана синхронная тактовая частота; в приемную часть введены узел запрета, формирователь зоны нечувствительности, узел определения направления подстройки, пороговый узел, делитель частоты и узел индикации, причем второй выход фазового дискриминатора через узел запрета подключен к

другому входу управляемого делителя частоты, выход которого через формирователь зоны нечувствительности подключен к третьему входу фазового дискриминатора, второй выход которого подключен к первому входу узла определения направления подстройки, соединенного вторым входом с первым входом управляемого делителя частоты, а первый выход узла определения направления подстройки через делитель частоты, пороговый узел,

соединенный также и с вторым выходом узла определения направления подстройки, и узел индикации подключен к управляющему входу узла запрета, при этом на первый вход узла индикации, третий вход порогового узла и

второй вход делителя частоты поданы хронирующие такты.

Фиг.1

Ъьпод. асинхрон сигнал

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство асинхронного сопряжения каналов | 1974 |

|

SU496687A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU882012A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Цифровой фазовый демодулятор | 1976 |

|

SU598265A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СЛУЧАЙНОЙ СОСТАВЛЯЮЩЕЙ НЕРАВНОМЕРНОСТИ ФАЗО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ | 1973 |

|

SU372716A1 |

Авторы

Даты

1976-06-30—Публикация

1974-07-15—Подача